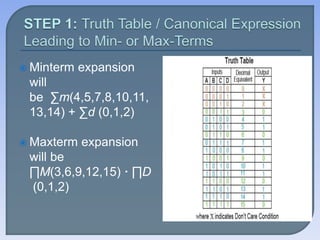

The document explains the difference between analog and digital signals, highlighting that digital signals have two discrete values (high and low), often represented as binary 0 and 1 in various coding systems. It covers binary coding techniques such as BCD, excess-3, and gray code, along with methods for converting between codes and using K-maps for simplifying Boolean expressions. The document further discusses the applications and limitations of these coding systems and provides examples of logical expressions and code representations.

![As the name indicates, the excess-3

represents a decimal number, in binary

form, as a number greater than 3. An

excess-3 code is obtained by adding 3 to a

decimal number.

Valid excess-3 code : 0011 to 1100

Invalid excess-3 code :[0000 to 0010] and

[1101 to 1111]](https://image.slidesharecdn.com/codeconversion-190524080902/85/Code-conversion-9-320.jpg)