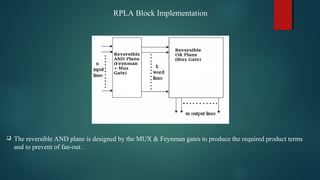

1) The document presents designs for reversible logic gates and their applications in low power circuits. It proposes an improved design for a reversible programmable logic array (RPLA) using multiplexer and Feynman gates that is more efficient than existing designs.

2) It also proposes a method for structuring a reversible arithmetic logic unit (ALU) using reversible logic gates instead of traditional gates, achieving the same functionality with reduced information loss.

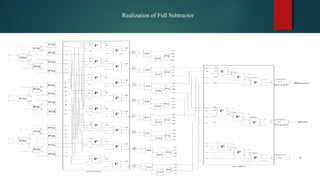

3) The RPLA design is demonstrated by implementing reversible 1-bit full adders and subtractors. Simulation results show the proposed design optimizes the number of reversible gates used.

![COST-EFFECTIVE DESIGN OF REVERSIBLE LOGIC GATES

AND ITS INDUSTRIAL APPLICATIONS

Presented designed by

AMITH BHONSLE

Masters of Technology [ VLSI Design]

VTU,Belgaum.](https://image.slidesharecdn.com/ieeeprojectreversiblelogicgatesbyamit-150207040854-conversion-gate01/85/Ieee-project-reversible-logic-gates-by_amit-1-320.jpg)

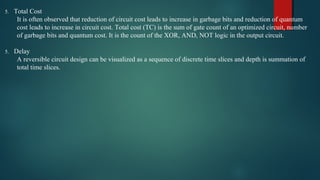

![Quantitative measures of circuit costs

There exist several heuristic algorithms for synthesis of classical reversible circuits and quantum circuits.

1.Gate Count [Circuit cost].

Gate count is the total number of gates in a circuit.

2.Quantum Cost

The quantum cost of a reversible gate is the number of elementary quantum gates needed to implement the

gate. It is the number of reversible gates (1×1 or 2×2) to realize the circuit.

3.Garbage bits

Garbage bits are the additional outputs that makes a function reversible and is not used for further

computations. It is the number of outputs that are not primary. Miller has shown that addition of new working

lines (i.e. essentially additional garbage bits) may be helpful to reduce quantum cost of a circuit.

4.Transistor Cost

The TrC [Transistor Cost] of a circuit is the total number of transistors required to implement the circuit.](https://image.slidesharecdn.com/ieeeprojectreversiblelogicgatesbyamit-150207040854-conversion-gate01/85/Ieee-project-reversible-logic-gates-by_amit-8-320.jpg)

![2. Feynman Gate

2×2 reversible gate called Feynman gate [5]. Feynman gate is also recognized as controlled- not gate

(CNOT). Quantum cost of a Feynman gate is 1.

Feynman gate as a. Not gate b. Data Copier](https://image.slidesharecdn.com/ieeeprojectreversiblelogicgatesbyamit-150207040854-conversion-gate01/85/Ieee-project-reversible-logic-gates-by_amit-11-320.jpg)