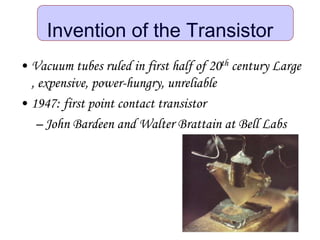

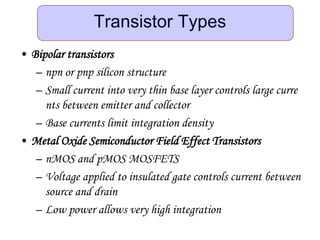

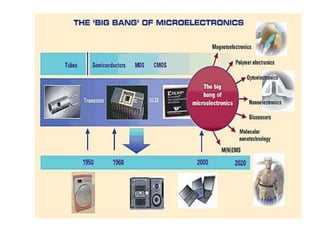

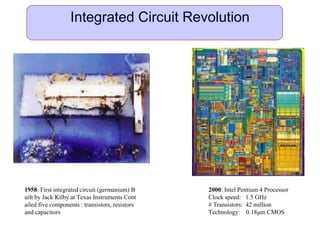

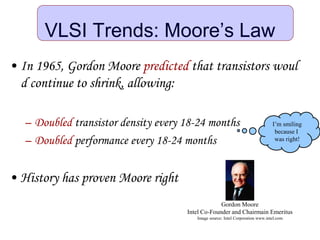

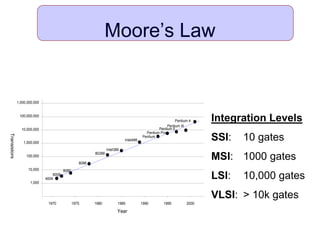

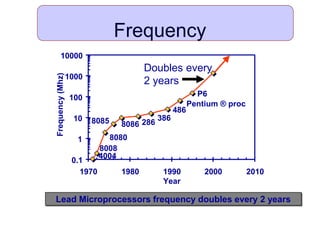

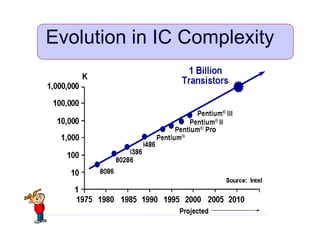

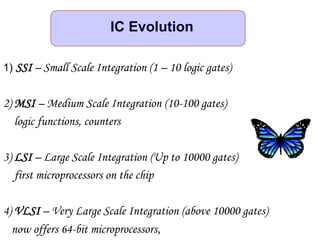

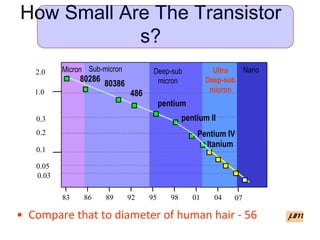

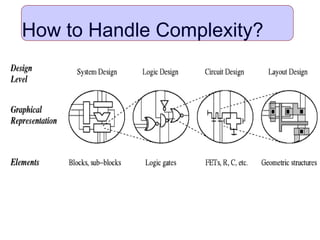

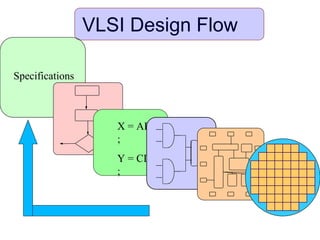

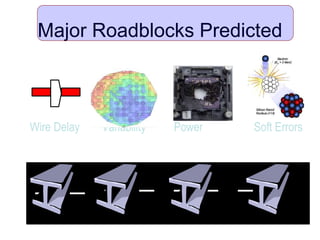

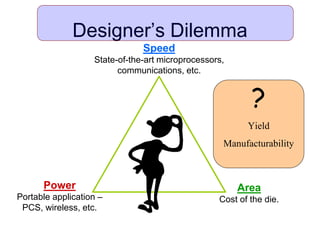

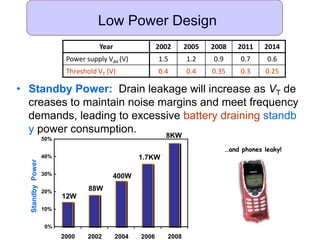

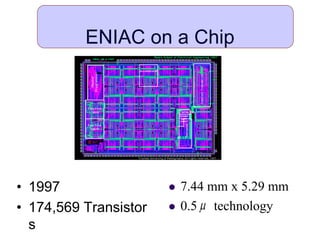

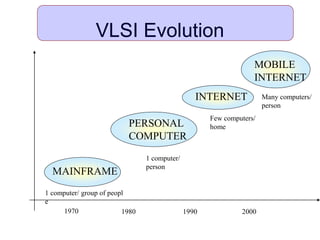

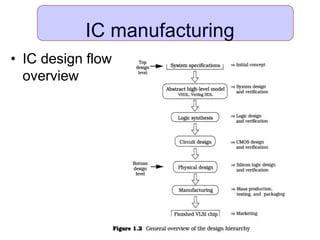

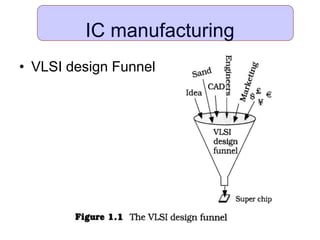

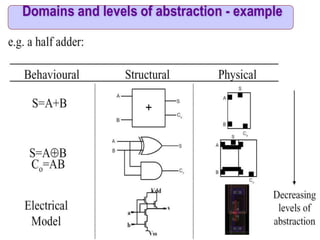

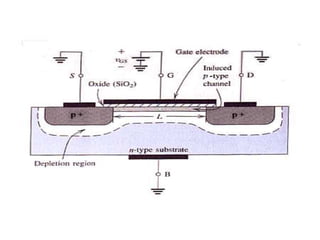

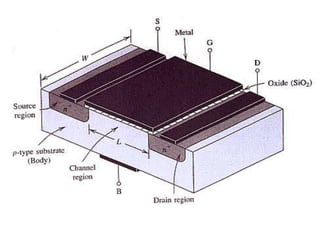

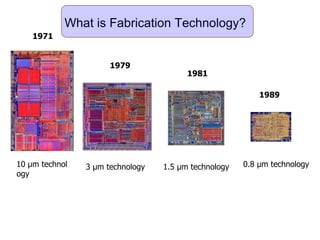

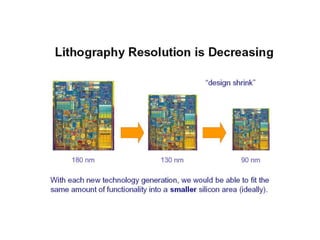

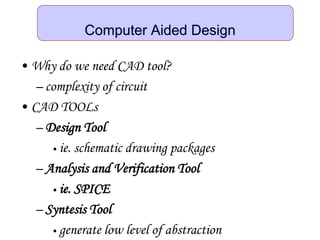

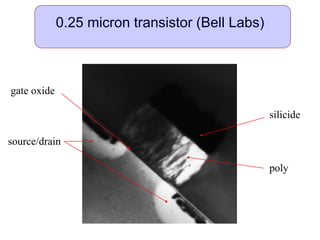

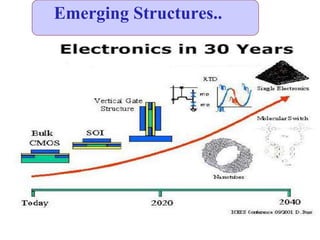

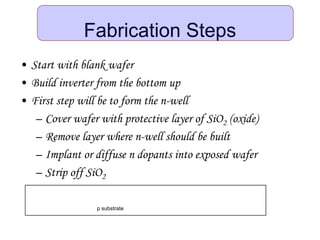

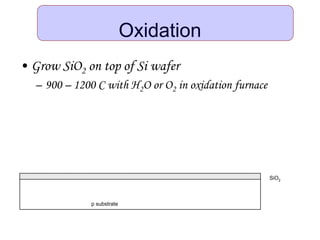

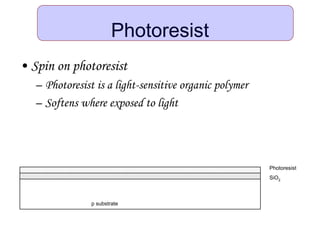

This document provides an overview of VLSI (Very Large Scale Integration) and its applications. It discusses the history of integrated circuits from their inception in the late 1940s to today's advanced nanoscale technologies. Key topics covered include Moore's law of transistor scaling, digital circuit design challenges, CMOS fabrication processes, and examples of how VLSI is used in various electronic systems and devices.