IEEE 2015 Projects for M.Tech & B.Tech VLSI

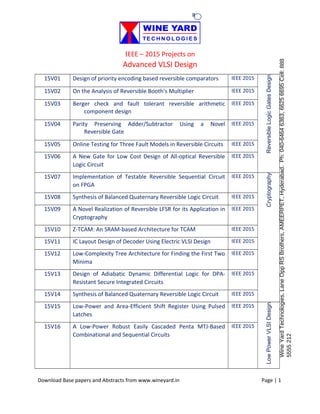

- 1. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 IEEE – 2015 Projects on Advanced VLSI Design 15V01 Design of priority encoding based reversible comparators IEEE 2015 ReversibleLogicGatesDesign 15V02 On the Analysis of Reversible Booth’s Multiplier IEEE 2015 15V03 Berger check and fault tolerant reversible arithmetic component design IEEE 2015 15V04 Parity Preserving Adder/Subtractor Using a Novel Reversible Gate IEEE 2015 15V05 Online Testing for Three Fault Models in Reversible Circuits IEEE 2015 15V06 A New Gate for Low Cost Design of All-optical Reversible Logic Circuit IEEE 2015 15V07 Implementation of Testable Reversible Sequential Circuit on FPGA IEEE 2015 Cryptography 15V08 Synthesis of Balanced Quaternary Reversible Logic Circuit IEEE 2015 15V09 A Novel Realization of Reversible LFSR for its Application in Cryptography IEEE 2015 15V10 Z-TCAM: An SRAM-based Architecture for TCAM IEEE 2015 15V11 IC Layout Design of Decoder Using Electric VLSI Design IEEE 2015 15V12 Low-Complexity Tree Architecture for Finding the First Two Minima IEEE 2015 15V13 Design of Adiabatic Dynamic Differential Logic for DPA- Resistant Secure Integrated Circuits IEEE 2015 15V14 Synthesis of Balanced Quaternary Reversible Logic Circuit IEEE 2015 15V15 Low-Power and Area-Efficient Shift Register Using Pulsed Latches IEEE 2015 LowPowerVLSIDesign 15V16 A Low-Power Robust Easily Cascaded Penta MTJ-Based Combinational and Sequential Circuits IEEE 2015 Download Base papers and Abstracts from www.wineyard.in Page | 1

- 2. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 15V17 A Low-Power Hybrid RO PUF With Improved Thermal Stability for Lightweight Applications IEEE 2015 LowPowerVLSIDesign 15V18 A Low Power and High Sensing Margin Non-Volatile Full Adder Using Racetrack Memory IEEE 2015 15V19 Low power Multiplier Architectures using Vedic Mathematics in 45 nm Technology for High Speed Computing IEEE 2015 15V20 Design & Study of a Low Power High Speed Full Adder Using GDI Multiplexer IEEE 2015 15V21 Design of a Power Optimal Reversible FIR Filter for Speech Signal Processing IEEE 2015 15V22 Low-Power Programmable PRPG With Test Compression Capabilities IEEE 2015 15V23 Design of Low Power and High Speed Carry Select Adder Using Brent Kung Adder IEEE 2015 15V26 Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic IEEE 2015 HighSpeedVLSIDesign 15V27 Design and Analysis of Approximate Compressors for Multiplication IEEE 2015 15V28 Recursive Approach to the Design of a Parallel Self-Timed Adder IEEE 2015 15V29 High-Speed and Energy-Efficient Carry Skip Adder Operating Under a Wide Range of Supply Voltage Levels IEEE 2015 15V30 High-Speed, Modified, Bulk stimulated, Ultra-Low-Voltage, Domino Inverter IEEE 2015 15V31 Implementation of high performance SRAM Cell Using Transmission Gate IEEE 2015 15V32 Energy and Area Efficient Three-Input XOR/XNORs With Systematic Cell Design Methodology IEEE 2015 15V33 Ultralow-Energy Variation-Aware Design: Adder Architecture Study IEEE 2015 Download Base papers and Abstracts from www.wineyard.in Page | 2

- 3. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 AreaEfficientVLSIDesign 15V34 All Optical Implementation of Mach-Zehnder Interferometer based Reversible Sequential Counters IEEE 2015 AreaEfficientVLSIDesign 15V35 Design of Full Adder circuit using Double Gate MOSFET IEEE 2015 15V36 Design of Optimized Reversible Binary and BCD Adders IEEE 2015 15V37 A Single-Ended With Dynamic Feedback Control 8T Subthreshold SRAM Cell IEEE 2015 15V38 Using Boolean Tests to Improve Detection of Transistor Stuck-open Faults in CMOS Digital Logic Circuits IEEE 2015 15V39 Modeling CMOS Gates Using Equivalent Inverters IEEE 2015 15V40 Reducing RMS Noise in CMOS dynamic reconfigurable latched comparator in 50 nm IEEE 2015 15V41 A Linear Comparator-based Fully Digital Delay Element IEEE 2015 15V42 Variable Latency Speculative Han-Carlson Adder IEEE 2015 15V43 Index-based Round-Robin Arbiter for NOC Routers IEEE 2015 NetworkingwithVLSIDesign 15V44 An Improved Dynamic Latch Based Comparator for 8-bit Asynchronous SAR ADC IEEE 2015 15V45 A Novel Ternary Content-Addressable Memory (TCAM) Design Using Reversible Logic IEEE 2015 15V46 A novel design of reversible 2:4 decoder IEEE 2015 15V47 Design and Implementation of a Reversible Central Processing Unit IEEE 2015 15V48 Performance Comparison of Pass Transistor and CMOS IEEE 2015 Download Base papers and Abstracts from www.wineyard.in Page | 3

- 4. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 Logic Configuration based De-Multiplexers 15V49 Quaternary Logic Lookup Table in Standard CMOS IEEE 2015 15V50 Logic Debugging of Arithmetic Circuits IEEE 2015 15V51 Reversible Logic Based Mapping of Quaternary Sequential Circuits Using QGFSOP Expression IEEE 2015 15V52 A 32 BIT MAC Unit Design Using Vedic Multiplier and Reversible Logic Gate IEEE 2015 VLSISignalProcessing 15V53 Towards reversible QCA computers: reversible gates and ALU IEEE 2015 15V54 Design And Development of Efficient Reversible Floating Point Arithmetic unit IEEE 2015 VLSISignalProcessing 15V55 Flexible DSP Accelerator Architecture Exploiting Carry-Save Arithmetic IEEE 2015 15V56 (4 + 2log n)ΔG Parallel Prefix Modulo-(2n − 3) Adder via Double Representation of Residues in [0, 2] IEEE 2015 15V57 Design And Implementation Of Field Programmable Gate Array Based Error Tolerant Adder For Image Processing Application IEEE 2015 15V58 Design and Implementation of Arithmetic Logic Unit (ALU) using Modified Novel Bit Adder in QCA IEEE 2015 15V59 Quantum Cost Realization of New Reversible Gates with Transformation Based Synthesis Technique IEEE 2015 15V60 Design of a Compact Reversible Carry Look-Ahead Adder Using Dynamic Programming IEEE 2015 IEEE 2014 Projects on Advanced VLSI Design WYV62 Design and Estimation of delay, power and area for Parallel IEEE 2014 Are Download Base papers and Abstracts from www.wineyard.in Page | 4

- 5. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 prefix adders aEfficient&LowPower WYV65 Area–Delay–Power Efficient Carry-Select Adder IEEE 2014 WYV68 Approach to design a compact reversible low power binary comparator IEEE 2014 WYV55 A Low Power Fault Tolerant Reversible Decoder Using MOS Transistor IEEE 2014 WYV61 Low power and area efficient carry select adder IEEE 2014 WYV37 Architectural level power optimization techniques for multipliers IEEE 2014 WYV56 Design of high speed hybrid carry select adder IEEE 2014 LessDelay&HighSpeedVLSI WYV57 Optimized Reversible Vedic Multipliers for High Speed Low Power operations IEEE 2014 WYV 2 Radix-8 Booth Encoded modulo multipliers with adoptive delay for high dynamic range Residue Number System. IEEE WYV 4 Design of characterization of parallel pre-fix adders using FPGA. IEEE WYV 7 Reducing the computation time in (short bit-width) two’s complement multipliers. IEEE WYV 9 A new vlsi architecture of parallel Multiplier Accumulator Based On Radix-2 Modified Booth Algorithm IEEE WYV36 The design of high performance barrel integer adder IEEE WYV54 A High Speed Binary Floating Point Multiplier Using Dadda Algorithm IEEE 2014 WYV63 Detection of Hardware Trojan in SEA Using Path Delay IEEE 2014 WYV66 Recursive Approach to the Design of a Parallel Self-Timed Adder IEEE 2014 WYV 8 FPGA Implementation of Scalable Encryption Algorithm. IEEE Datahiding WYV15 FPGA implementation of SHA-1 algorithm IEEE WYV12 Implementation of the hummingbird cryptographic Algorithm IEEE WYV35 Cyclic redundancy check generation using multiple lookup table algorithms IEEE WYV1 An on-chip AHB bus tracer with real time compression and dynamic multi-resolution supports for SOC IEEE Download Base papers and Abstracts from www.wineyard.in Page | 5

- 6. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 CommunicationSystems WYV 5 Self-immunity technique to improve register file integrity against soft errors. IEEE WYV 6 Design and simulation of UART serial communication module based on VHDL. IEEE WYV11 Hardware implementation of RFID Mutual Authentication Protocol. IEEE WYV13 Verilog modeling of WI-FI MAC Layer for Transmitter IEEE CommunicationSystems WYV14 FPGA implementation of USB transceiver macro cell interface with usb2.0 specifications IEEE WYV17 VHDL implementation of lossless data compression. IEEE WYV18 A vliw vector media compressor with cascaded SIMD ALU’S. IEEE WYV21 Design and implementation of blue tooth security using VHDL. IEEE WYV48 Design and implementation of APB bridge based on AMBA 4.0 IEEE WYV50 Applying CDMA technique to network-on-chip IEEE 2014 WYV22 Implementation of vending machine controller IEEE Realtimeapplications WYV23 Implementation of Traffic Light Controller IEEE WYV24 Implementation of Digital Clock IEEE WYV25 Implementation of Electronic Voting Machine controller IEEE WYV26 Implementation of Universal Asynchronous receiver/Transmitter IEEE WYV27 Implementation of Serial Peripheral Interface IEEE WYV28 Implementation of Content Addressable Memory IEEE WYV29 Implementation of 32 bit Cyclic Redundancy Check IEEE WYV30 Implementation of Barrel Shifter IEEE WYV31 Implementation of Round Robin Arbiter IEEE WYV34 Finite state machine based vending machine controller with auto-billing features IEEE Download Base papers and Abstracts from www.wineyard.in Page | 6

- 7. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 WYV 3 High throughput DA-Based DCT with high accuracy Error Compensated Adder Tree. IEEE Digitalsignalprocessingapplications WYV64 parallel multiplier accumulator Based on radix-2 Modified Booth Algorithm by using a VLSI architecture IEEE 2014 WYV10 LUT Optimization for Memory-Based Computation. IEEE WYV33 Optimized implementation of FFT processor for OFDM systems IEEE WYV39 Arithmetic & logic unit (ALU) design using reversible control unit IEEE Digitalsignalprocessingapplications WYV38 Design and minimization of reversible circuits for a data acquisition and storage system IEEE WYV41 Design & implementation of MAC unit using reversible logic IEEE WYV44 An efficient implementation of floating point multiplier IEEE WYV49 A table-based algorithm for pipelined CRC calculation IEEE WYV69 Parity Preserving Logic based Fault Tolerant Reversible ALU IEEE 2014 WYV32 A novel analysis of sequential circuits design using reversible logic gates IEEE ReversibleLogicGatesbasedimplementations WYV40 A distinguish between reversible and conventional logic gates IEEE WYV42 Modified toffoli gate and its applications in designing components of reversible arithmetic and logic unit IEEE WYV43 A new reversible design of BCD adder IEEE WYV45 Fault tolerant variable block carry skip logic (VBCSL) using parity preserving IEEE WYV46 Design of a nano metric reversible 4-bit binary counter with parallel load IEEE WYV47 Introduction to reversible logic gates & its application IEEE WYV51 Realization of 2:4 reversible decoder and its applications IEEE 2014 WYV52 All Optical Reversible Multiplexer Design using Mach-Zehnder interferometer IEEE 2014 Download Base papers and Abstracts from www.wineyard.in Page | 7

- 8. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 WYV53 Design of Dedicated Reversible Quantum Circuitry for Square Computation IEEE 2014 WYV58 Energy Efficient Code Converters using Reversible Logic Gates IEEE 2014 WYV59 Design of Low Logical Cost Conservative Reversible Adders using Novel PCTG IEEE 2014 WYV60 Contemplation of Synchronous Gray Code Counter and its Variants using Reversible Logic Gates IEEE 2014 WYV67 An Optimized Design of Binary Comparator Circuit in Quantum Computing IEEE 2014 WYV70 ASIC Design of Reversible Multiplier Circuit IEEE 2014 WYV71 A Low Energy and High Performance DM^2 Adder IEEE 2014 Lowpower,LowVoltage&Highspeed WYV72 Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator IEEE 2014 WYV73 Low Power Pulse Triggered Flip-Flop Design based on Signal Feed-Through Scheme IEEE 2014 WYV74 Increase in Read Noise Margin of Single-Bit-Line SRAM Using Adiabatic Change of Word Line Voltage IEEE 2014 WYV75 An 8T Low-Voltage and Low-Leakage Half-Selection Disturb- Free SRAM Using Bulk-CMOS and FinFETs IEEE 2014 WYV76 Low Power Noise Tolerant Domino 1-Bit Full Adder IEEE 2014 WYV77 A Novel Low Leakage and High Density 5T CMOS SRAM Cell in 45nm Technology IEEE 2014 WYV78 A New Design of Low Power High Speed Hybrid CMOS Full Adder IEEE 2014 WYV79 A Novel High Speed 4 bit carry generator with a new structure for arithmetic operations IEEE 2014 Lowpower,LowVoltage&Highspeed WYV80 A Sub-threshold Eight Transistor (8T) SRAM Cell Design for Stability Improvement IEEE 2014 WYV81 An Arithmetic and Logic Unit Optimized for Area and power IEEE 2014 Download Base papers and Abstracts from www.wineyard.in Page | 8

- 9. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 Download Base papers and Abstracts from www.wineyard.in Page | 9

- 10. R WineYardTechnologies,LaneOppRSBrothers,AMEERPET,Hyderabad.Ph:040-64646363,66256695Cell:888 5555212 Download Base papers and Abstracts from www.wineyard.in Page | 9