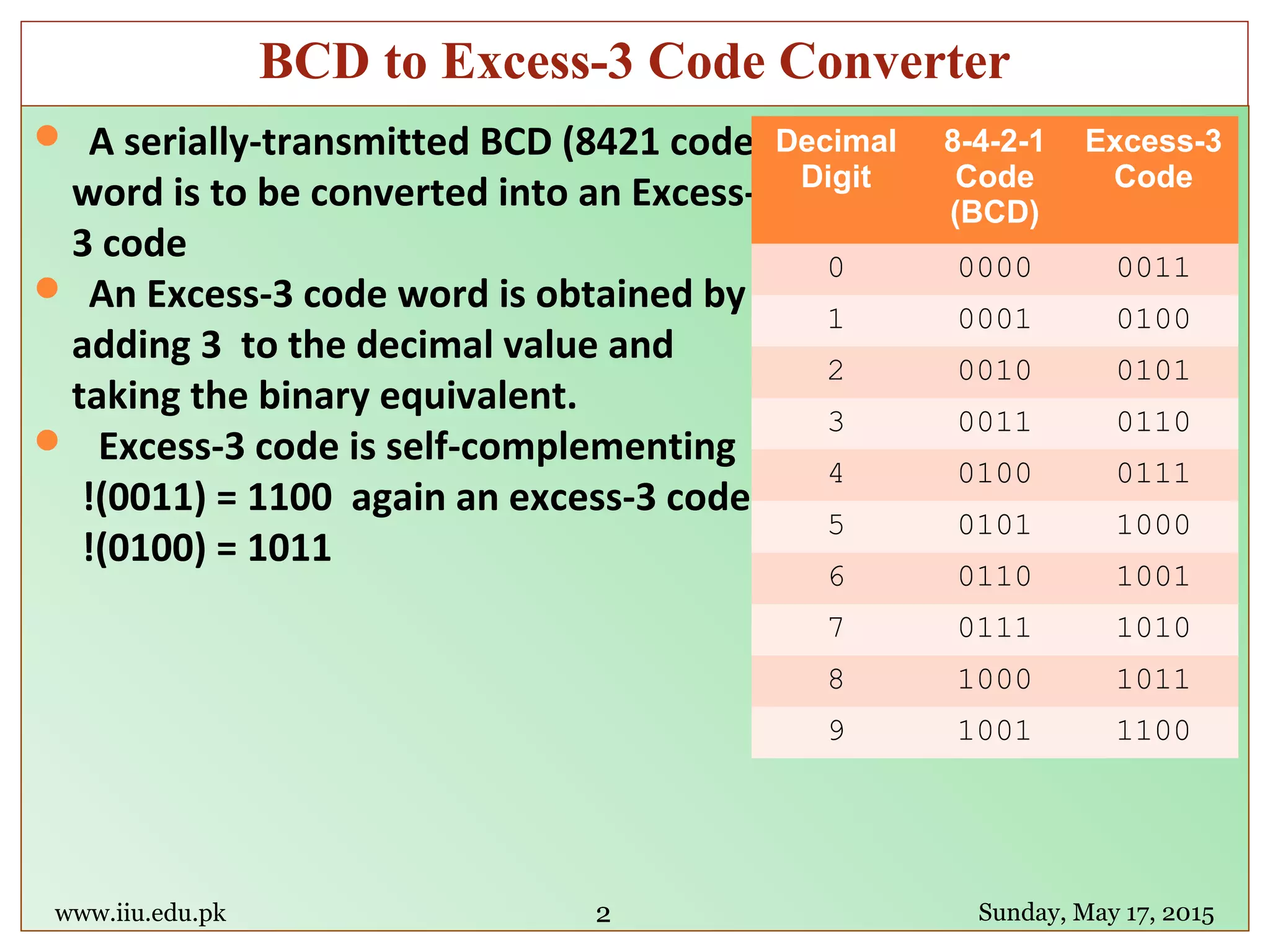

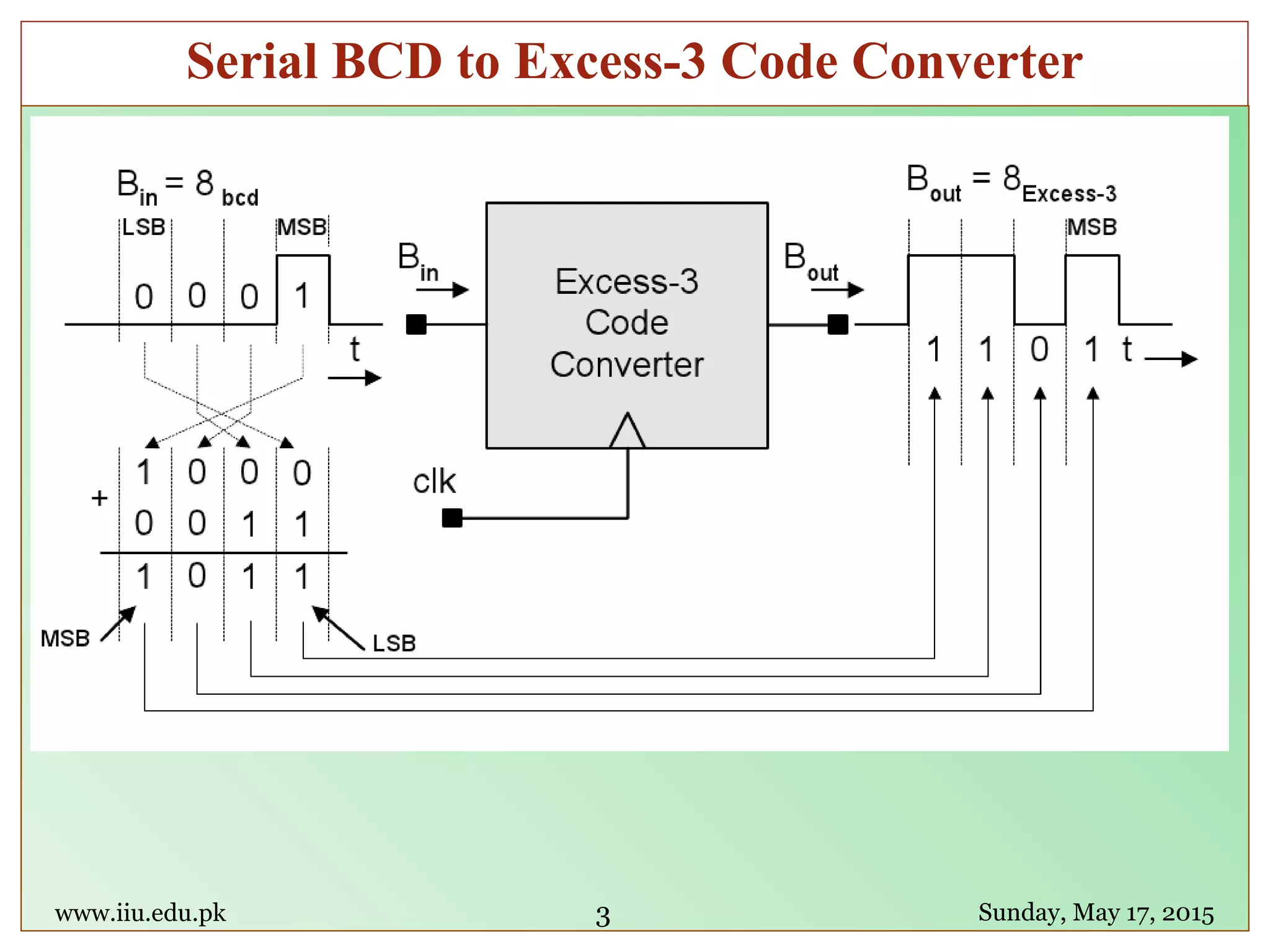

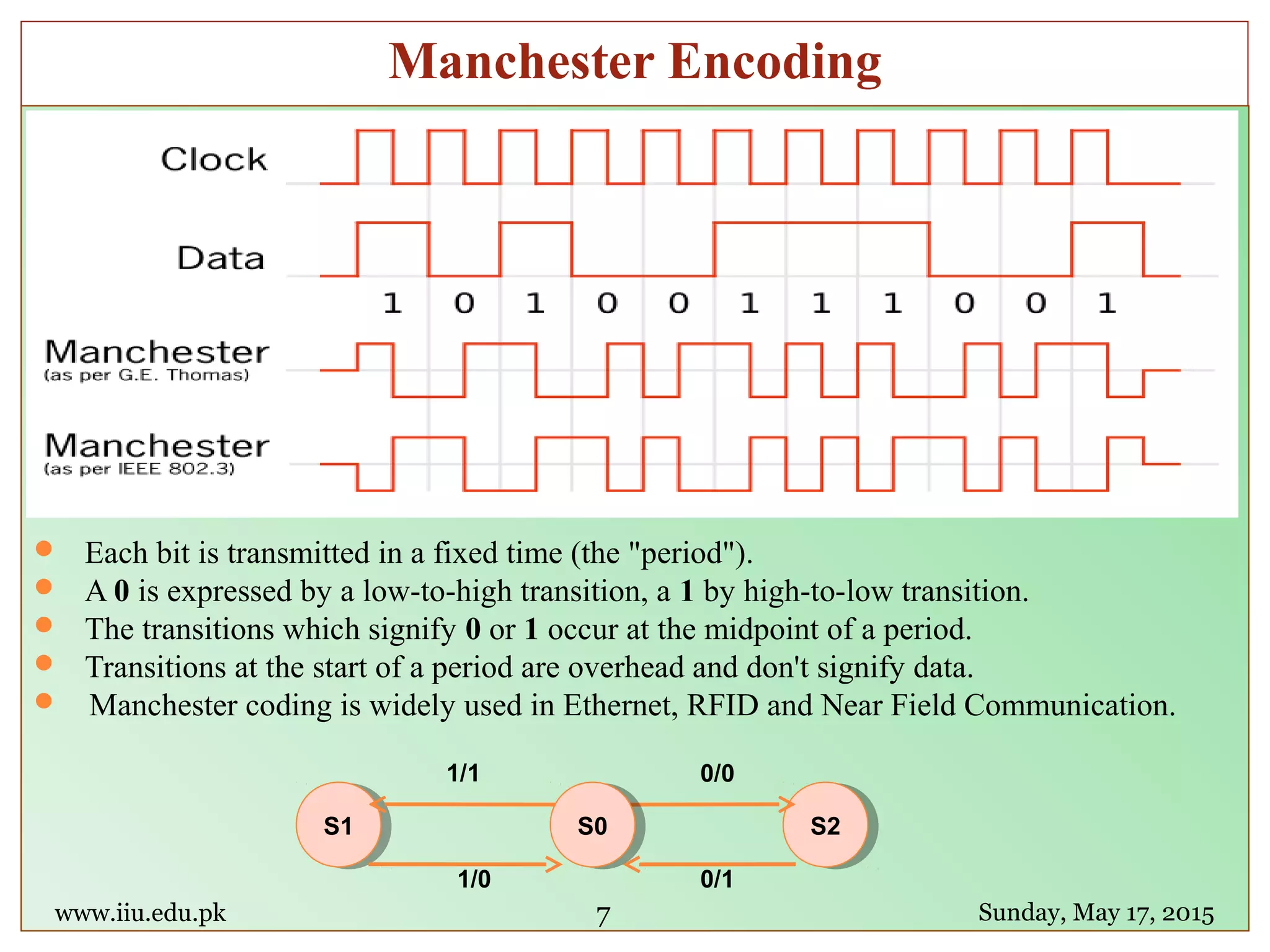

The document discusses BCD to Excess-3 code conversion and Manchester encoding. It describes how to convert a serially transmitted BCD word into an Excess-3 code using a state machine with 3 states. It also explains Manchester encoding as transmitting a 0 as a low-to-high transition and 1 as a high-to-low transition at the midpoint of each period. Verilog code is provided for a BCD to Excess-3 converter and Manchester encoder, along with test benches.

![module BCD_to_Excess_3 (y, x, pstate, clk, reset);

output y, pstate; input x, clk, reset;

parameter S0 = 3'd0, S1 = 3'd1, S2 = 3'd2, S3 = 3'd3, S4 = 3'd4, S5 = 3'd5, S6 = 3'd6;

reg[2: 0] pstate, nxtstate; reg y;

always @ (posedge clk or negedge reset)

if (reset== 0) pstate <= S0; else pstate <= nxtstate;

always @ (pstate or x) begin

case (pstate)

S0: if (x) begin nxtstate = S4; y = 0; end

else begin nxtstate = S1; y = 1; end

S1: if (x) begin nxtstate = S5; y = 0; end

else begin nxtstate = S2; y = 1; end

S2: begin nxtstate = S3; y = x; end

S3: begin nxtstate = S0; y = x; end

S4: begin nxtstate = S5; y = x; end

S5: if (x) begin nxtstate = S6; y = 0; end

else begin nxtstate = S3; y = 1; end

S6: begin nxtstate = S0; y = 1; end

default: begin nxtstate = 3'dx; y = 1'bx; end

endcase end endmodule

www.iiu.edu.pk Sunday, May 17, 2015

Behavioral Modeling

5](https://image.slidesharecdn.com/fpga-10-bcd-to-excess-3-converter-manchester-encoding-150517184352-lva1-app6892/75/Fpga-10-bcd-to-excess-3-converter-manchester-encoding-5-2048.jpg)

![module Test_BCD_to_Excess3;

wire y; wire [2:0]pstate; reg x, clk, reset;

BCD_to_Excess_3 BE1 (y, x, pstate, clk, reset);

initial begin reset = 1;

#7 reset = 0; #3 reset = 1;

end

initial begin clk = 0;

repeat (20) #5 clk = ~clk;

end

initial begin x = 1;

repeat (10) #10 x = ~ x;

end

endmodule

www.iiu.edu.pk Sunday, May 17, 2015

Test Bench

6

S0S0

S1S1

S2S2

S3S3

0/1

0/1

0/0

0/0

S4S4

1/0

S5S5

0/0

0/1

1/0

S6S6

1/1

1/1 1/0

1/1

0/1

reset](https://image.slidesharecdn.com/fpga-10-bcd-to-excess-3-converter-manchester-encoding-150517184352-lva1-app6892/75/Fpga-10-bcd-to-excess-3-converter-manchester-encoding-6-2048.jpg)

![module NRZ_2_Manchester_Mealy (B_out, state, B_in, clock, reset_b);

output B_out; input B_in; input clock, reset_b; output state;

reg [1: 0] state, next_state; reg B_out;

parameter S0 = 0, S1 = 1, S2 = 2, dont_care_state = 2'bx, dont_care_out = 1'bx;

always @ (negedge clock or negedge reset_b)

if (reset_b == 0) state <= S0;

else state <= next_state;

always @ (state or B_in ) begin

B_out = 0;

case (state)

S0: if (B_in == 0) begin next_state = S2; B_out = 0; end

else if (B_in == 1) begin next_state = S1; B_out = 1; end

S1: begin next_state = S0; B_out = 0; end

S2: begin next_state = S0; B_out = 1; end

default: begin next_state = dont_care_state;

B_out = dont_care_out; end

endcase

end

endmodule

www.iiu.edu.pk Sunday, May 17, 2015

Manchester Encoding

8

S1S1 S2S2

0/01/1

0/11/0

S0S0](https://image.slidesharecdn.com/fpga-10-bcd-to-excess-3-converter-manchester-encoding-150517184352-lva1-app6892/75/Fpga-10-bcd-to-excess-3-converter-manchester-encoding-8-2048.jpg)

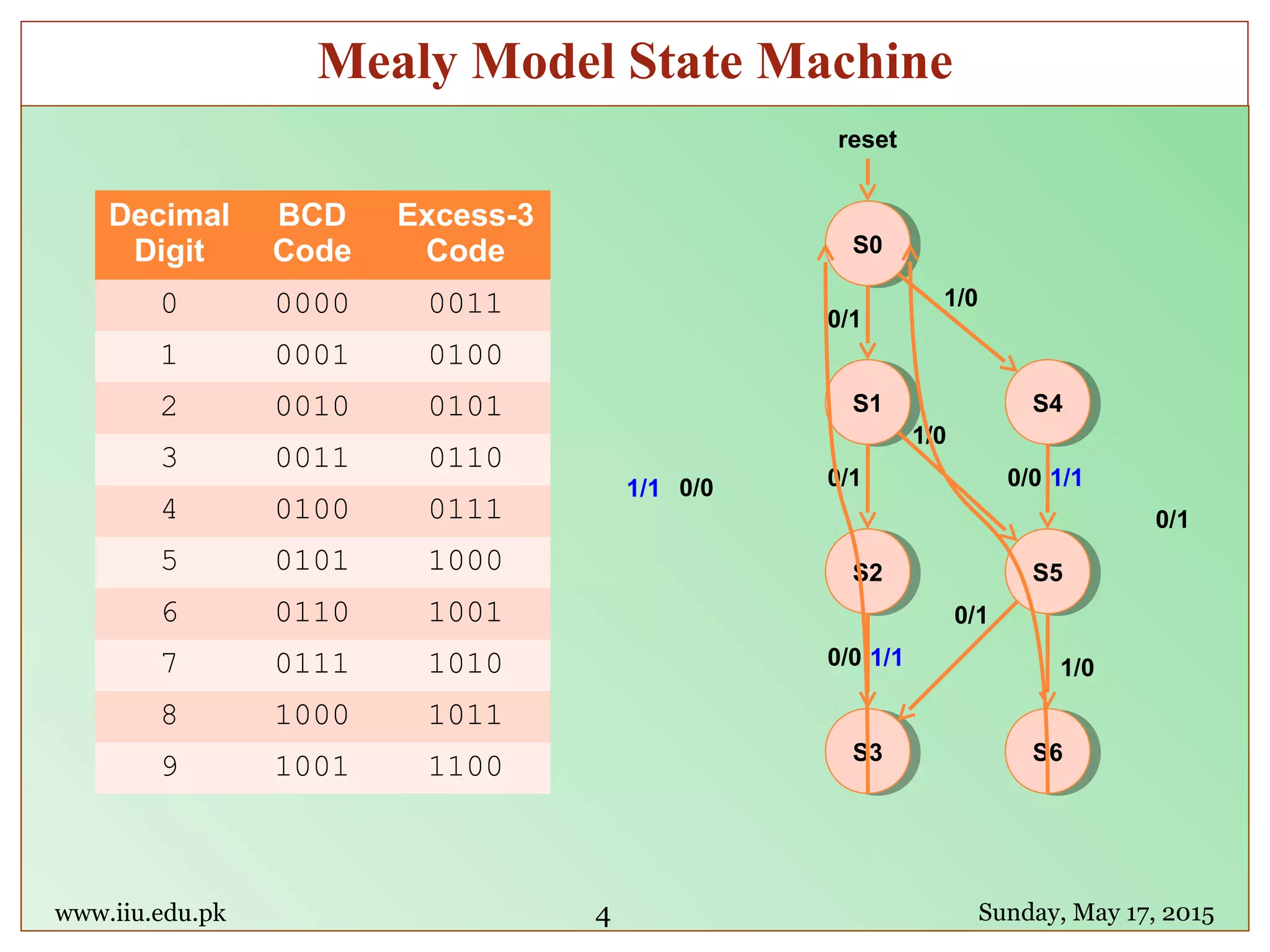

![module test_NRZ_2_Manchester_Mealy;

wire B_out; reg B_in, clk, rst; wire [1:0] state; reg clk2;

NRZ_2_Manchester_Mealy (B_out, state, B_in, clk, rst);

initial begin rst = 1; #7 rst = 0; #3 rst = 1; end

initial begin clk = 0;

repeat (20) #5 clk = ~clk; end

initial begin clk2 = 1;

repeat (10) #10 clk2 = ~clk2; end

initial begin B_in = 1;

repeat (3) #40 B_in = ~ B_in; end

endmodule

www.iiu.edu.pk Sunday, May 17, 2015

Manchester Encoding Test Bench

9

S1S1 S2S2

0/01/1

0/11/0

S0S0](https://image.slidesharecdn.com/fpga-10-bcd-to-excess-3-converter-manchester-encoding-150517184352-lva1-app6892/75/Fpga-10-bcd-to-excess-3-converter-manchester-encoding-9-2048.jpg)

![module test_NRZ_2_Manchester_Mealy;

wire B_out; reg B_in, clk, rst; wire [1:0] state; reg clk2;

NRZ_2_Manchester_Mealy (B_out, state, B_in, clk, rst);

initial begin rst = 1; #7 rst = 0; #3 rst = 1; end

initial begin clk = 0;

repeat (20) #5 clk = ~clk; end

initial begin clk2 = 1;

repeat (10) #10 clk2 = ~clk2; end

initial begin B_in = 1;

repeat (3) #40 B_in = ~ B_in; end

endmodule

www.iiu.edu.pk Sunday, May 17, 2015

Manchester Encoding Test Bench

9

S1S1 S2S2

0/01/1

0/11/0

S0S0](https://image.slidesharecdn.com/fpga-10-bcd-to-excess-3-converter-manchester-encoding-150517184352-lva1-app6892/75/Fpga-10-bcd-to-excess-3-converter-manchester-encoding-10-2048.jpg)