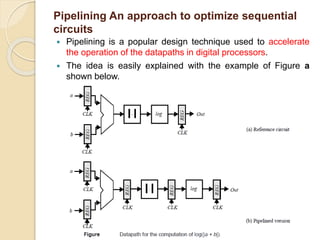

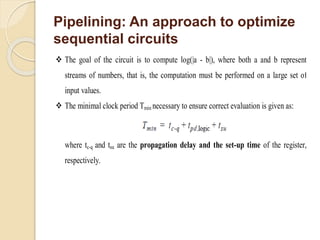

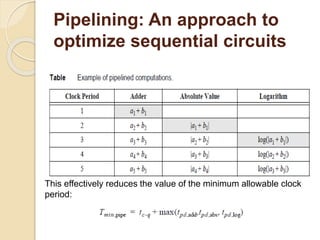

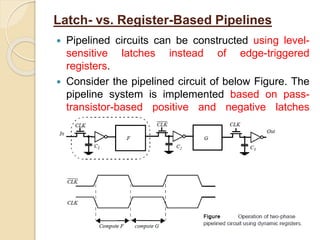

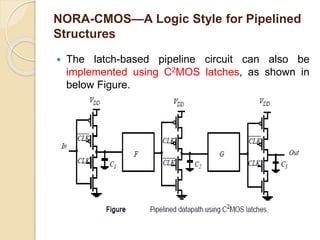

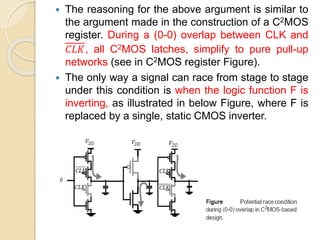

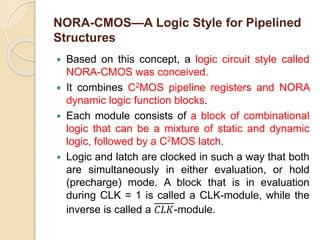

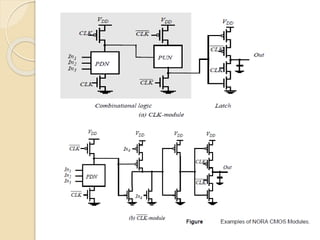

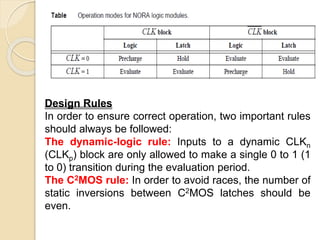

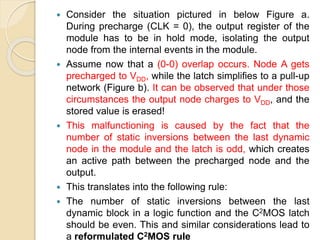

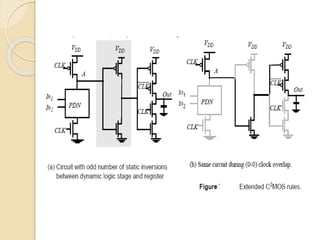

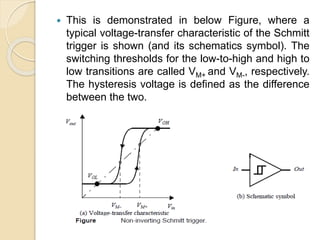

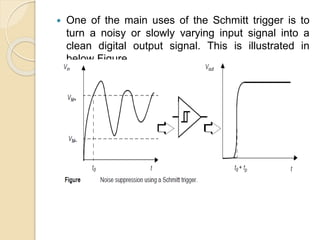

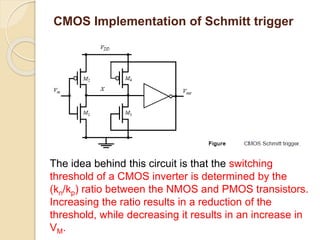

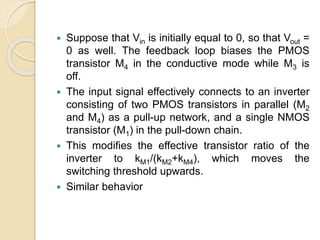

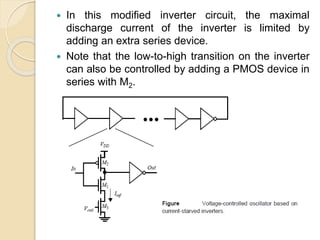

This document discusses pipelining as an approach to optimize sequential circuits. It describes how pipelining can be implemented using registers between logic blocks to improve resource utilization and increase throughput. This allows computations to be spread over multiple clock cycles in an assembly-line fashion. The document also discusses latch-based vs register-based pipelines and different logic styles like NORA-CMOS that can be used for pipelined structures. It covers design rules and considerations for ensuring correct pipelined operation. Finally, it briefly describes non-bistable sequential circuits like astable, monostable and Schmitt trigger circuits.