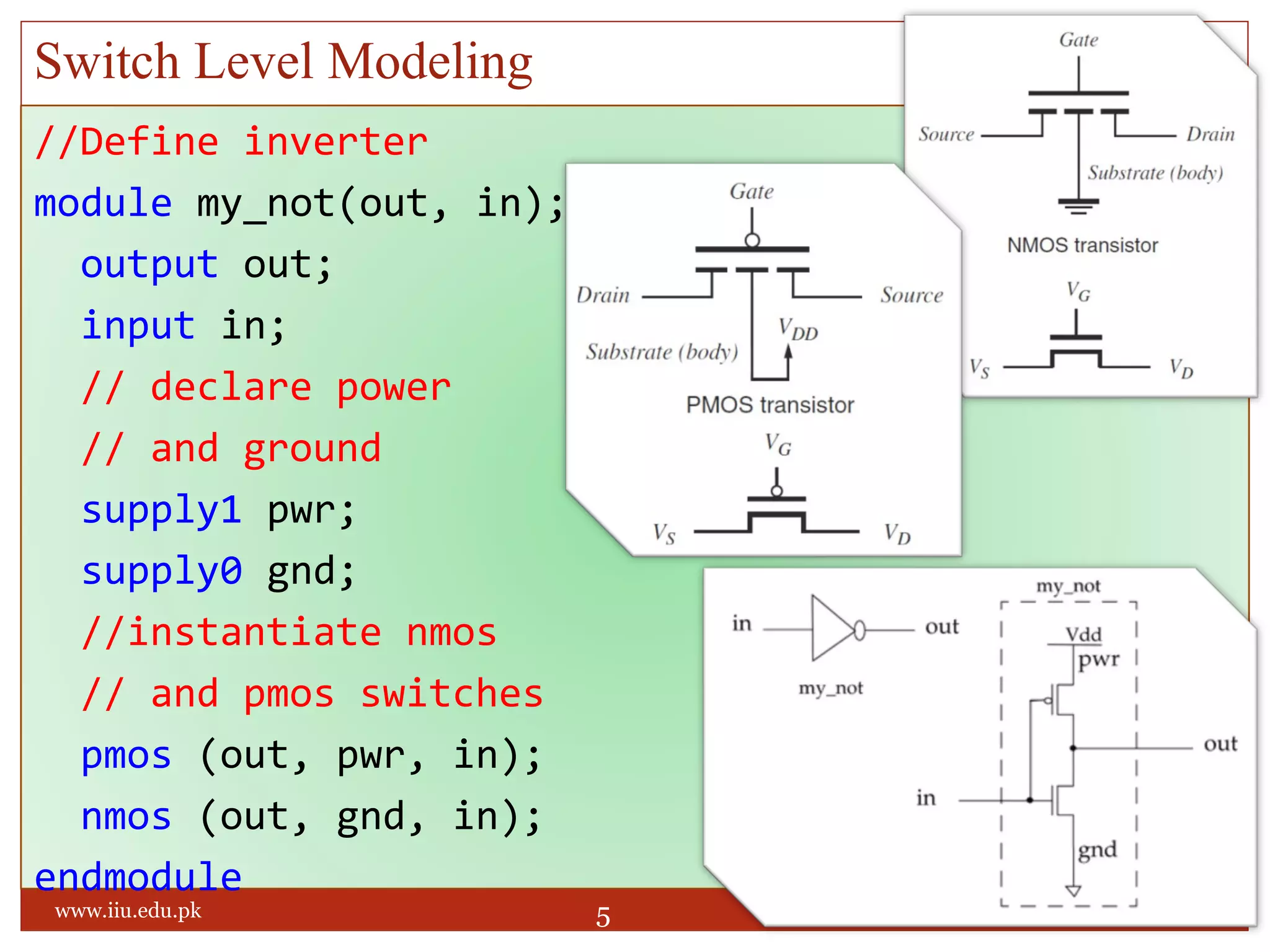

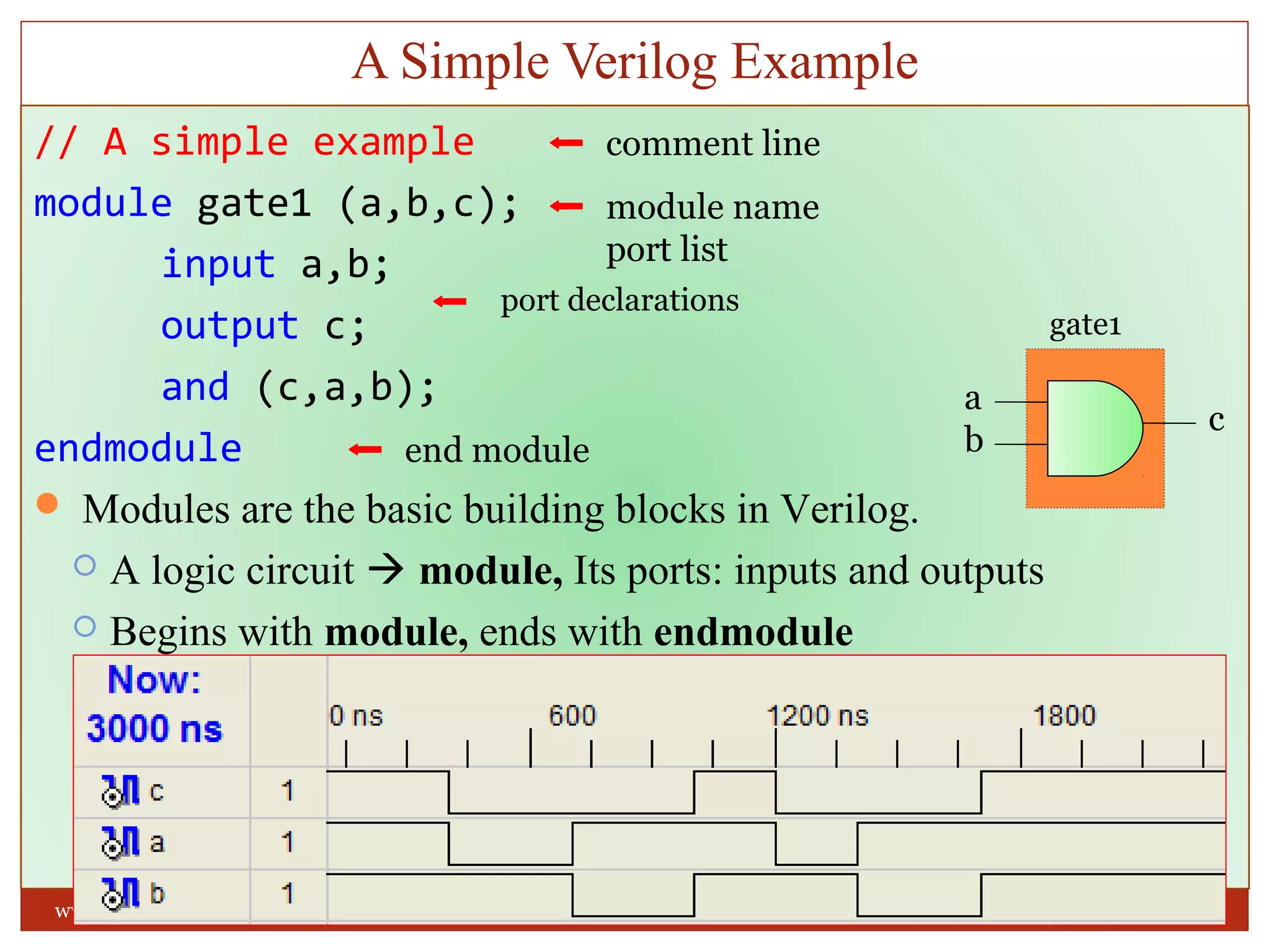

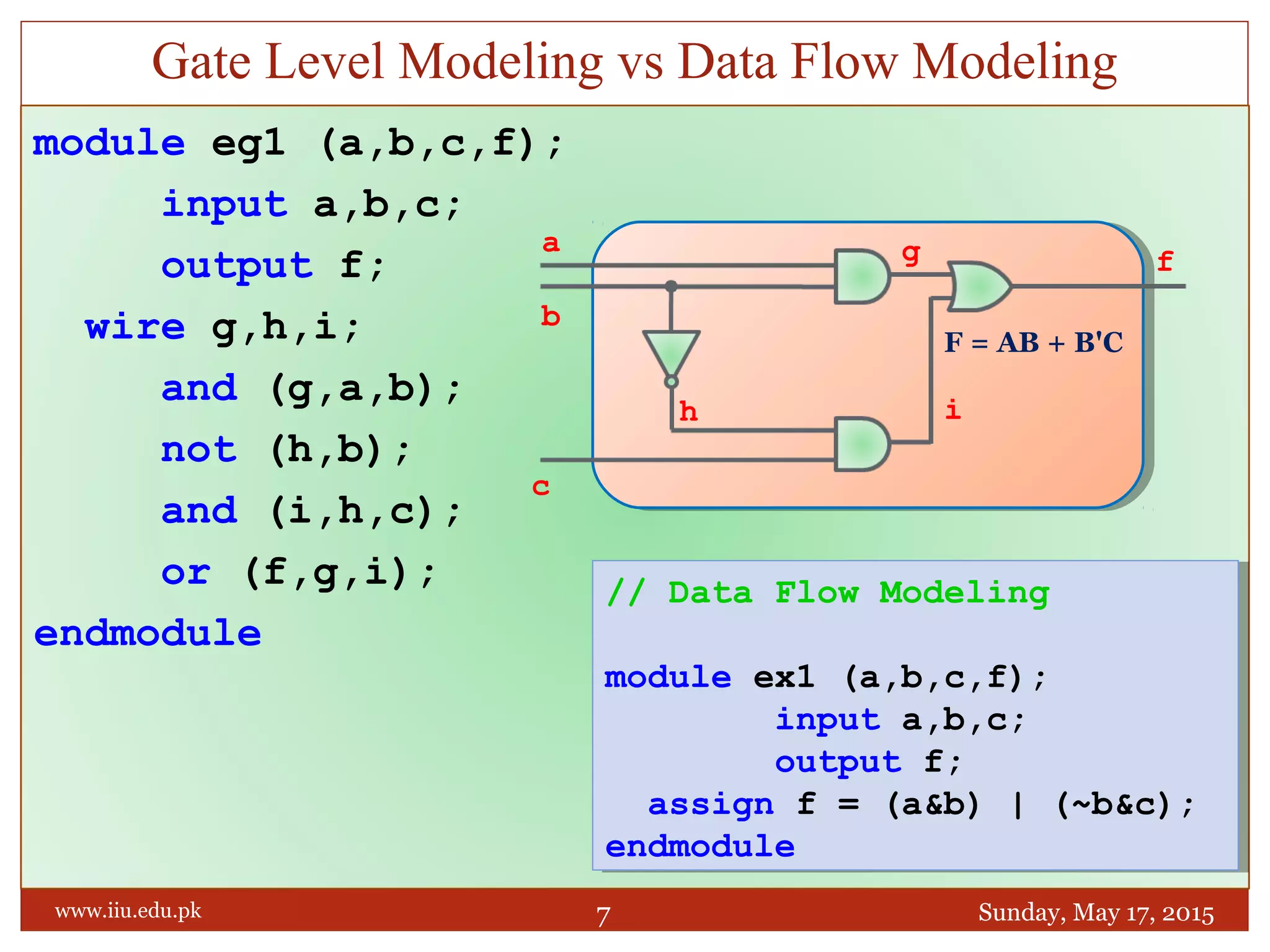

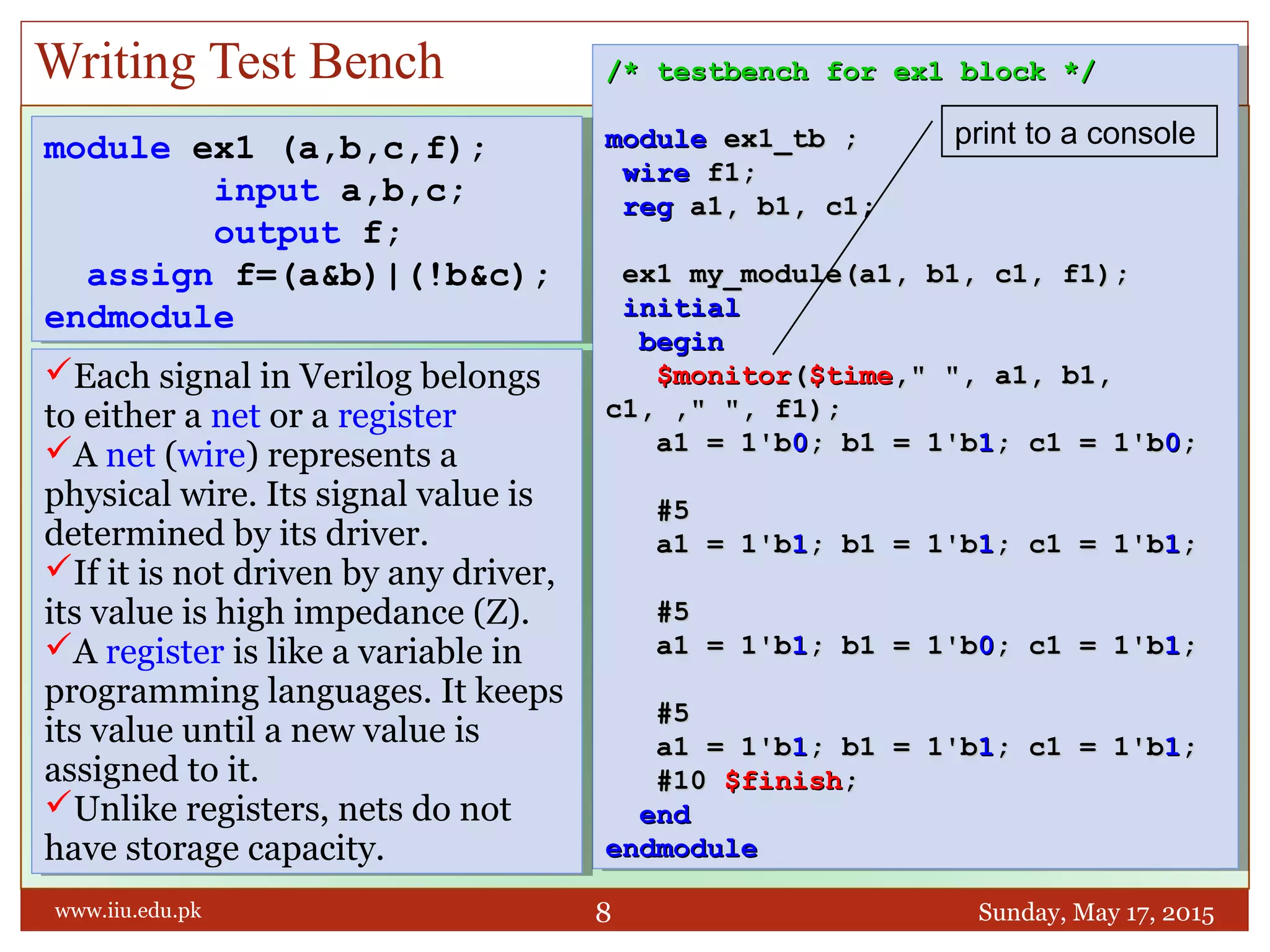

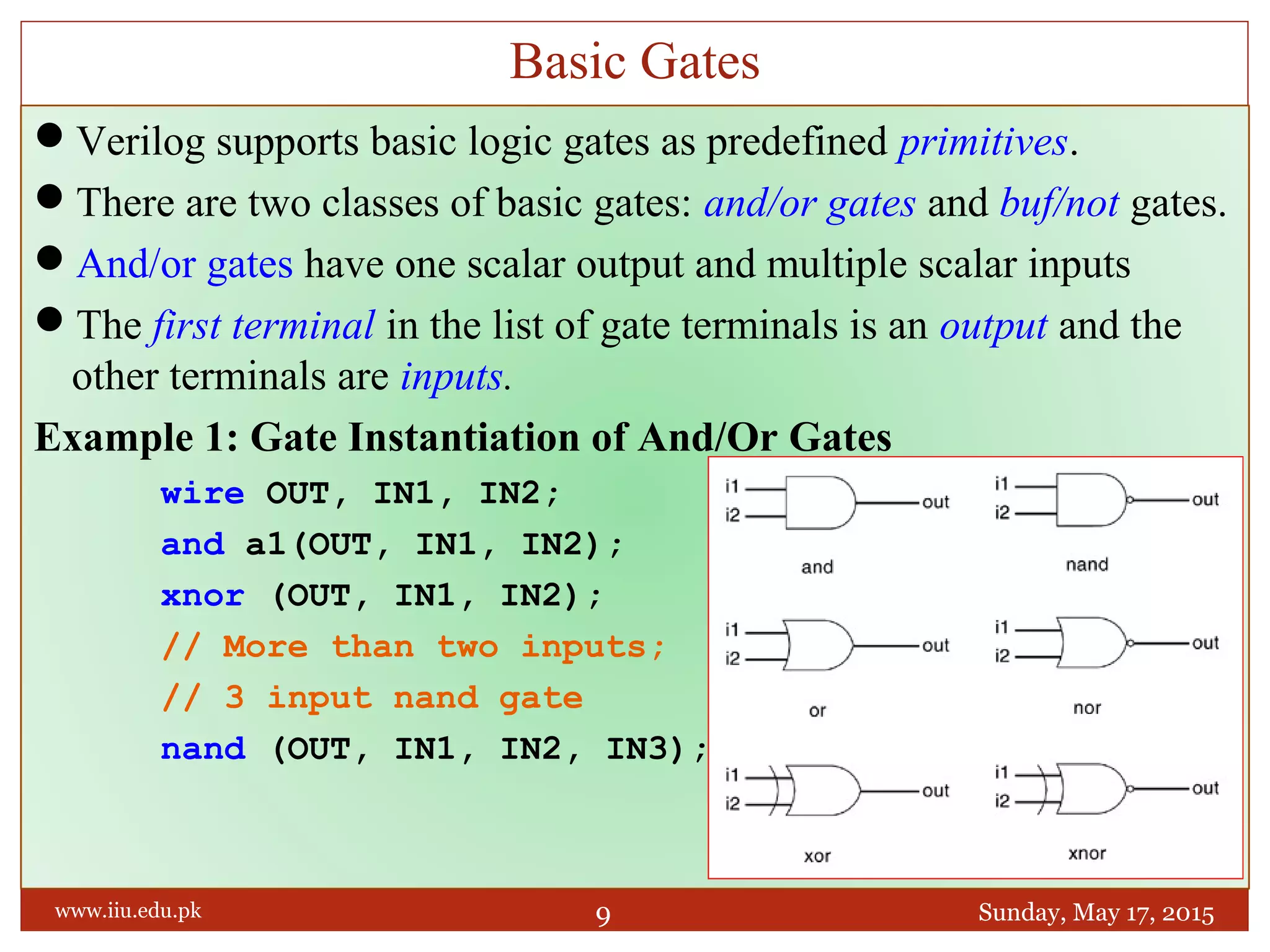

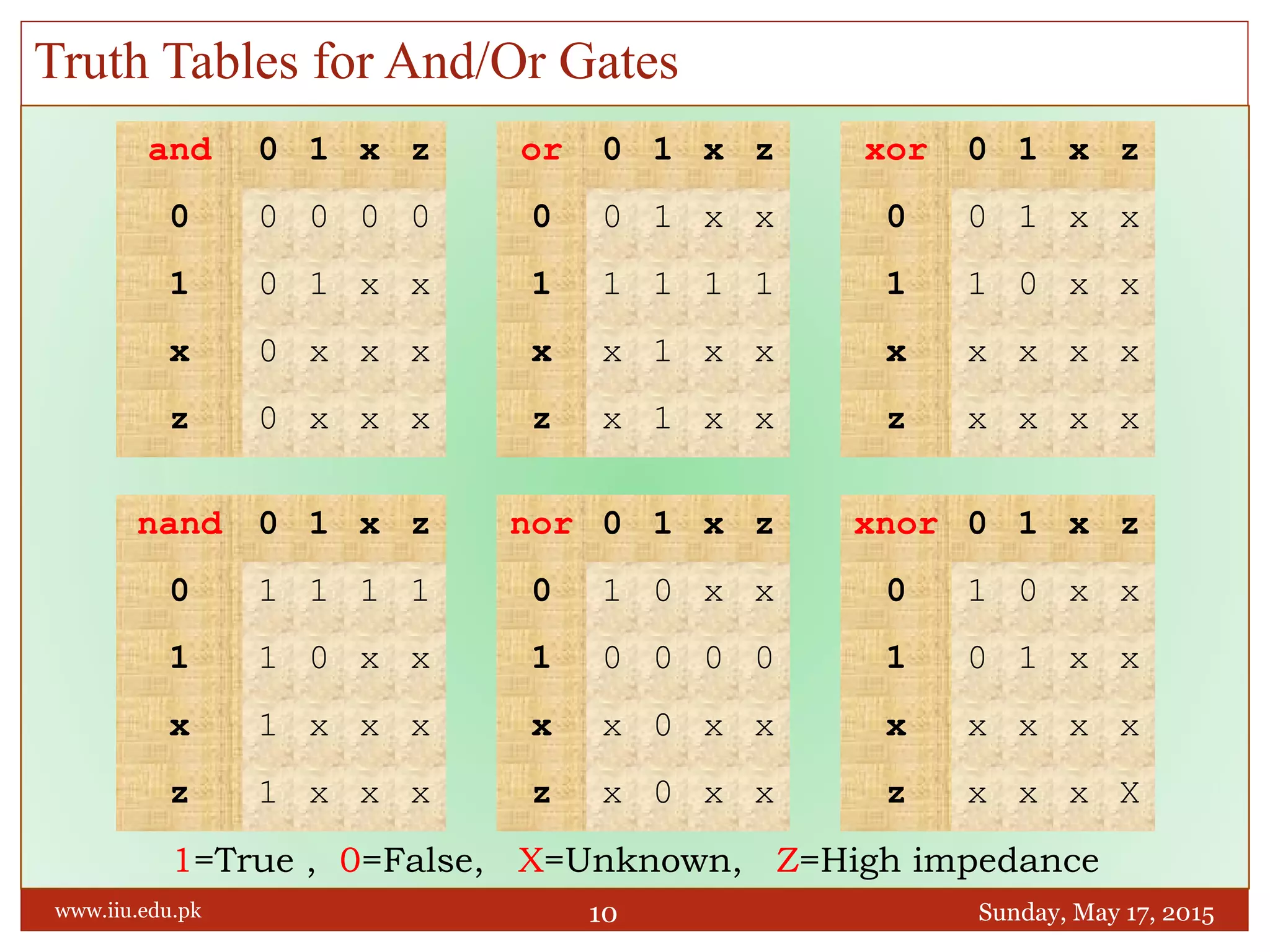

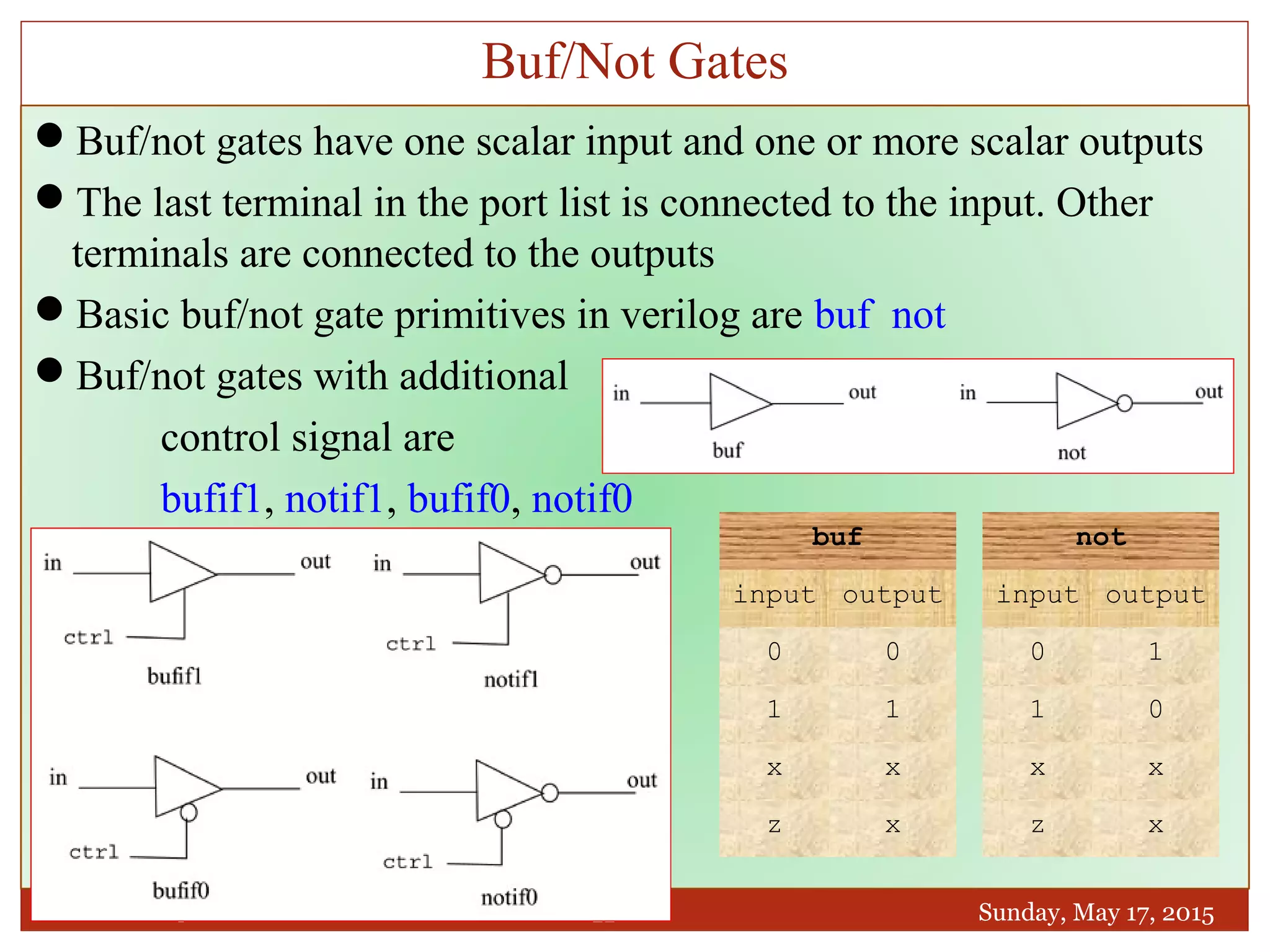

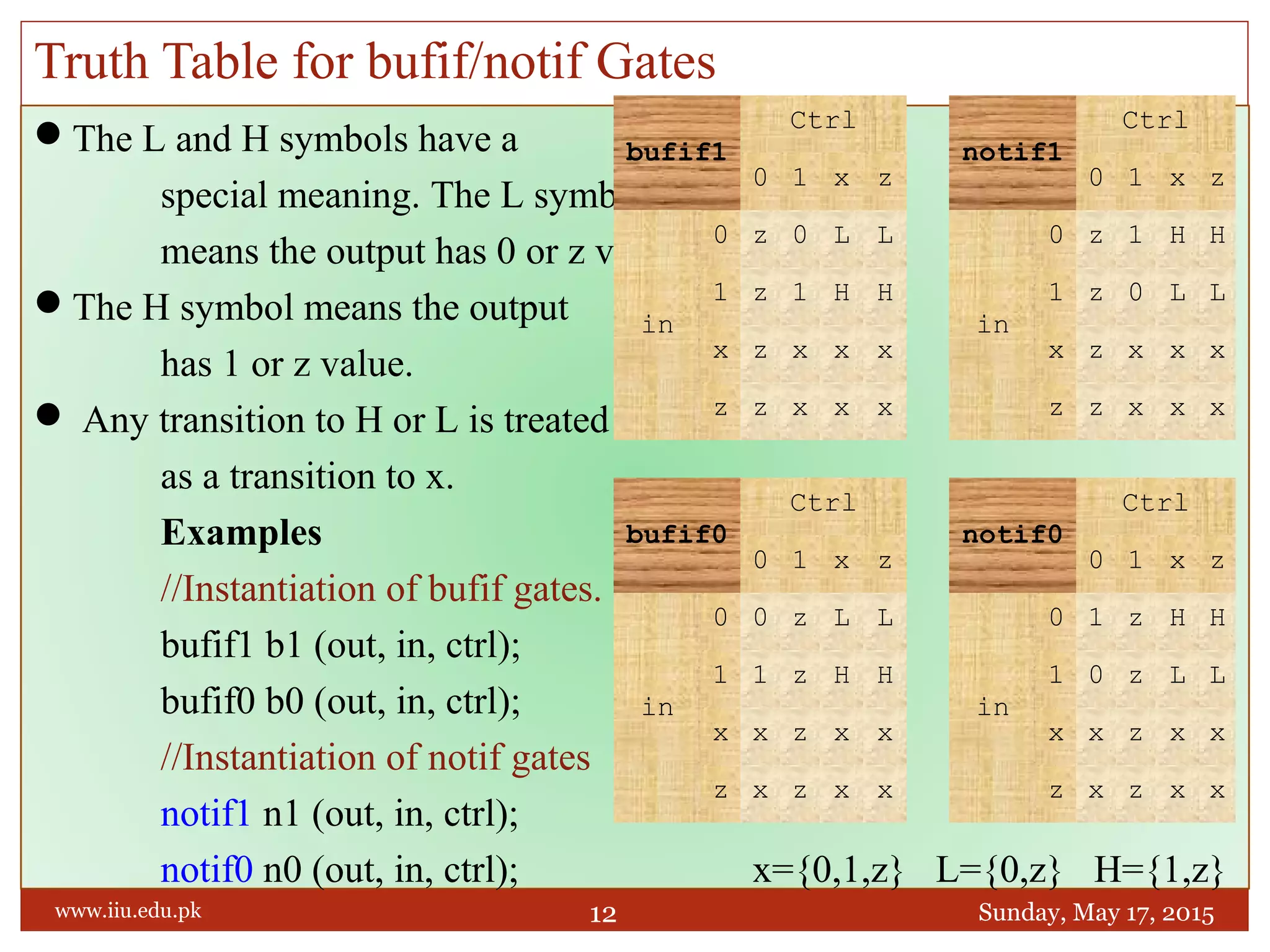

The document discusses hardware description languages (HDLs) and Verilog programming. It states that two widely used HDLs are Verilog and VHDL. Verilog is more popular than VHDL for FPGA programming. The document then provides details on the history, functions, and usage of Verilog. It explains that Verilog can be used to model circuits at different levels of abstraction, from transistor level to behavioral level. Register transfer level modeling combines behavioral and dataflow modeling, which is suitable for FPGA design. Several examples of Verilog code for gate level and dataflow modeling are also presented.