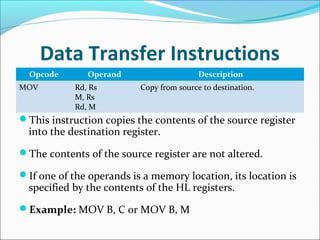

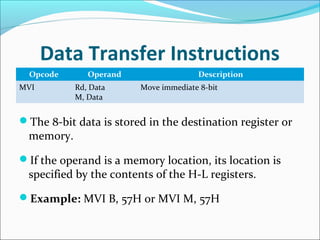

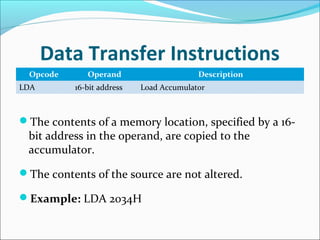

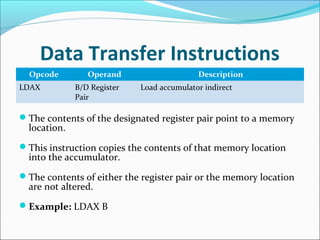

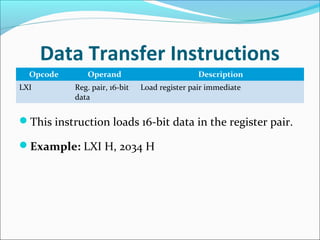

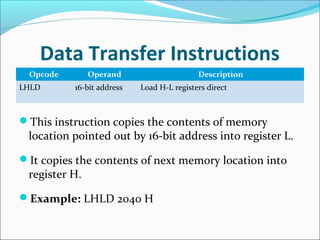

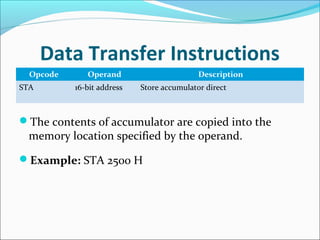

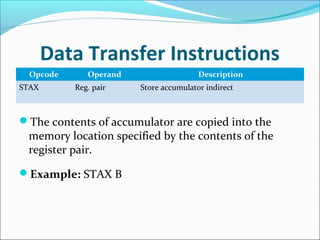

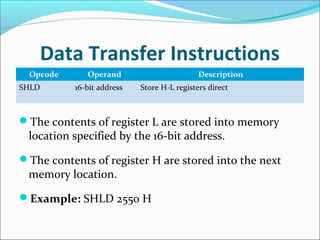

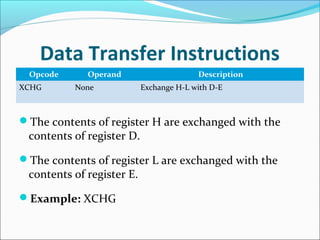

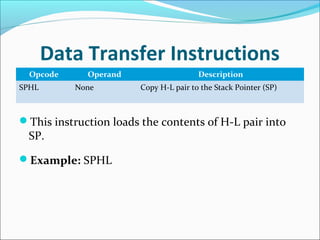

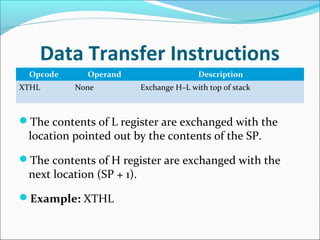

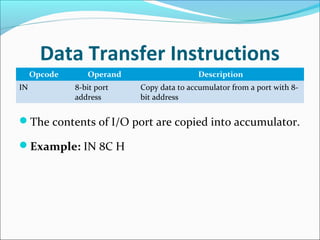

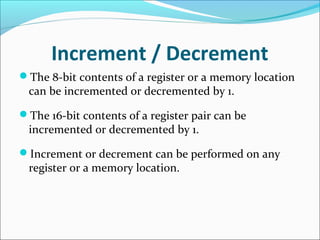

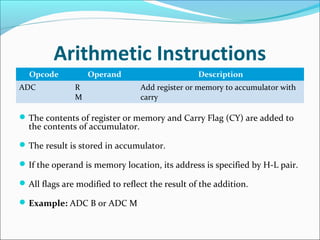

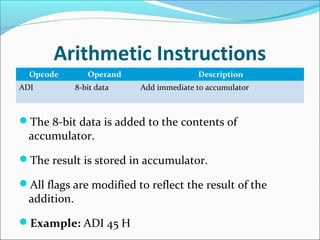

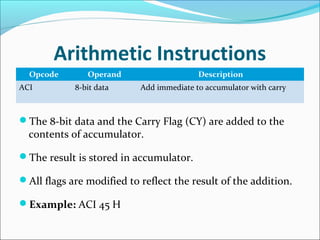

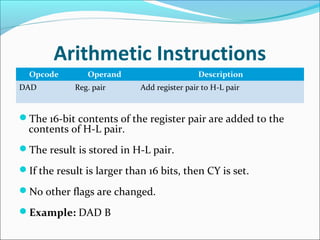

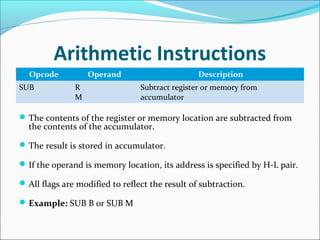

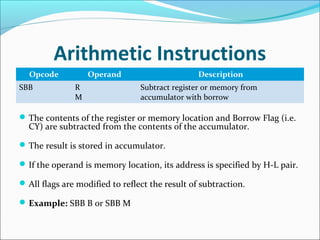

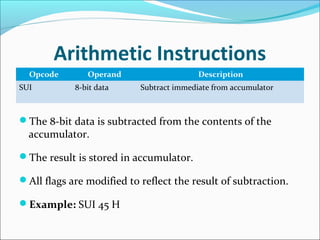

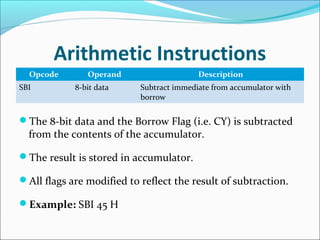

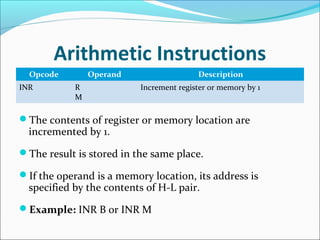

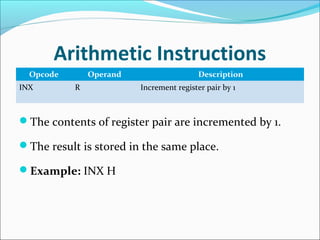

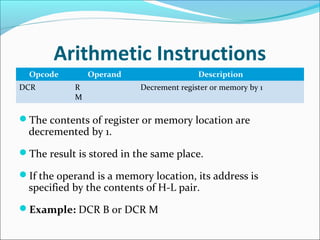

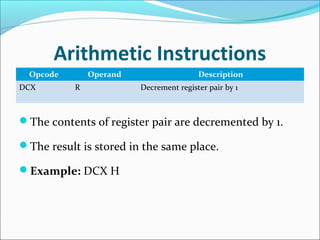

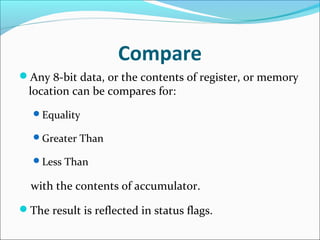

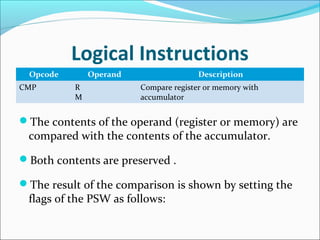

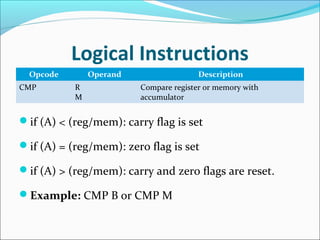

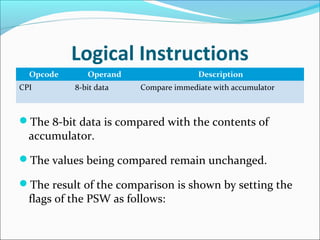

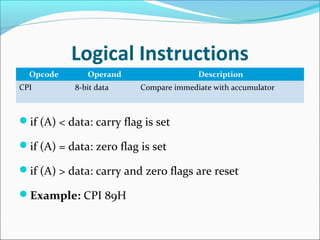

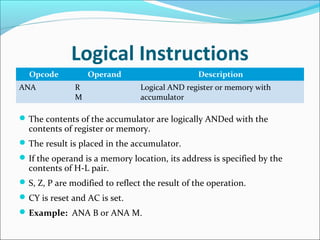

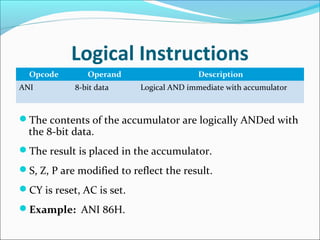

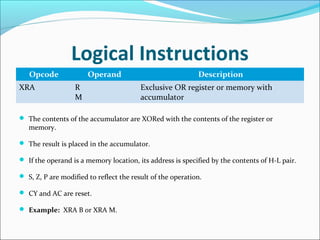

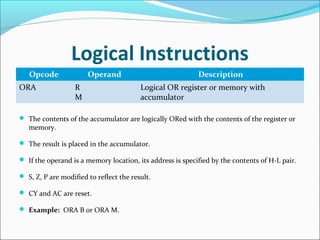

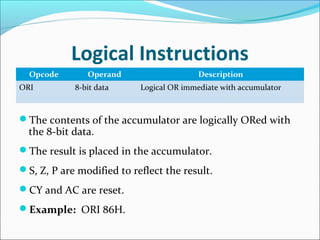

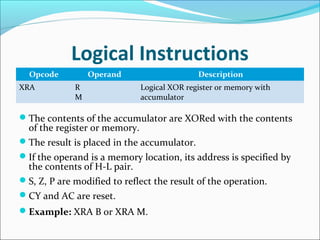

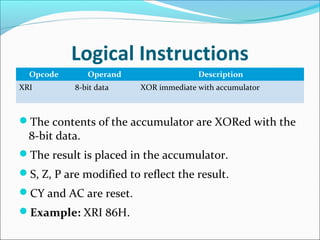

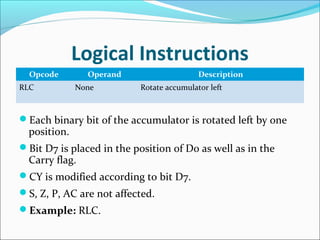

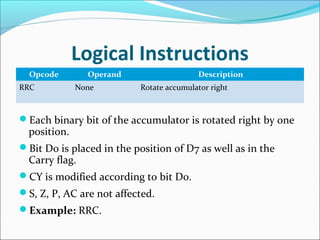

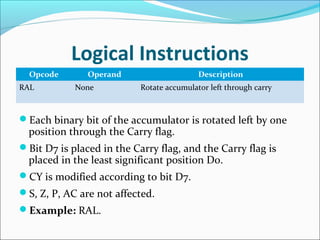

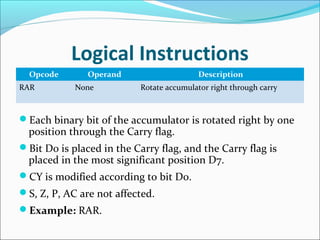

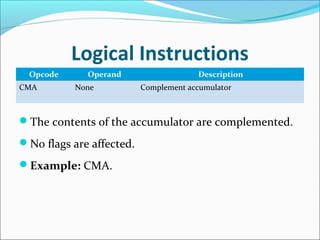

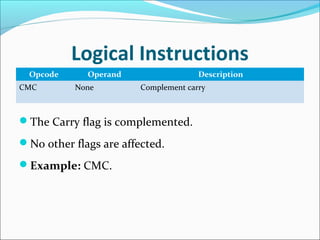

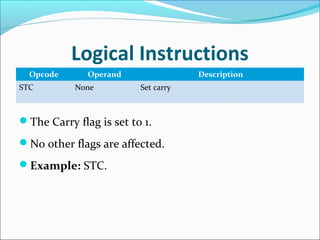

The instruction set of the 8085 microprocessor contains 246 instructions that are classified into different types such as data transfer, arithmetic, logical, branching, and control instructions. Data transfer instructions move data between registers and memory locations. Arithmetic instructions perform operations like addition, subtraction, increment, and decrement. Logical instructions perform logical operations like AND, OR, XOR on registers and memory.