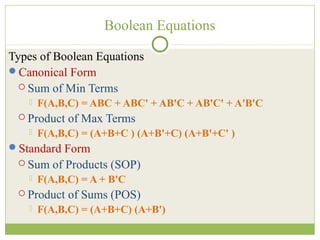

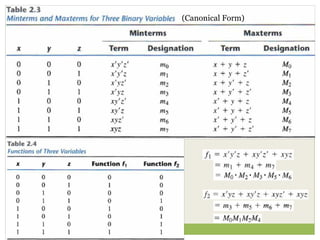

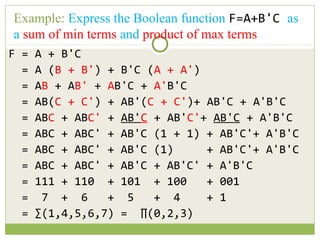

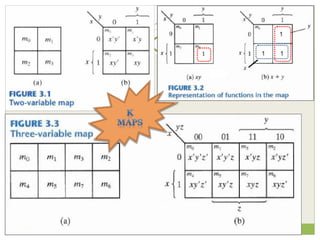

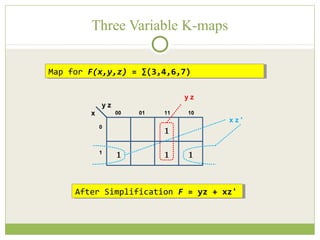

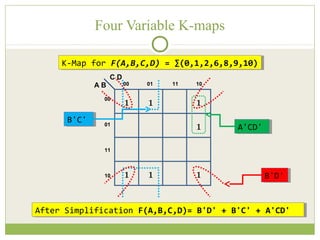

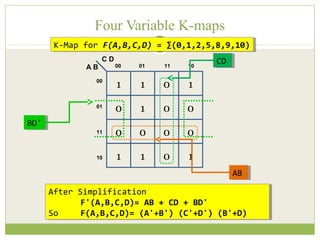

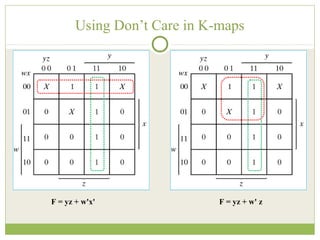

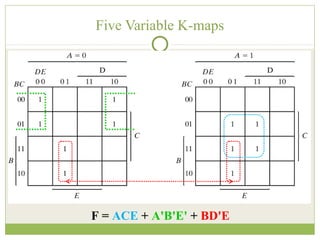

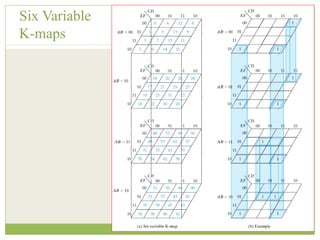

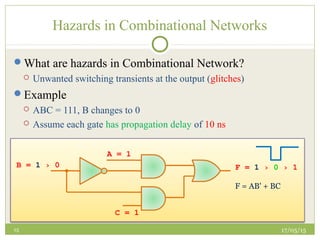

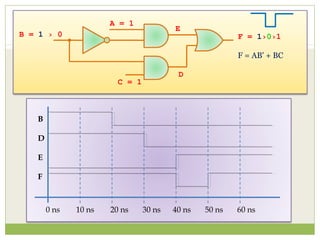

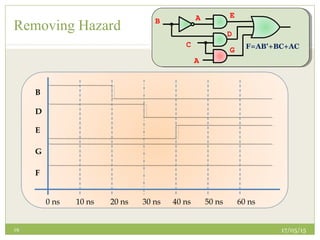

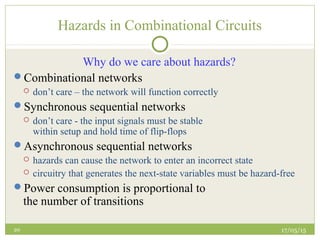

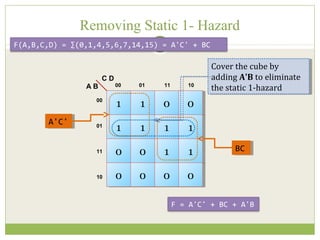

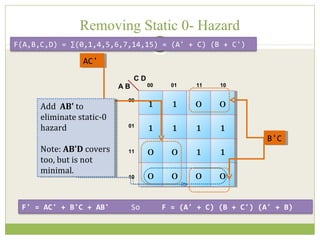

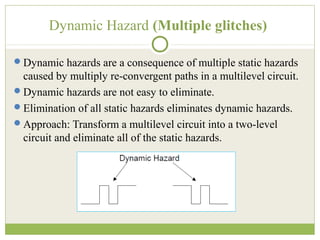

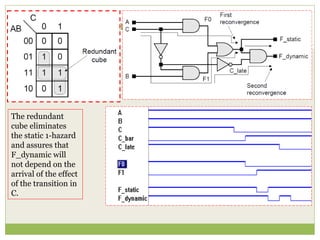

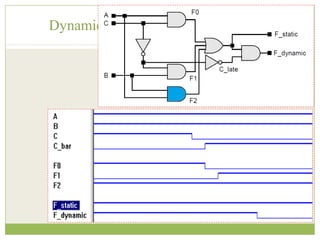

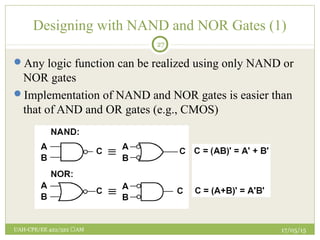

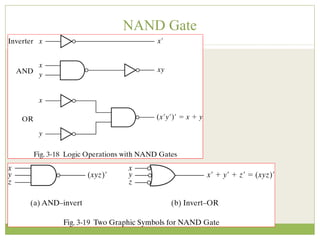

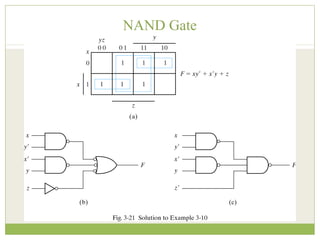

This document provides a summary of digital logic design concepts including combinational logic, Boolean equations, Karnaugh maps, hazards, and NAND/NOR representation. It discusses combinational logic, Boolean equation forms, using Karnaugh maps to minimize logic functions, hazards that can occur in combinational circuits, and ways to remove hazards. It also explains that any logic function can be realized using only NAND or NOR gates and how basic NAND and NOR gates can be implemented using transistors.