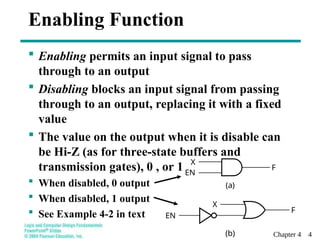

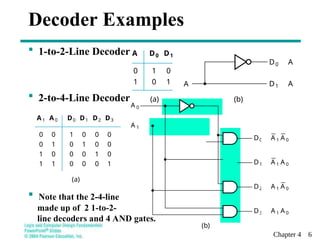

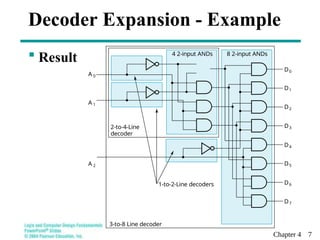

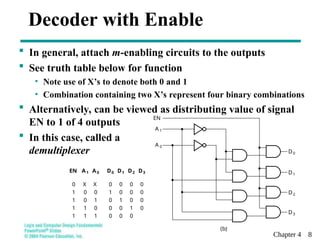

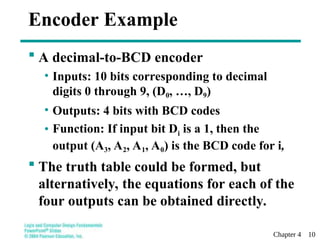

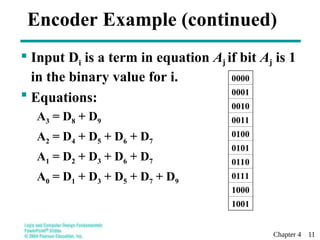

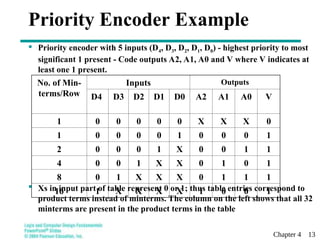

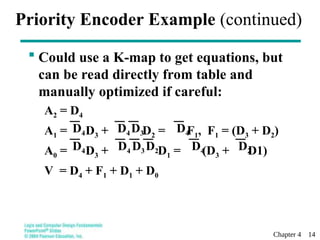

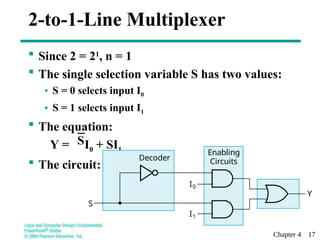

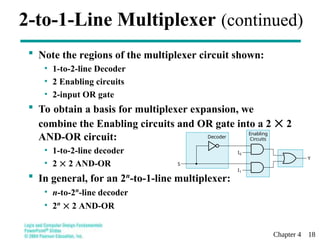

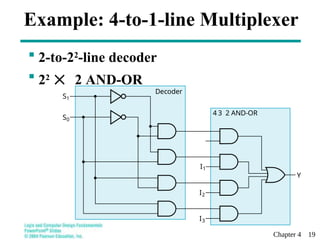

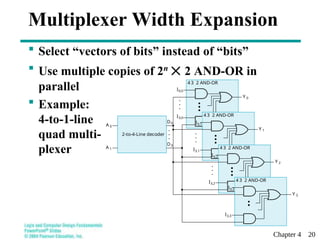

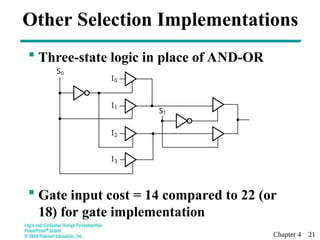

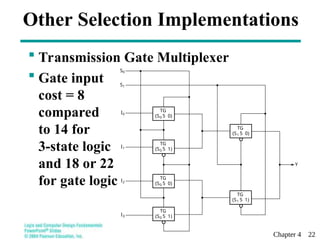

This document discusses combinational functional blocks in logic and computer design, covering topics such as enabling, decoding, encoding, and selecting. It provides detailed explanations and examples of various functional components, including decoders, encoders, and multiplexers, highlighting their roles and implementations in digital systems. Additionally, it outlines terms of use for the educational materials presented.