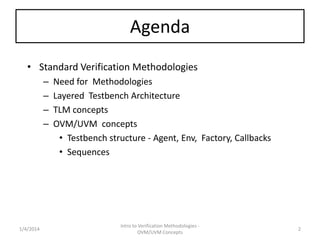

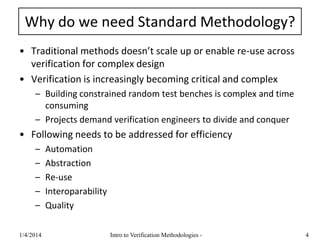

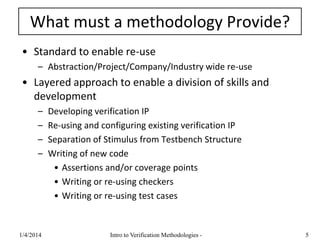

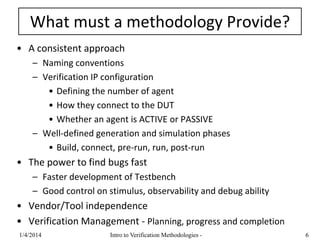

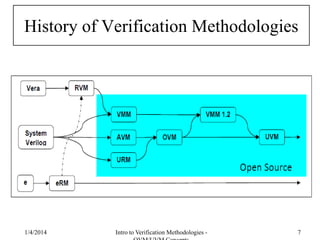

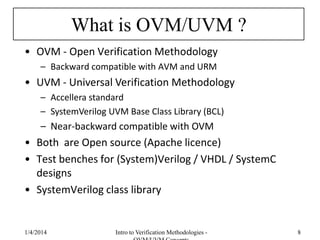

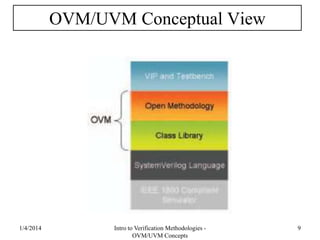

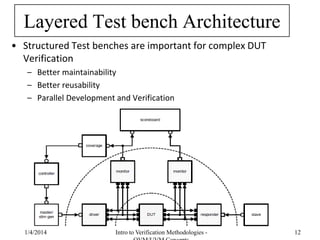

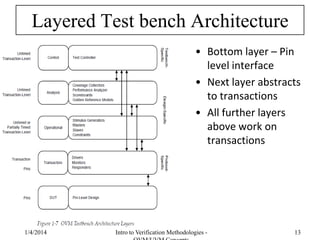

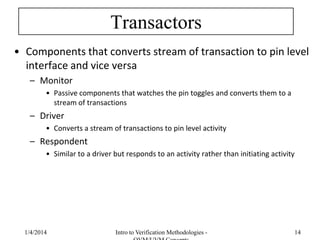

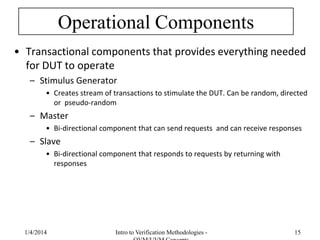

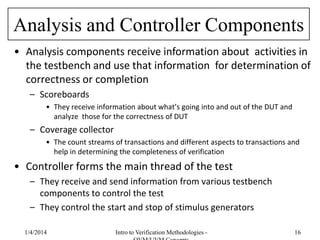

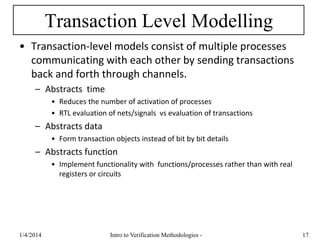

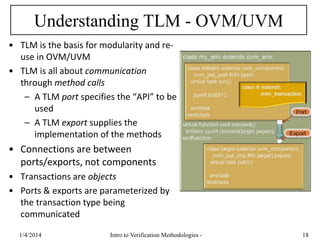

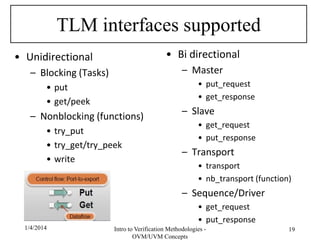

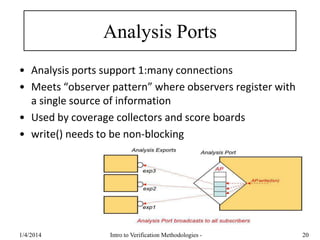

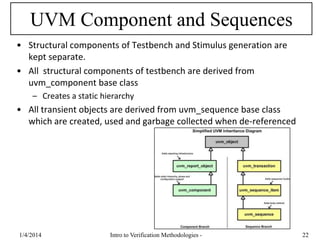

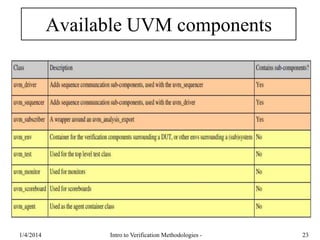

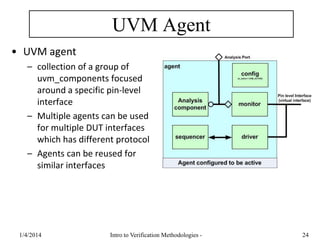

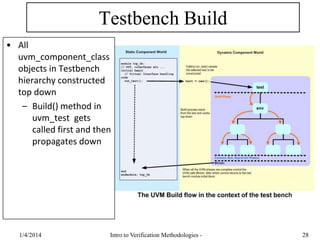

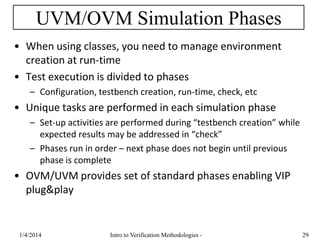

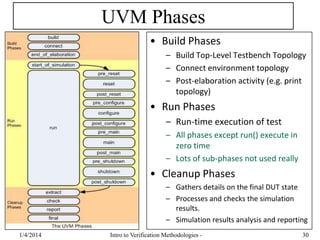

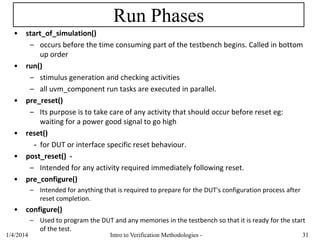

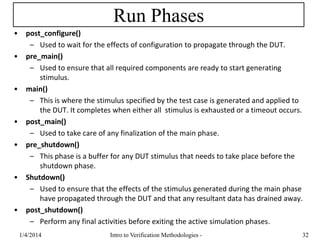

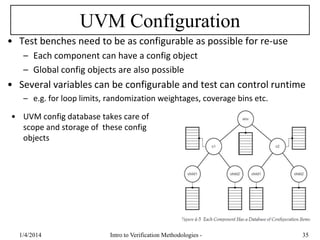

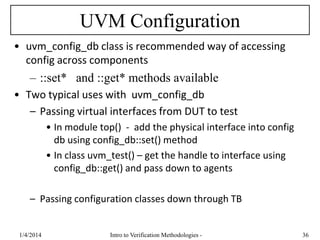

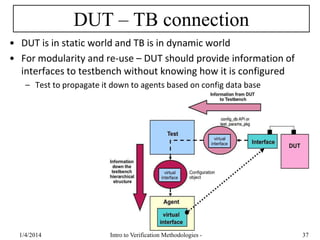

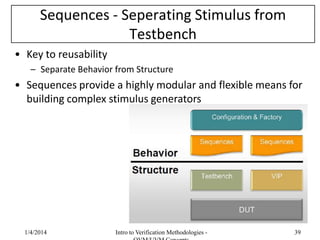

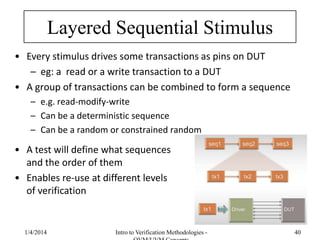

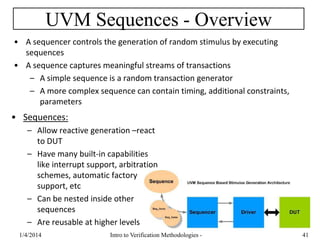

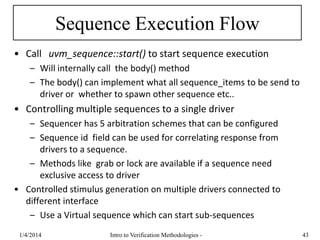

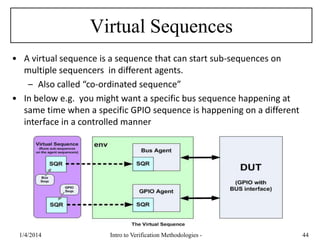

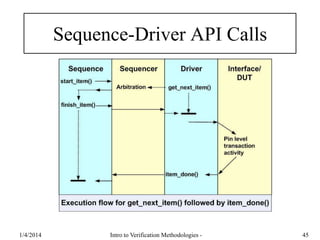

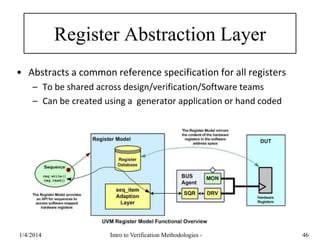

The document provides an introduction to verification methodologies, specifically OVM (Open Verification Methodology) and UVM (Universal Verification Methodology), focusing on structured testbench architecture and the importance of standard methodologies for complex design verification. It highlights the need for automation, reusability, and interoperability in verification processes while detailing the components and phases involved in creating effective testbenches using these methodologies. Additionally, the document discusses transaction-level modeling (TLM), configuration, and the role of sequences in generating stimulus for design under test (DUT).