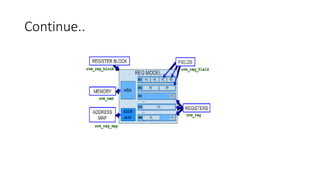

The document discusses the Register Abstraction Layer (RAL) in the context of UVM, emphasizing its significance in providing a register model that facilitates the prediction of expected outputs and simplifies test case implementation. It outlines the structure of RAL with base classes for registers, fields, maps, and blocks, and describes the development process through automation using scripts. It concludes by highlighting the integration and usage of RAL in verification activities, including test case building and coverage.