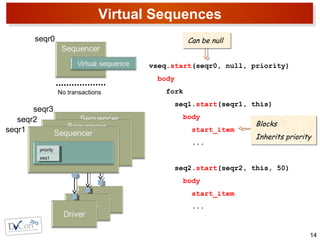

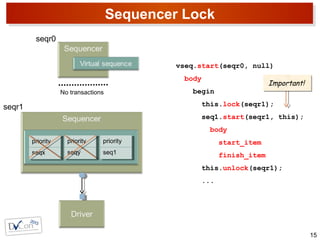

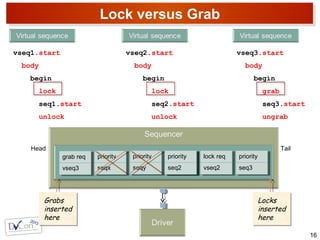

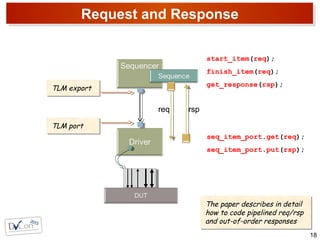

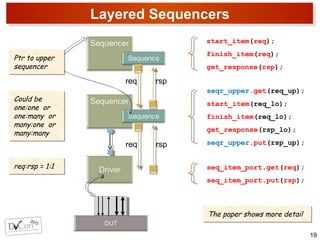

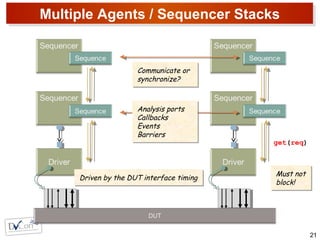

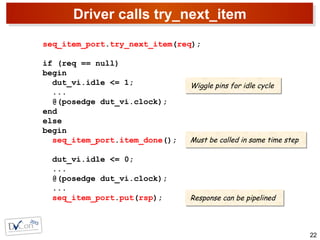

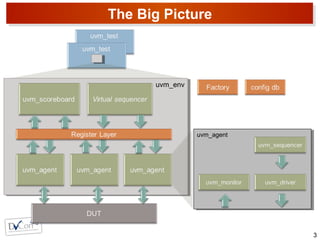

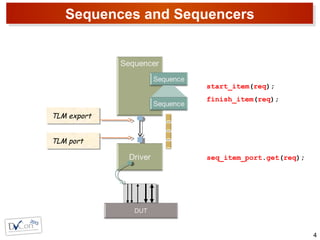

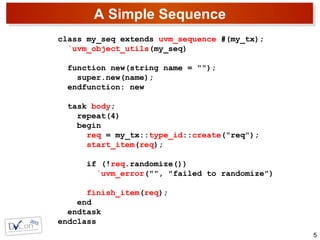

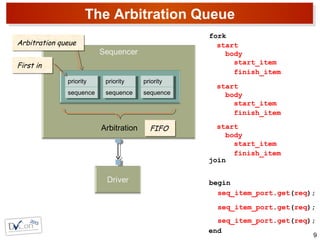

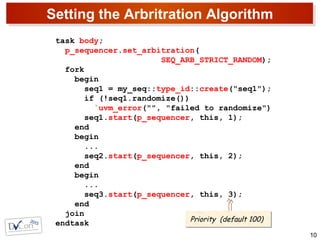

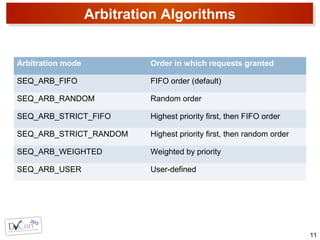

John Aynsley provides an in-depth overview of advanced UVM concepts including sequences and sequencers, virtual sequences, layered sequencers for request-response transactions, and strategies for synchronizing multiple sequencer stacks. The document discusses techniques for modeling pipelined interfaces, out-of-order responses, and idle cycles in a driver. It also examines the arbitration queue, user-defined arbitration algorithms, locking versus grabbing sequences, and using events to synchronize different components.

![User-Defined Arbitration Algorithm

12

class my_sequencer extends uvm_sequencer #(my_tx);

...

function integer user_priority_arbitration(

integer avail_sequences[$]);

foreach (avail_sequences[i])

begin

integer index = avail_sequences[i];

uvm_sequence_request req = arb_sequence_q[index];

int pri = req.item_priority;

uvm_sequence_base seq = req.sequence_ptr;

if (pri > max_pri)

...

end

return max_index;

endfunction

endclass

Could access properties of the sequence objectCould access properties of the sequence object](https://image.slidesharecdn.com/uvmdcon2013-130607034447-phpapp01/85/Uvm-dcon2013-12-320.jpg)