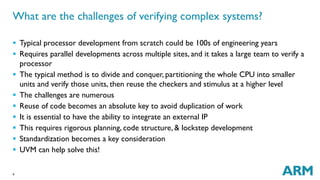

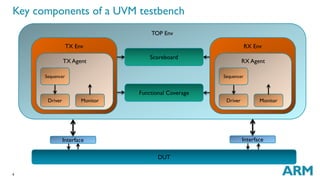

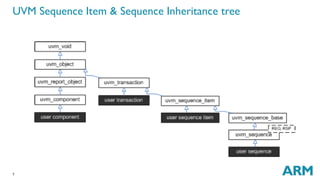

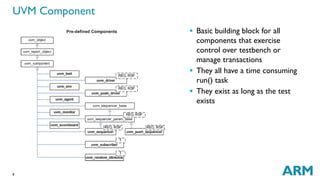

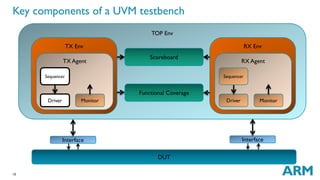

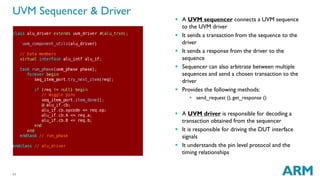

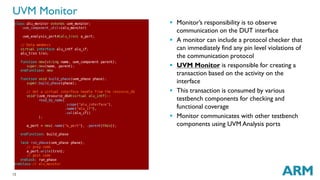

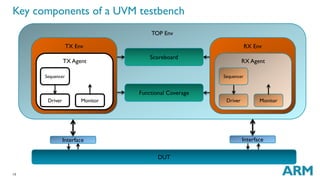

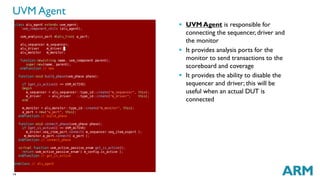

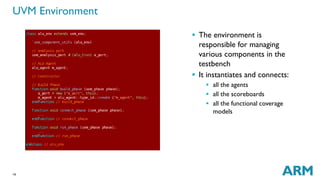

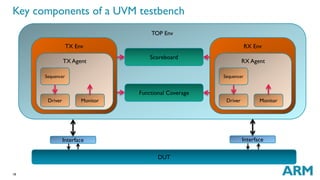

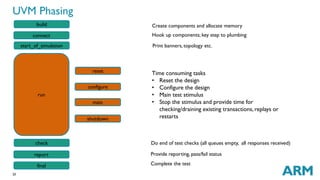

This document discusses the key components and features of the Universal Verification Methodology (UVM) for verifying complex systems. UVM provides a standardized framework for modular and reusable verification components to help address challenges like code duplication. It supports concepts like transactions, sequences, agents, drivers, monitors, scoreboards and environments to build verification testbenches. UVM is maintained by Accellera and its adoption helps enable reuse, clear definition of components, and configuration flexibility.