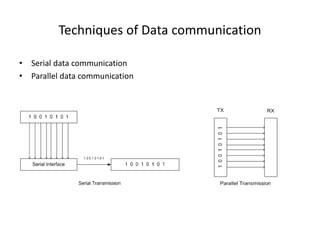

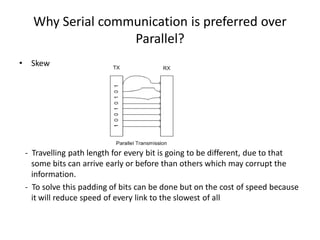

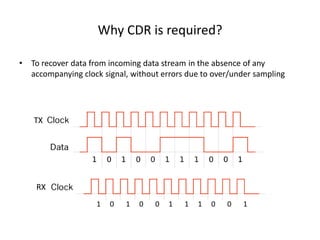

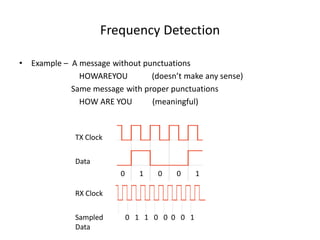

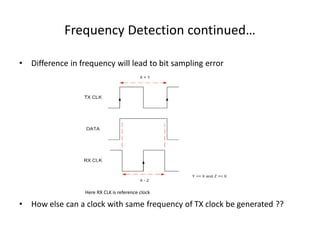

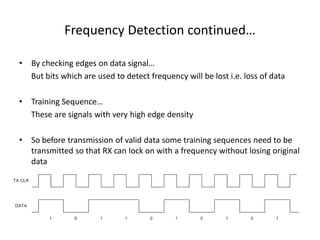

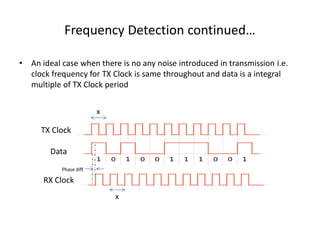

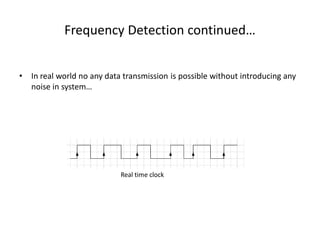

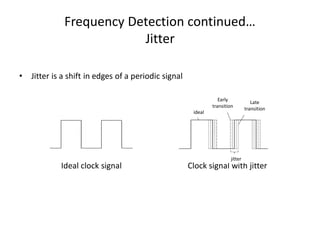

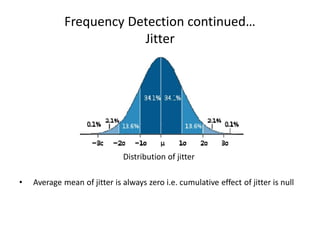

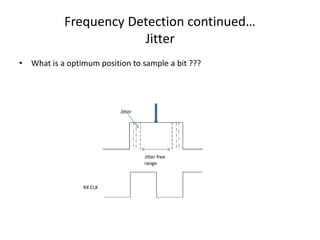

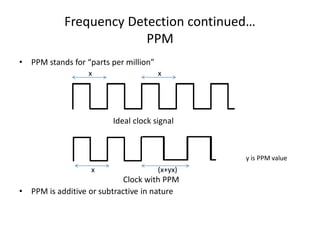

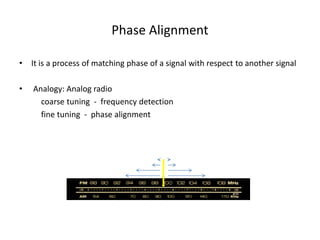

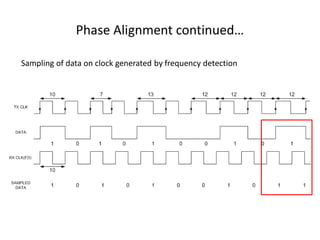

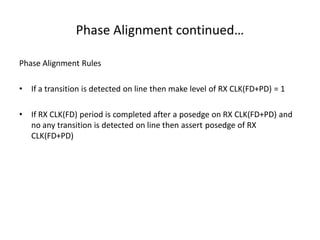

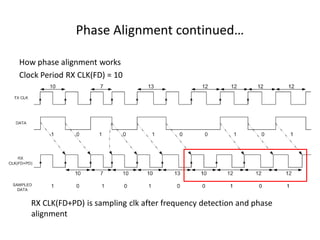

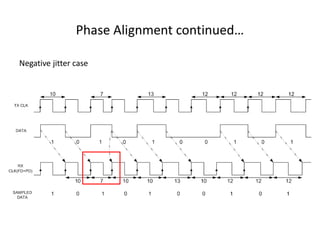

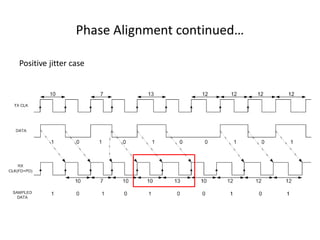

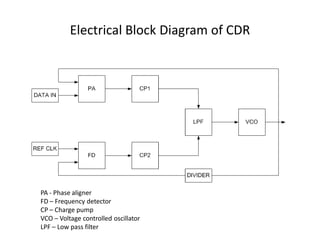

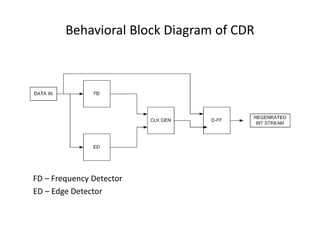

The document discusses the behavioral modeling of clock and data recovery (CDR) devices, highlighting the importance of serial communication over parallel communication due to issues like skew and inter-symbol interference. It explains the functions of CDR, including frequency detection and phase alignment, necessary for recovering data from high-speed serial interfaces in the absence of a dedicated clock signal. The document also covers challenges such as jitter and ppm (parts per million) that affect data transmission and methods like encoding to manage these issues.