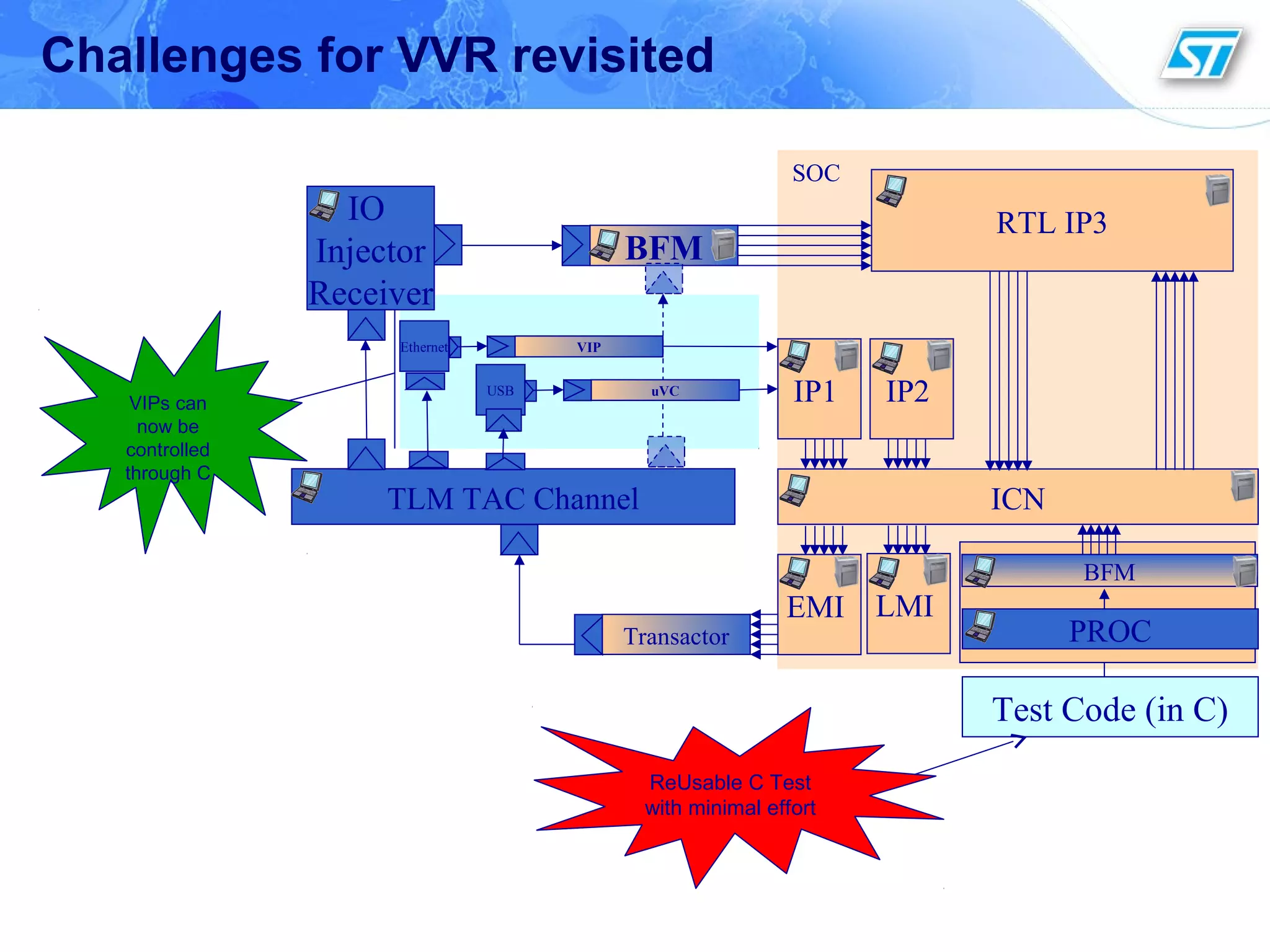

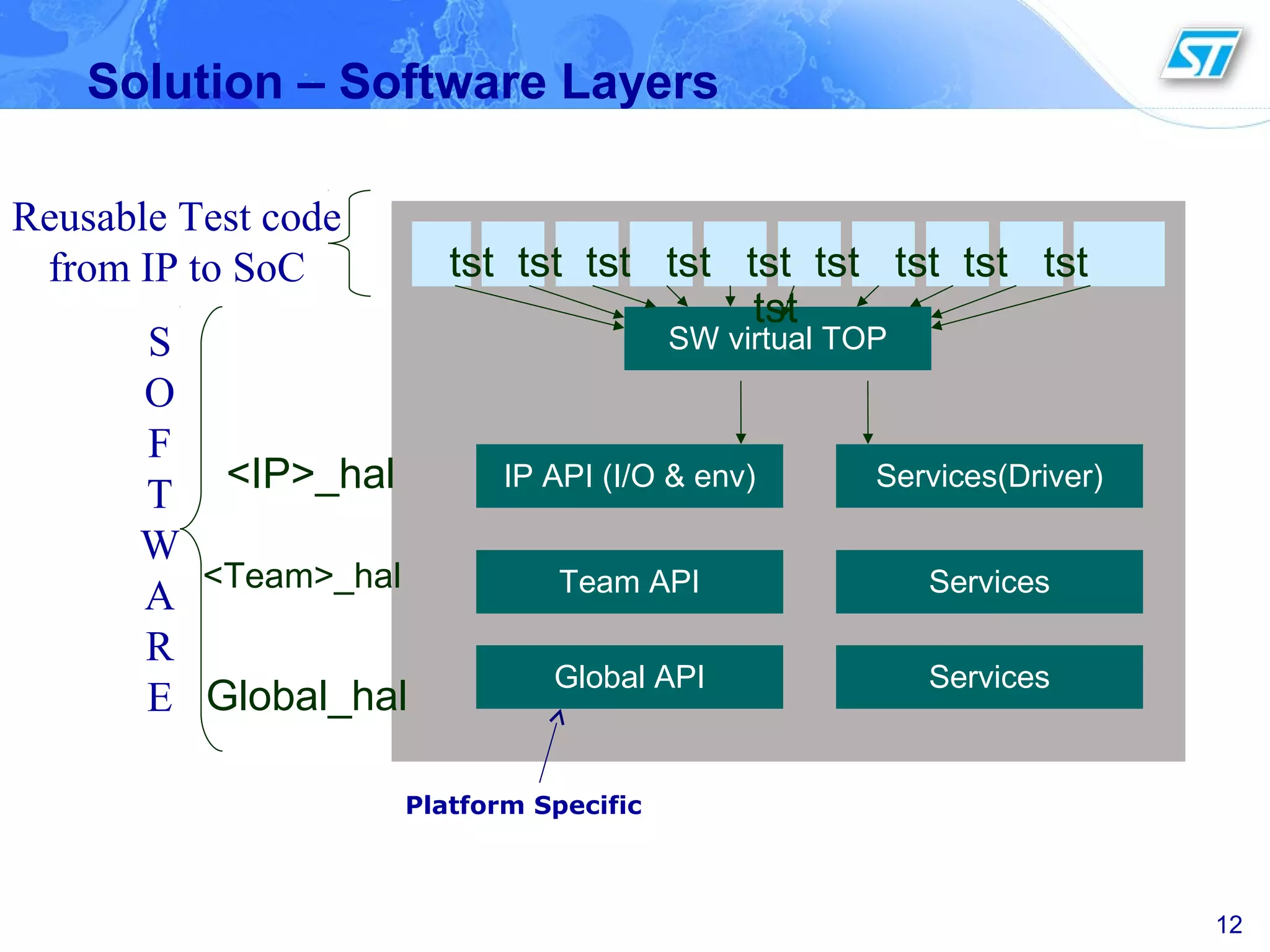

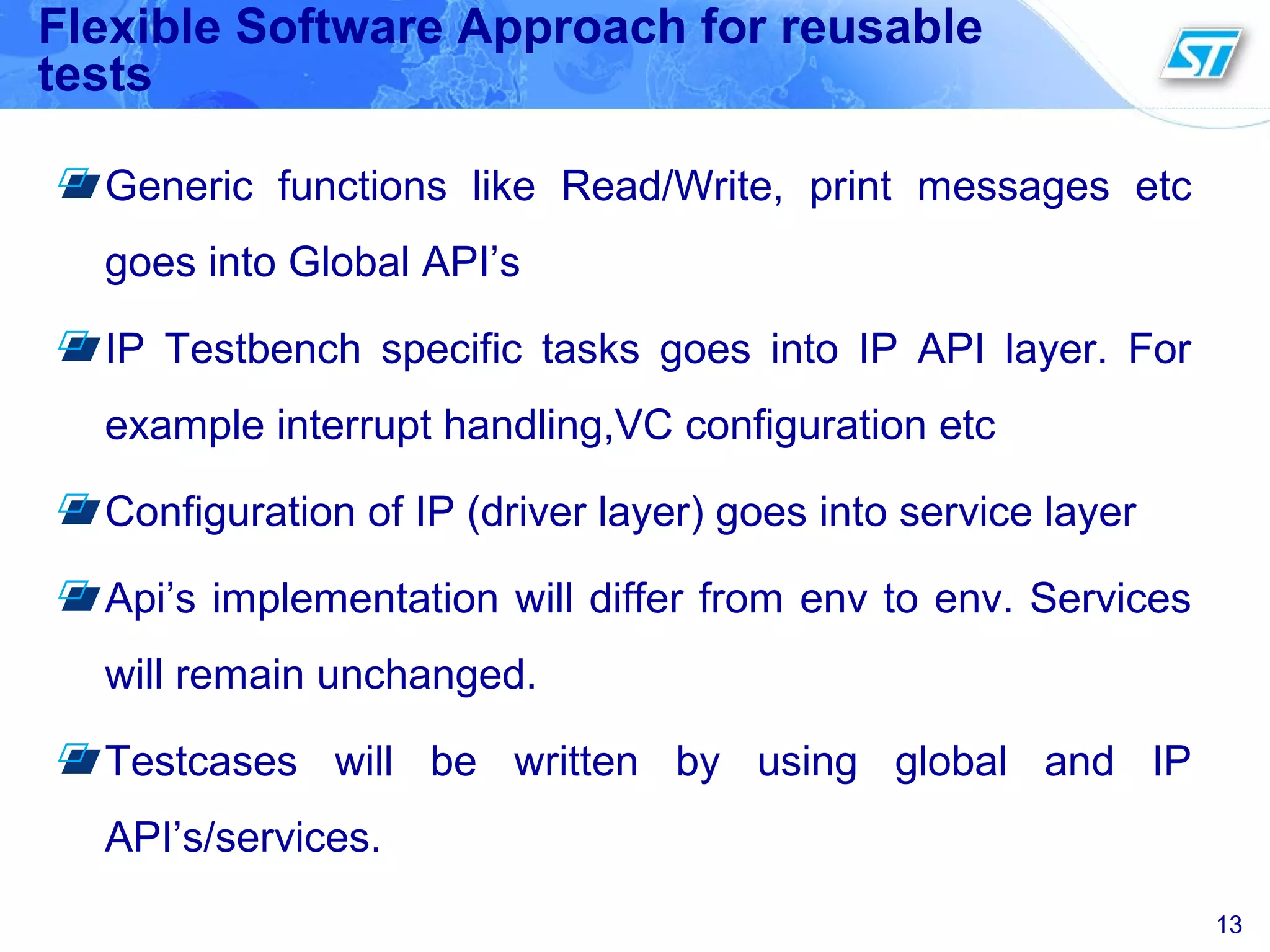

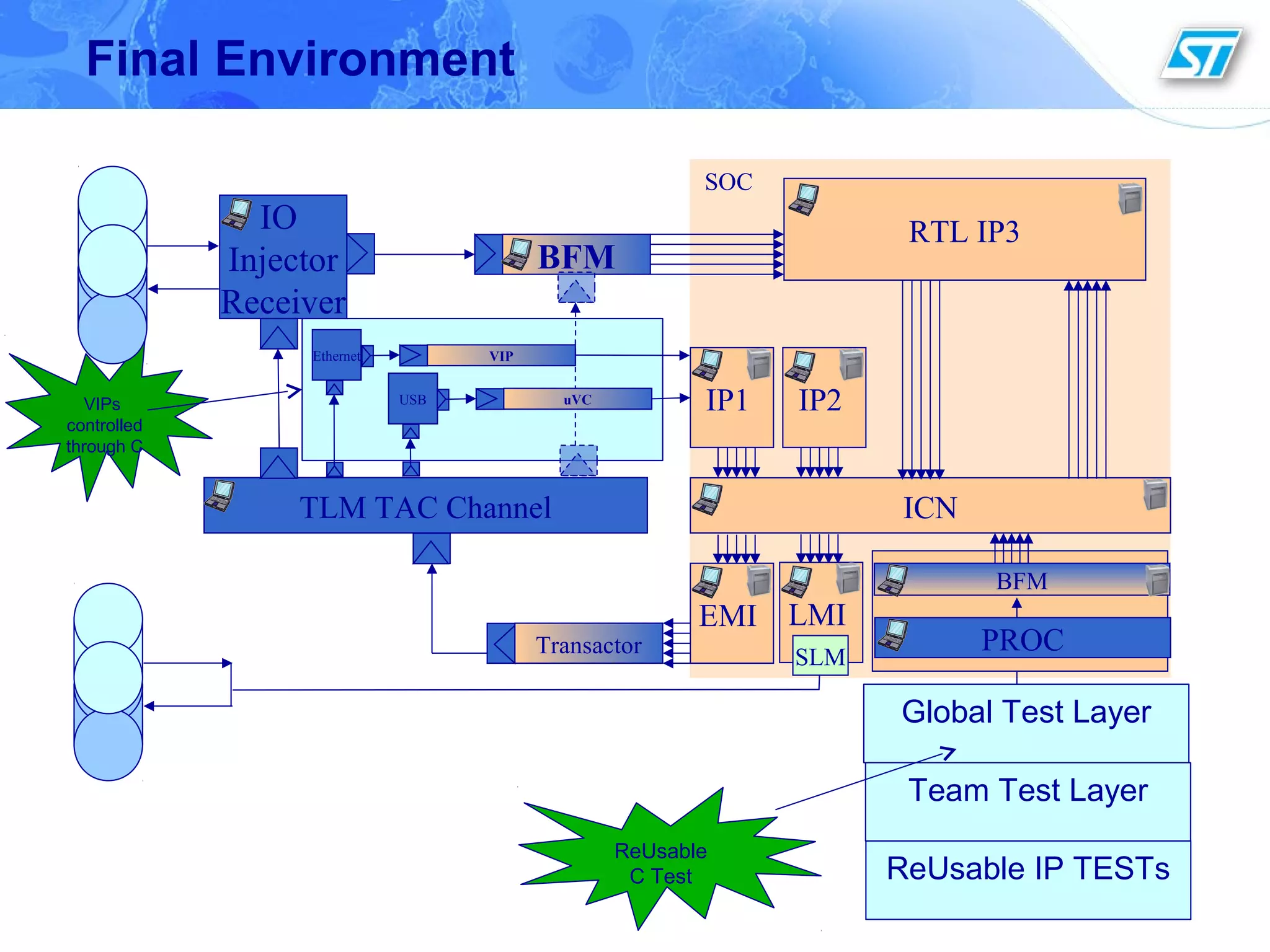

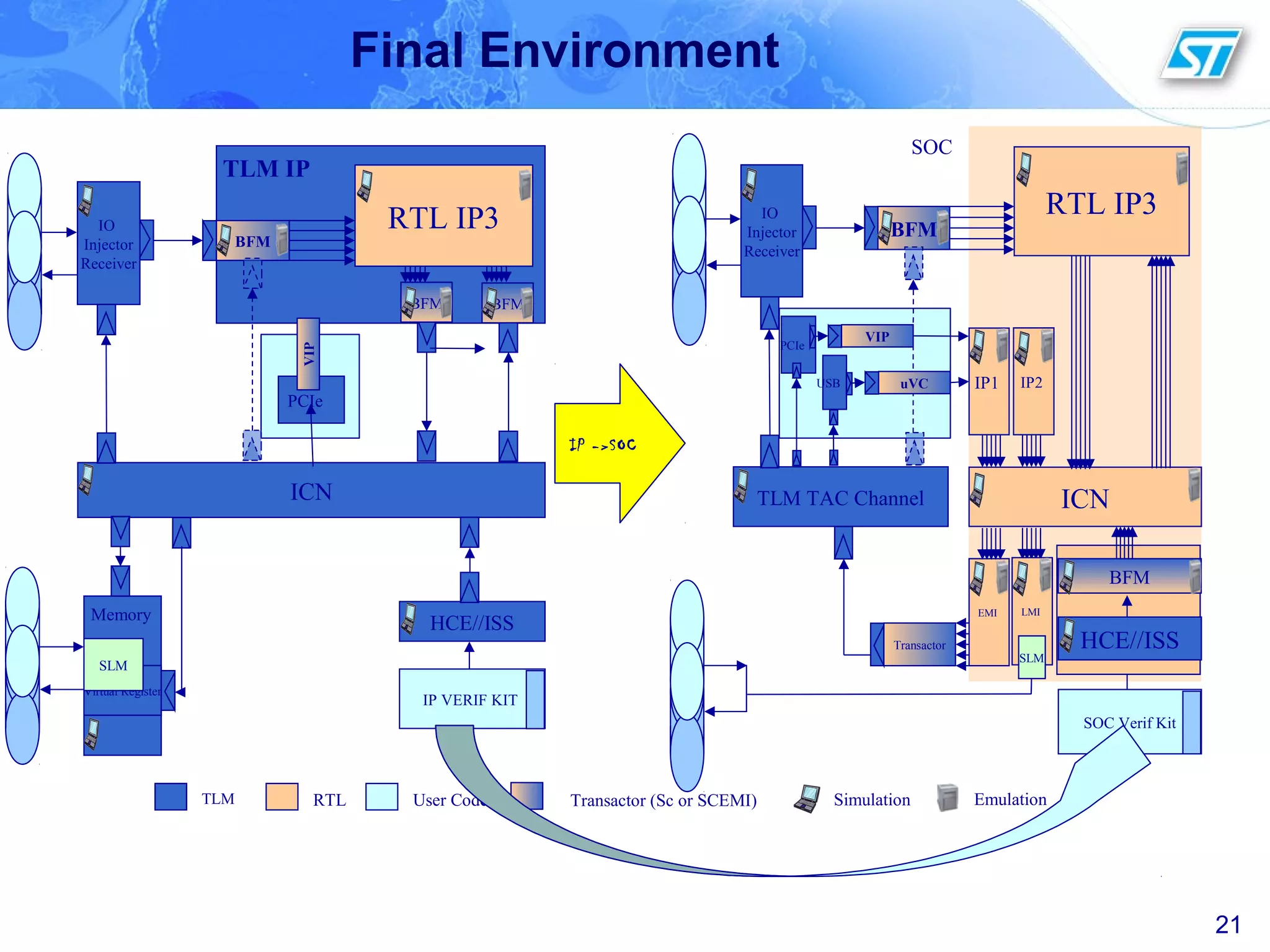

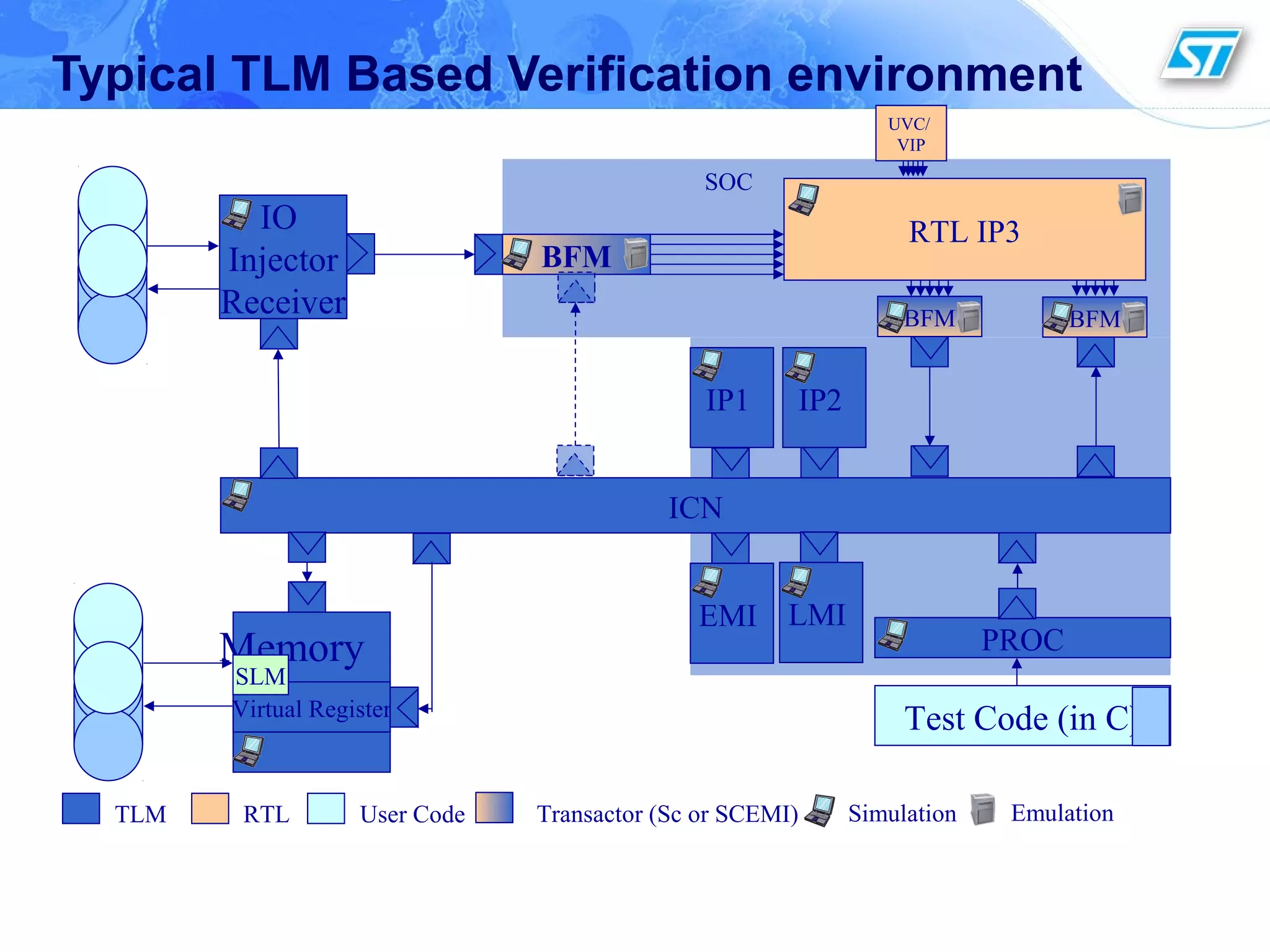

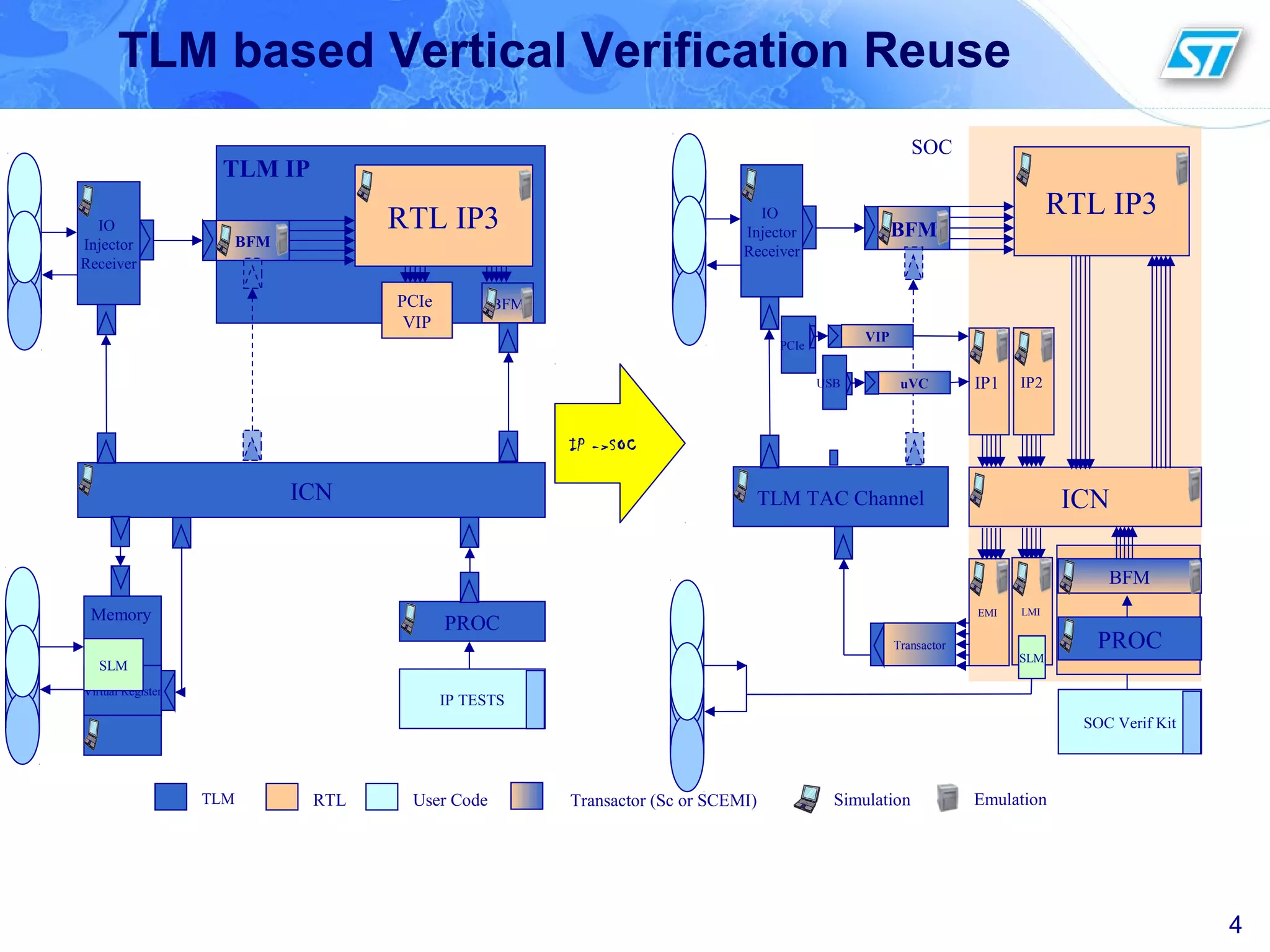

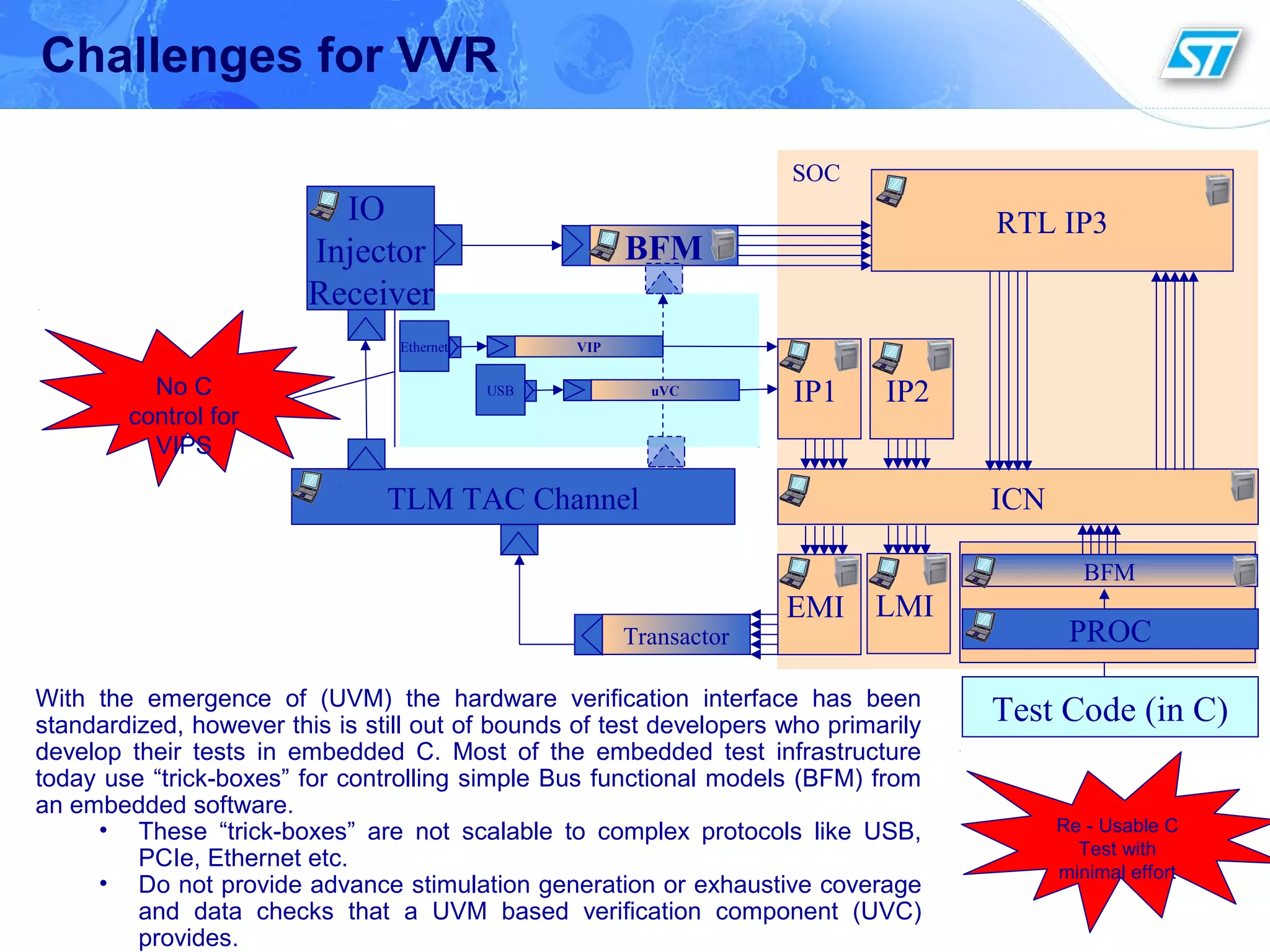

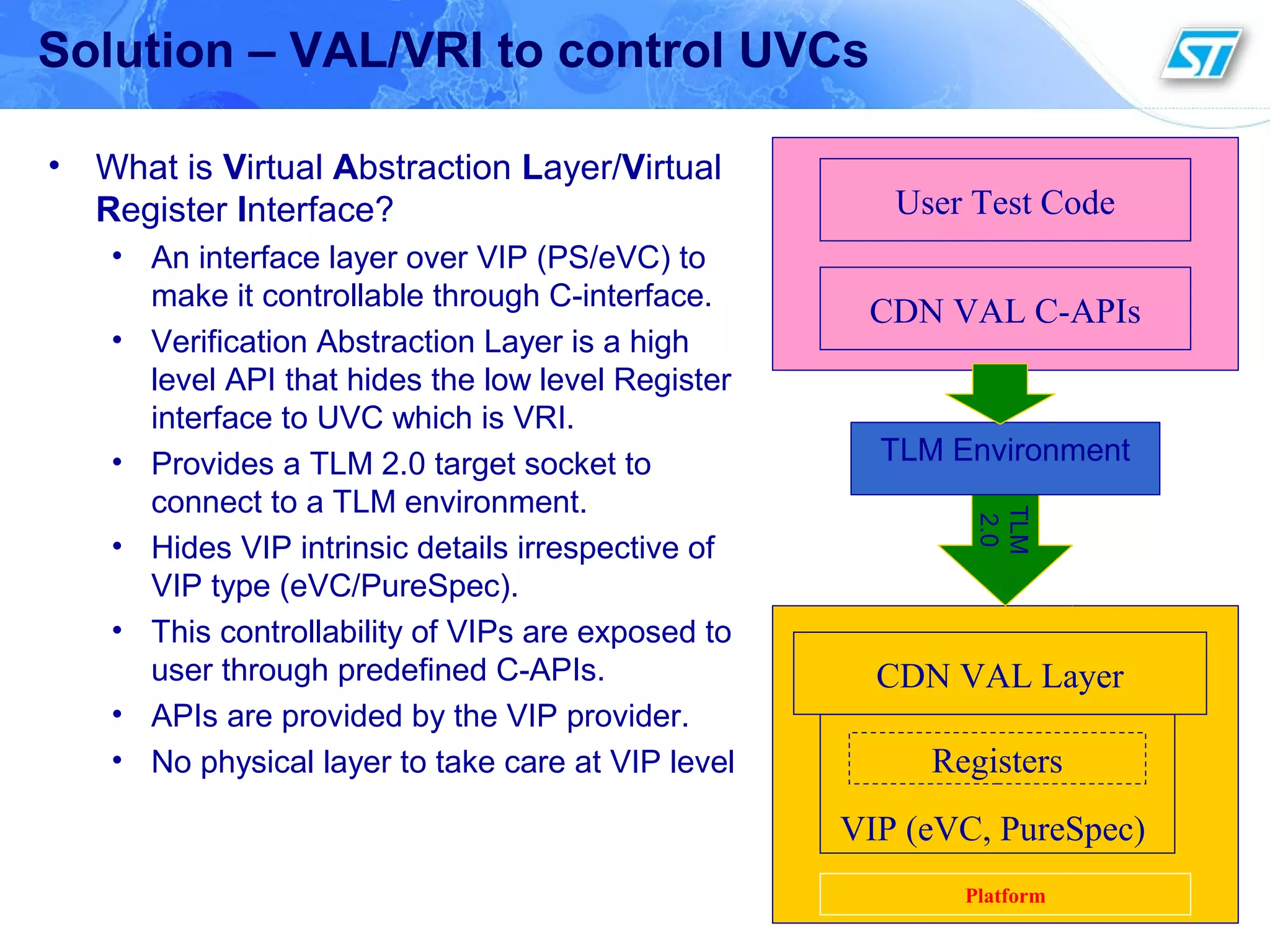

The document discusses a TLM (Transaction-Level Modeling) based software control methodology for vertical verification reuse (VVR) in System-on-Chip (SoC) designs. It outlines the challenges faced in traditional verification approaches and introduces solutions such as a Virtual Abstraction Layer (VAL) and Virtual Register Interface (VRI) that allow for enhanced control and reusability of verification components in C test environments. The proposed framework aims to reduce verification complexity and time while enabling efficient test case development across different platforms.

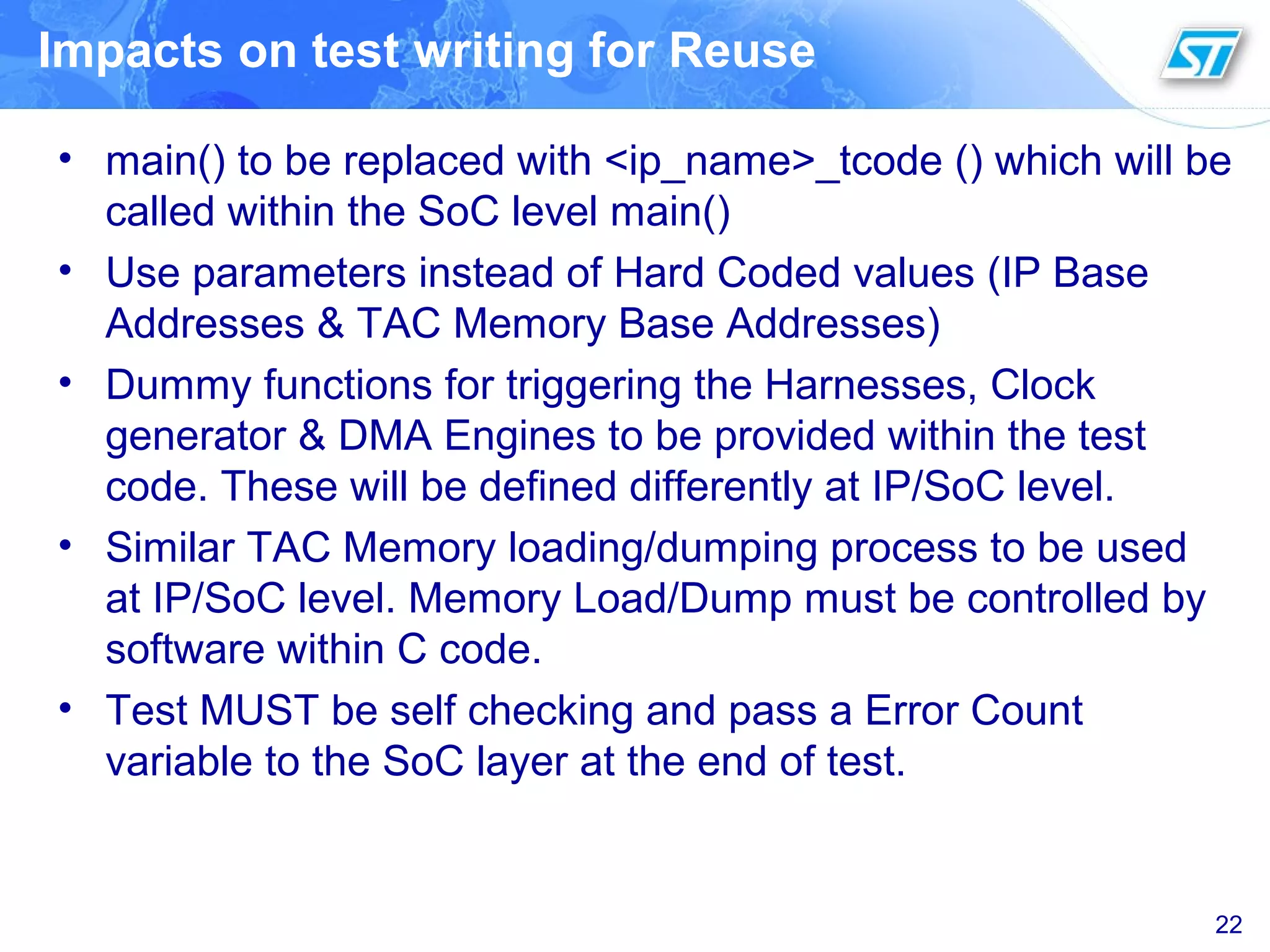

![Test case using CDN-VRI-API

void sata_main_test()

{

struct sata_register_htod_t reg_htod_info;

reg_htod_info.c_bit = 1;

reg_htod_info.features = 0x21;

reg_htod_info.secnum = 0x22;

reg_htod_info.cyllow = 0x23;

reg_htod_info.cylhigh = 0x24;

reg_htod_info.drvhead = 0xFF;

reg_htod_info.secnum_exp = 0x25;

reg_htod_info.cyllow_exp = 0x26;

reg_htod_info.cylhigh_exp = 0x27;

reg_htod_info.features_exp = 0x28;

reg_htod_info.seccnt = 0x29;

reg_htod_info.seccnt_exp = 0x2A;

reg_htod_info.hob = 0;

reg_htod_info.srst = 1;

reg_htod_info.ien = 0;

//call SATA VAL API

vri_sata_register_htod(0, ®_htod_info, 1);

}

static int error_count = 0;

// main()

int esw_main(int argc, char * argv[])

{

// COB-init, boot, lmi-init,

error_count = pre_test_config();

// sata specific test

error_count = sata_main_test();

// test post checking

error_count = test_post_processing();

return error_count;

}

void vri_sata_register_htod(

unsigned long instance_num,

struct sata_register_htod_t *reg_htod_info,

unsigned long frame_count)

{

// implementation

}

Main test SATA Main test (using CDN-API)

CDN-VRI-API](https://image.slidesharecdn.com/dvclube2102-tlmbasedsoftwarecontrolofuvcsforverticalverificationreuse-krishnakumar-150911073316-lva1-app6891/75/DvClub-2102-tlm-based-software-control-of-uvcs-for-vertical-verification-reuse-krishna-kumar-10-2048.jpg)