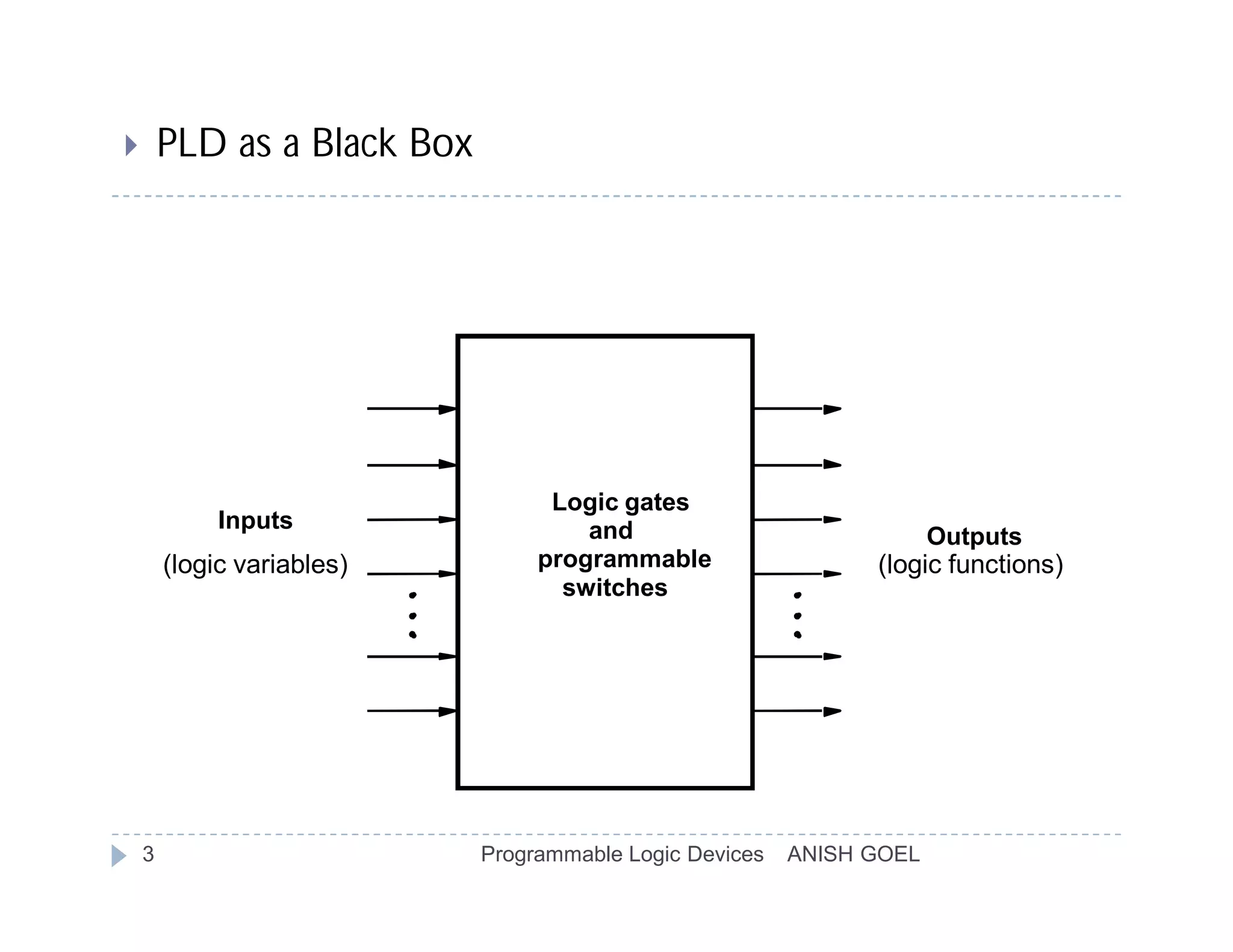

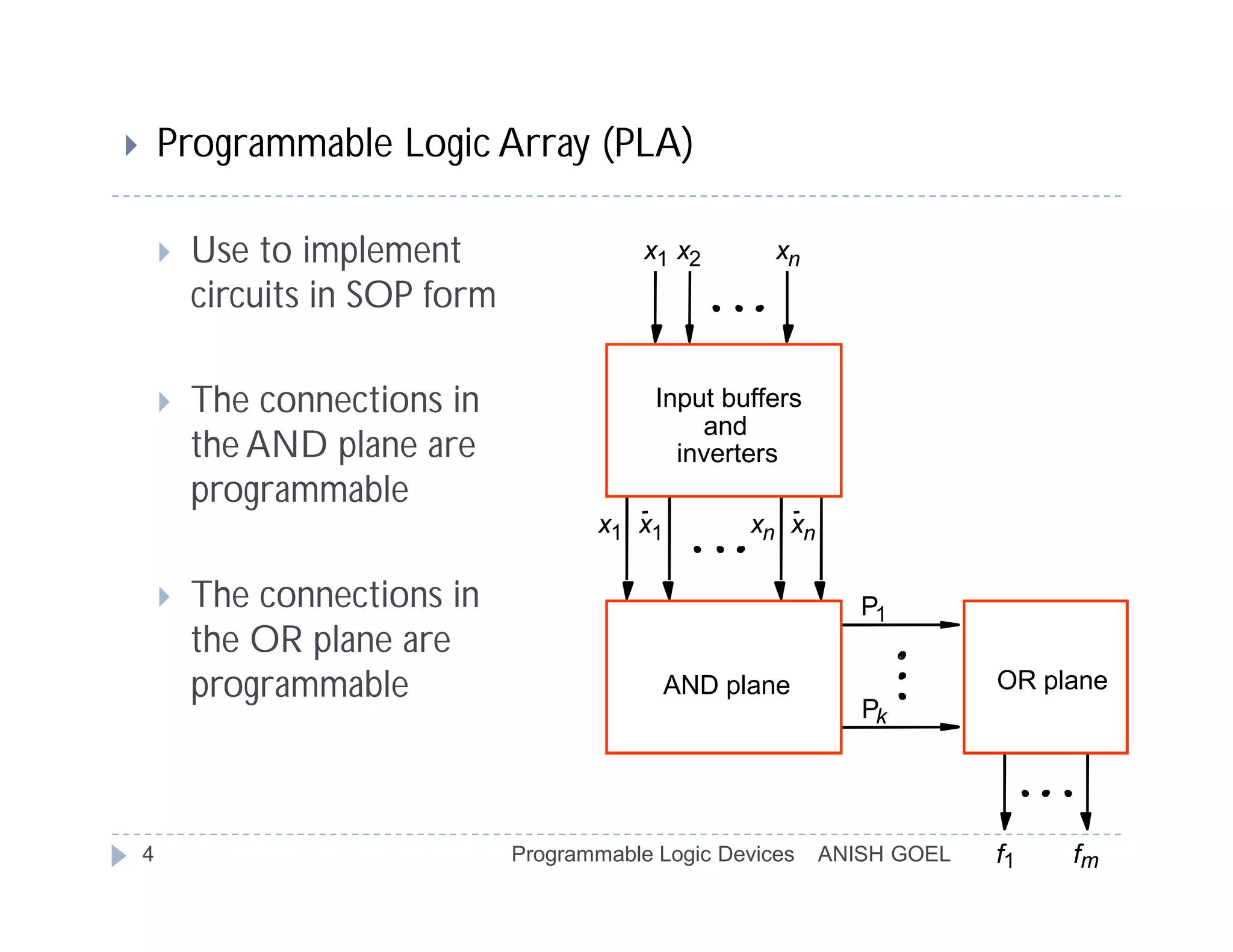

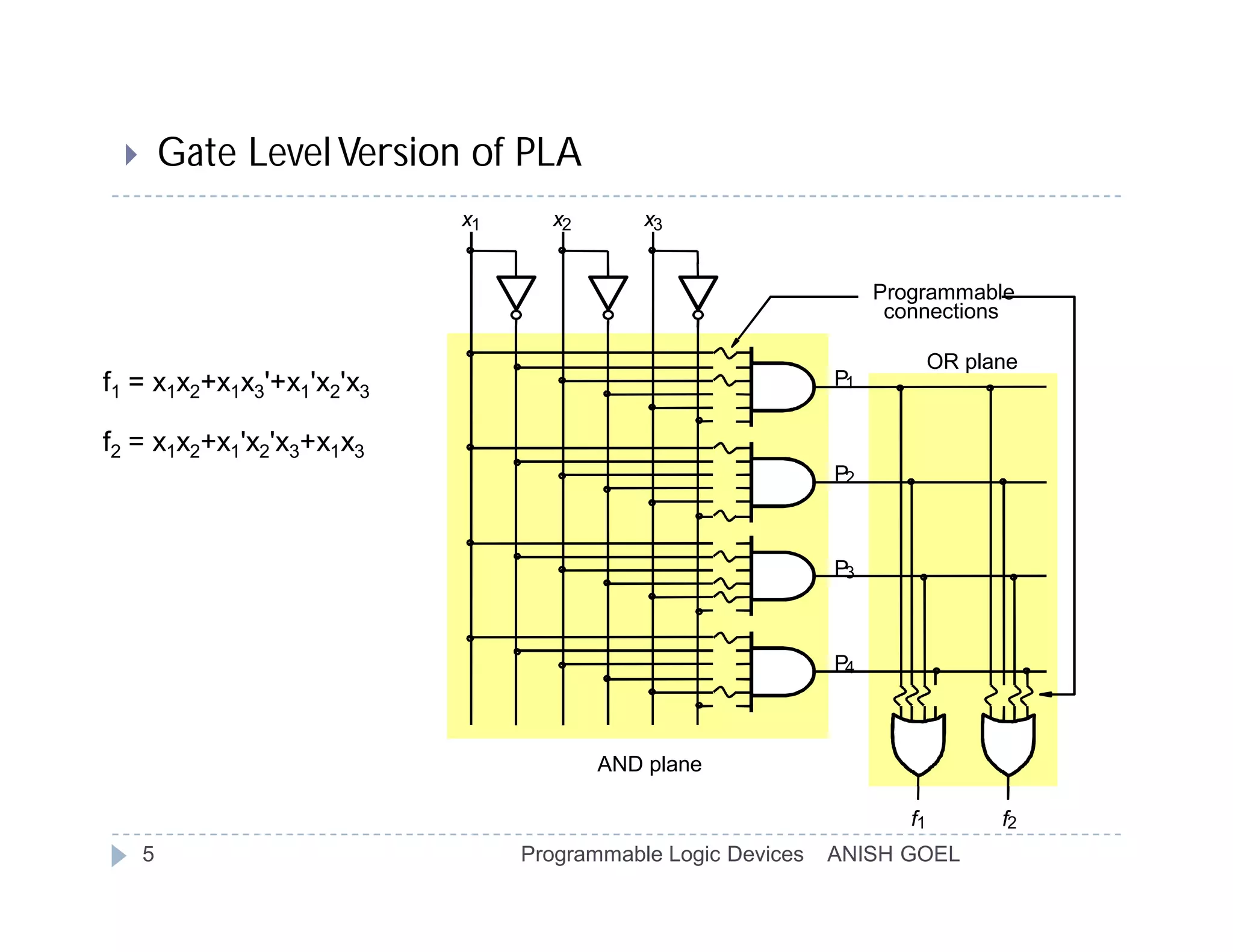

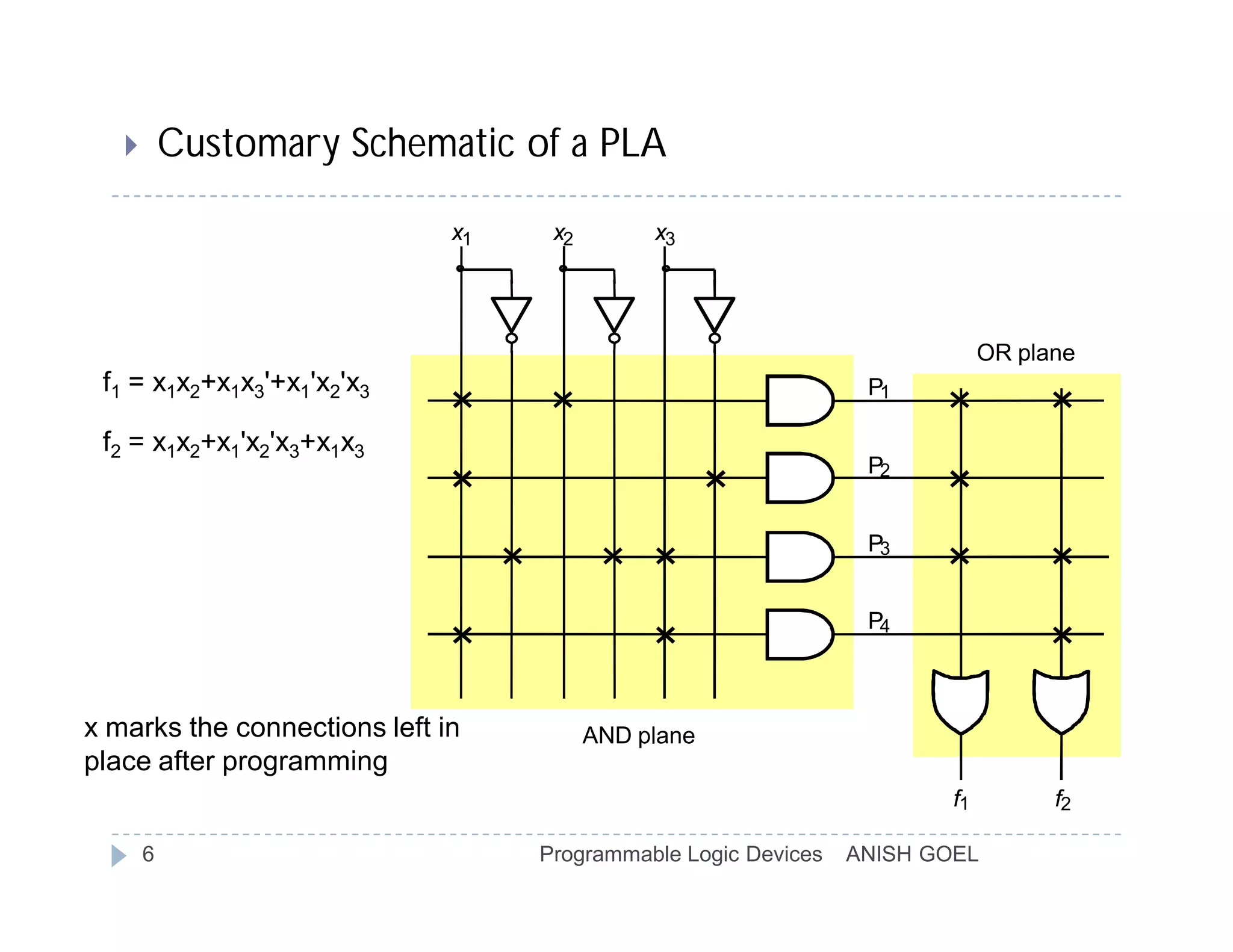

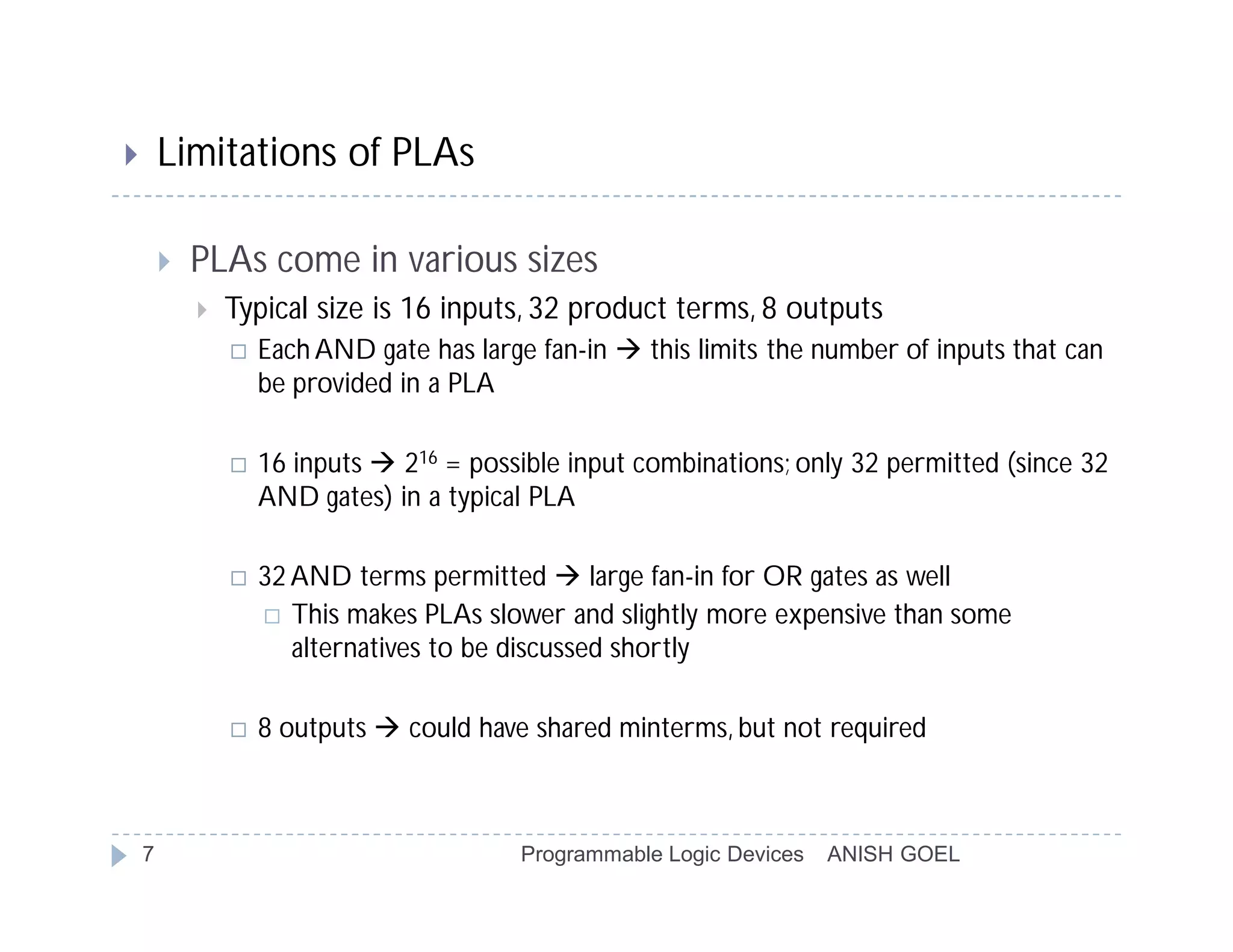

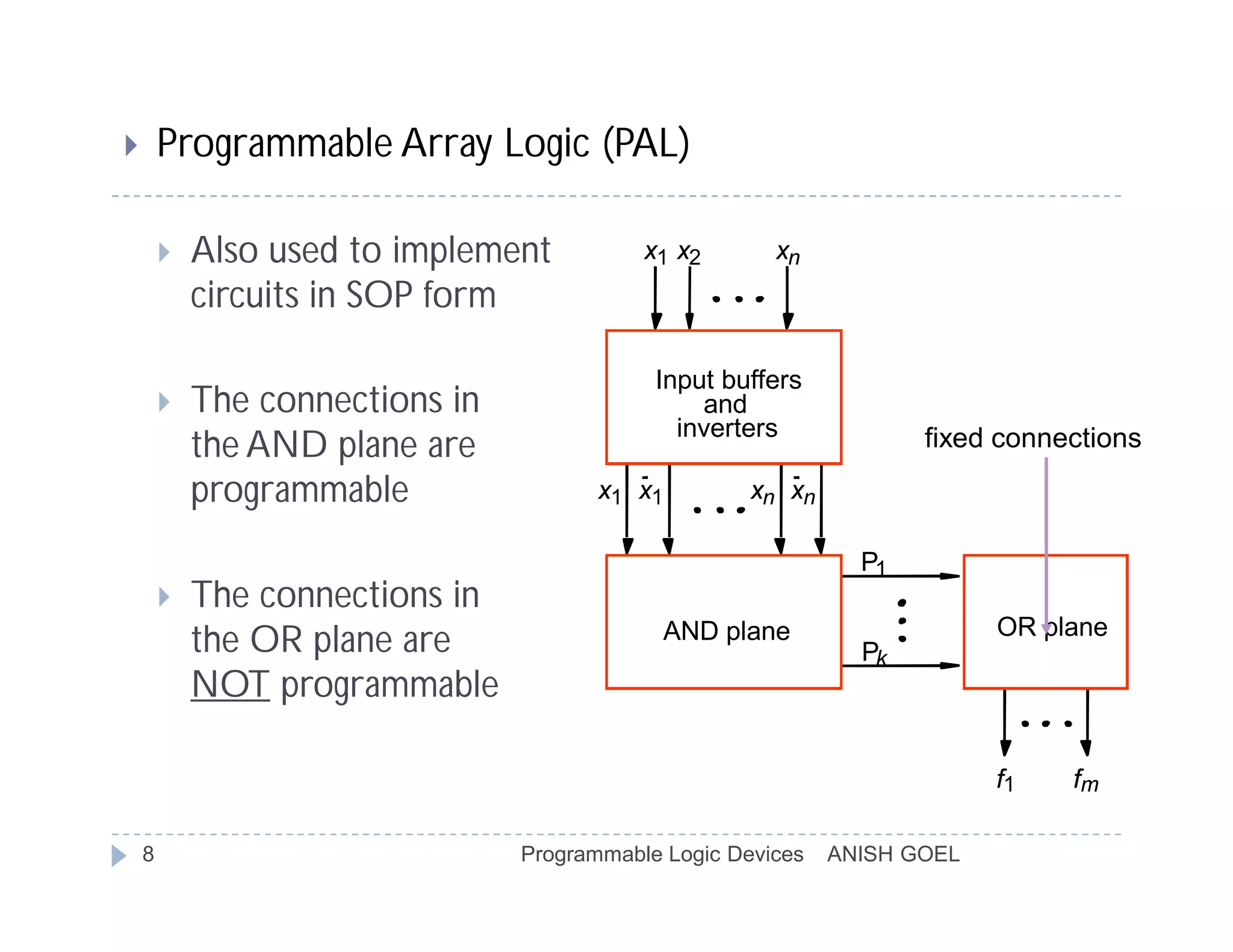

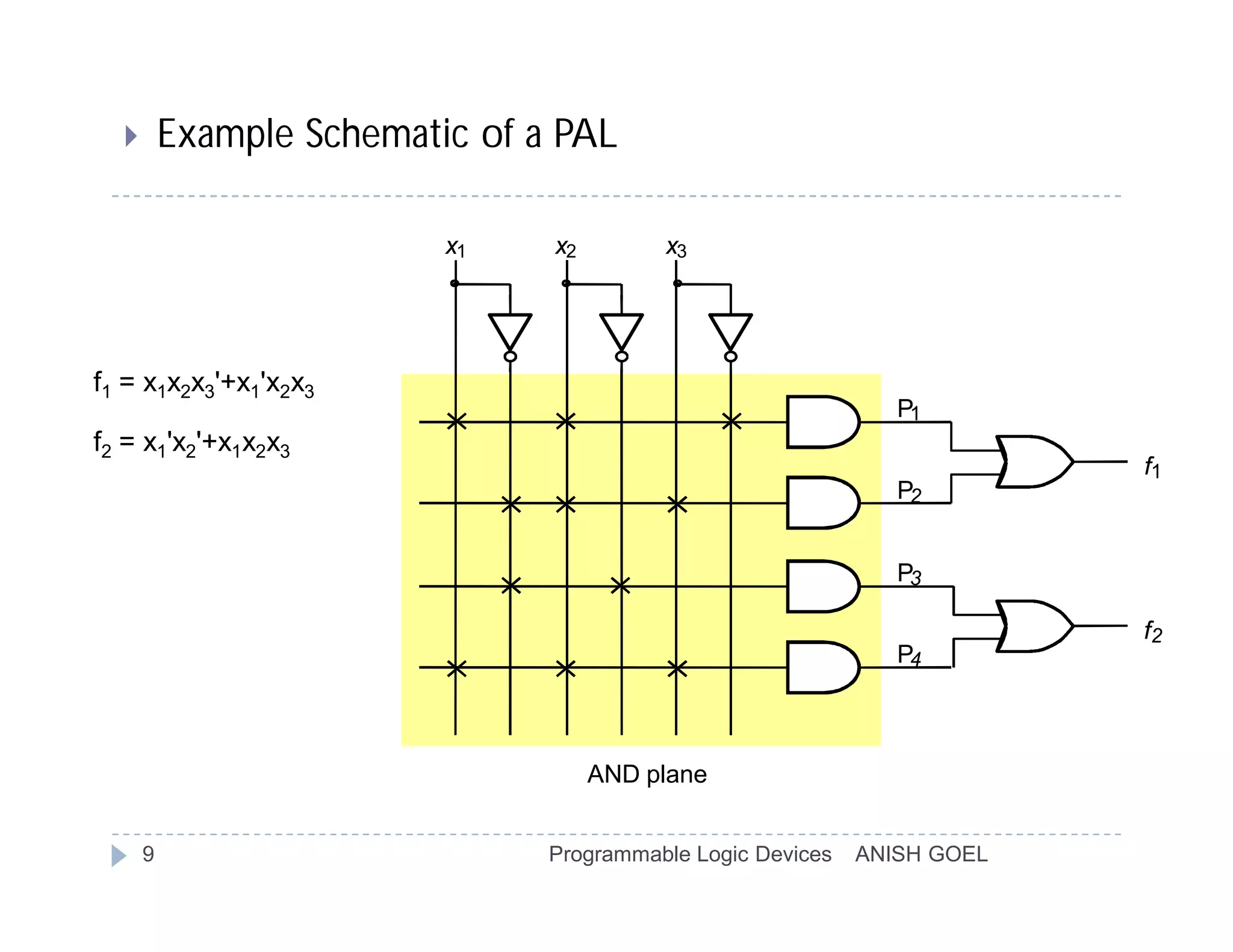

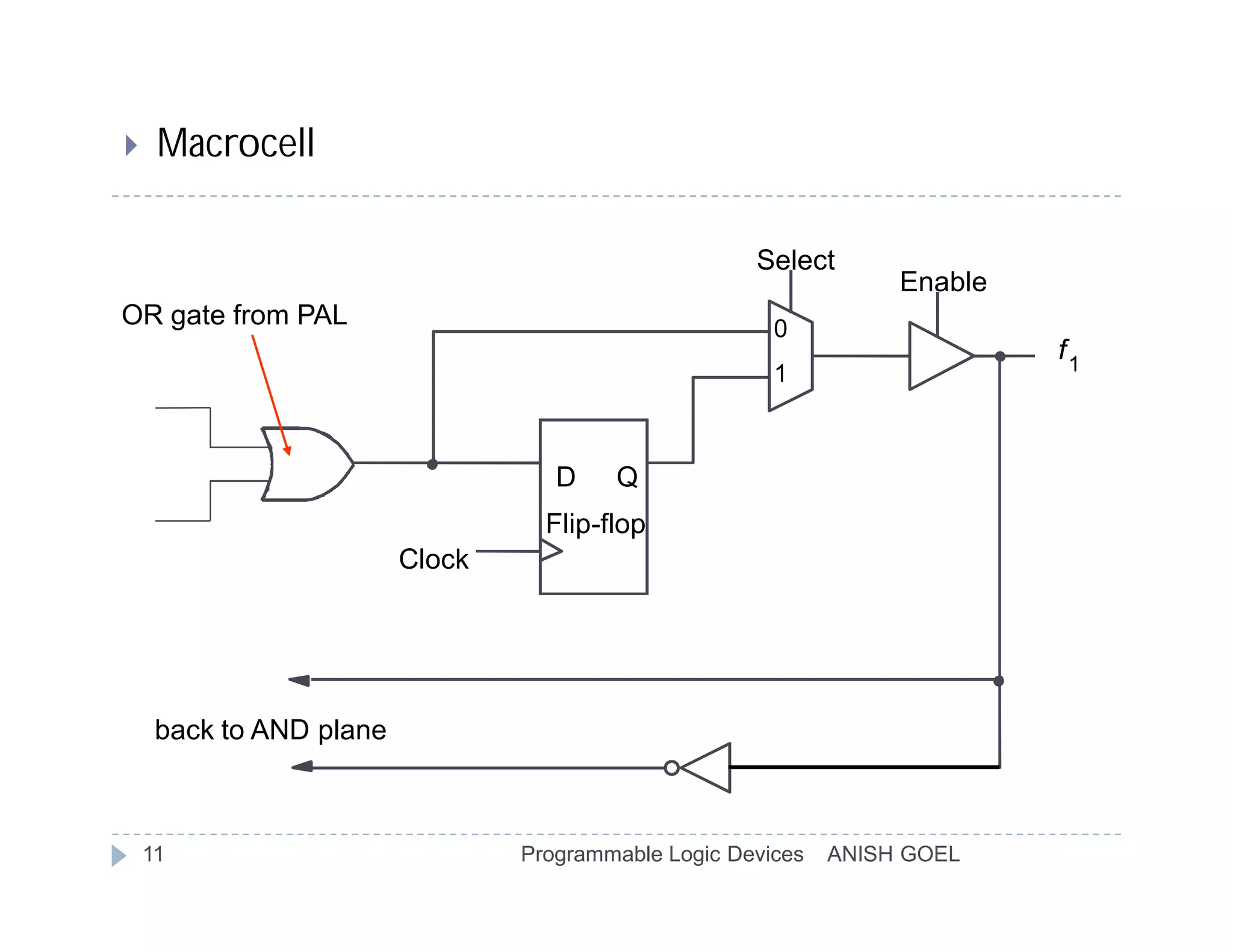

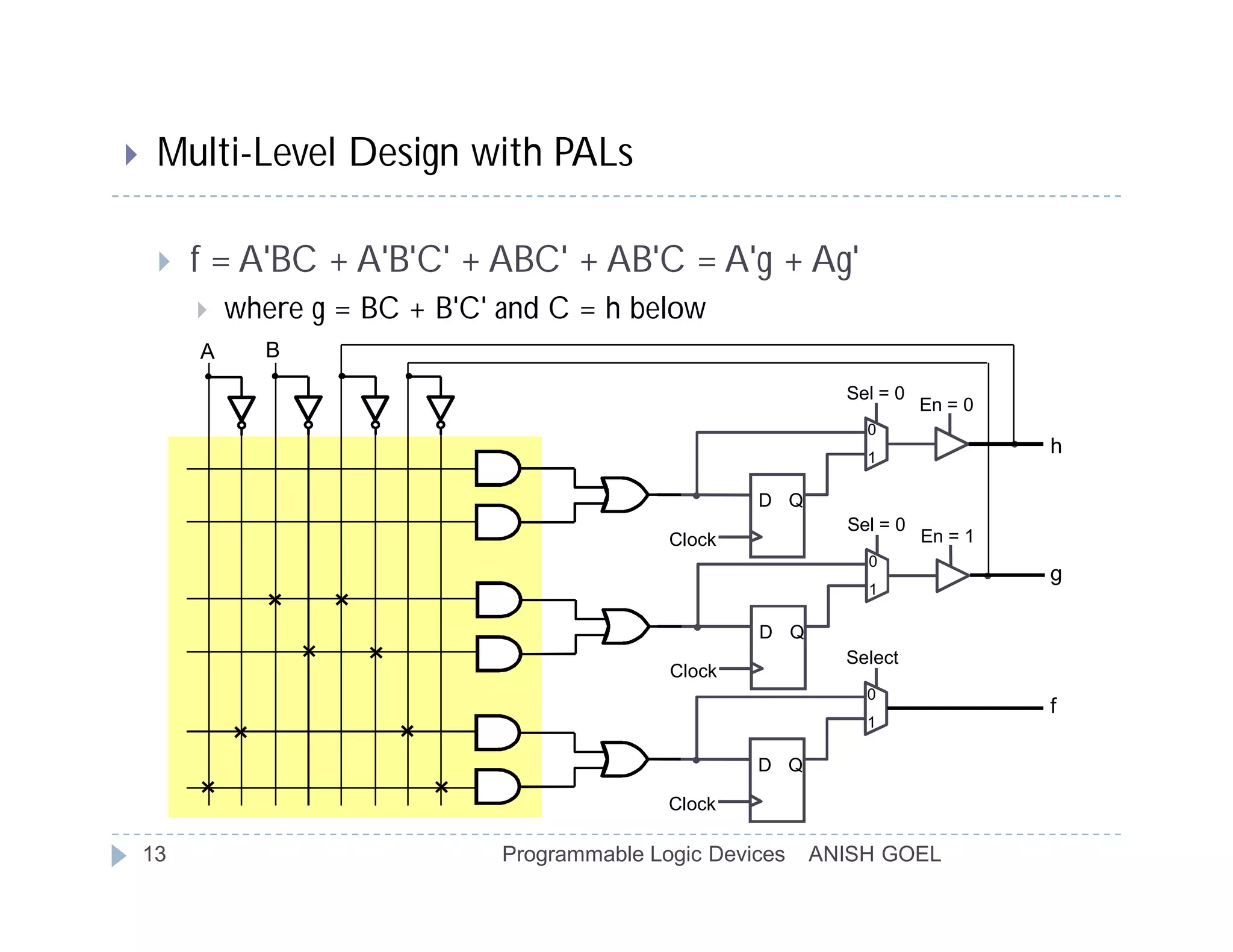

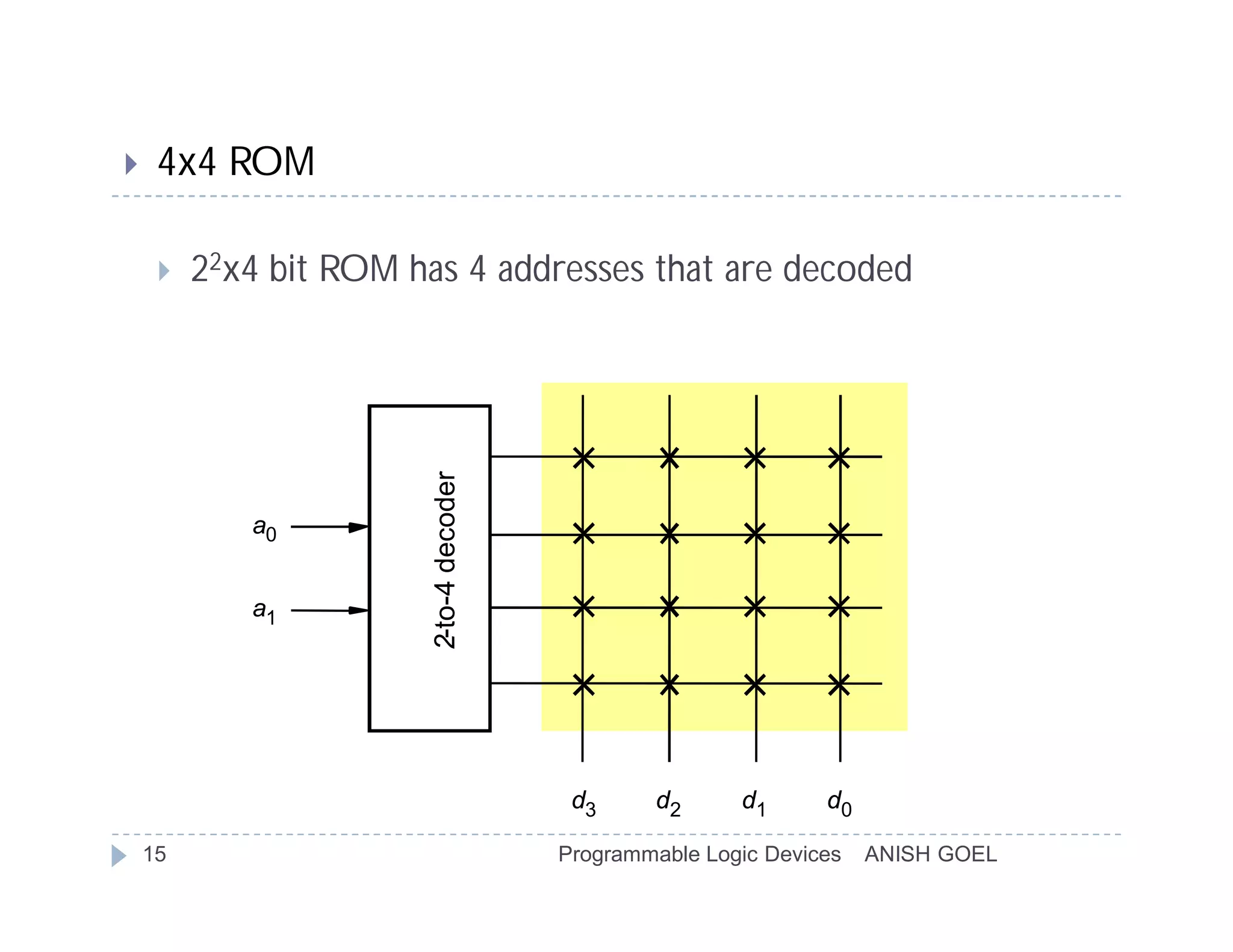

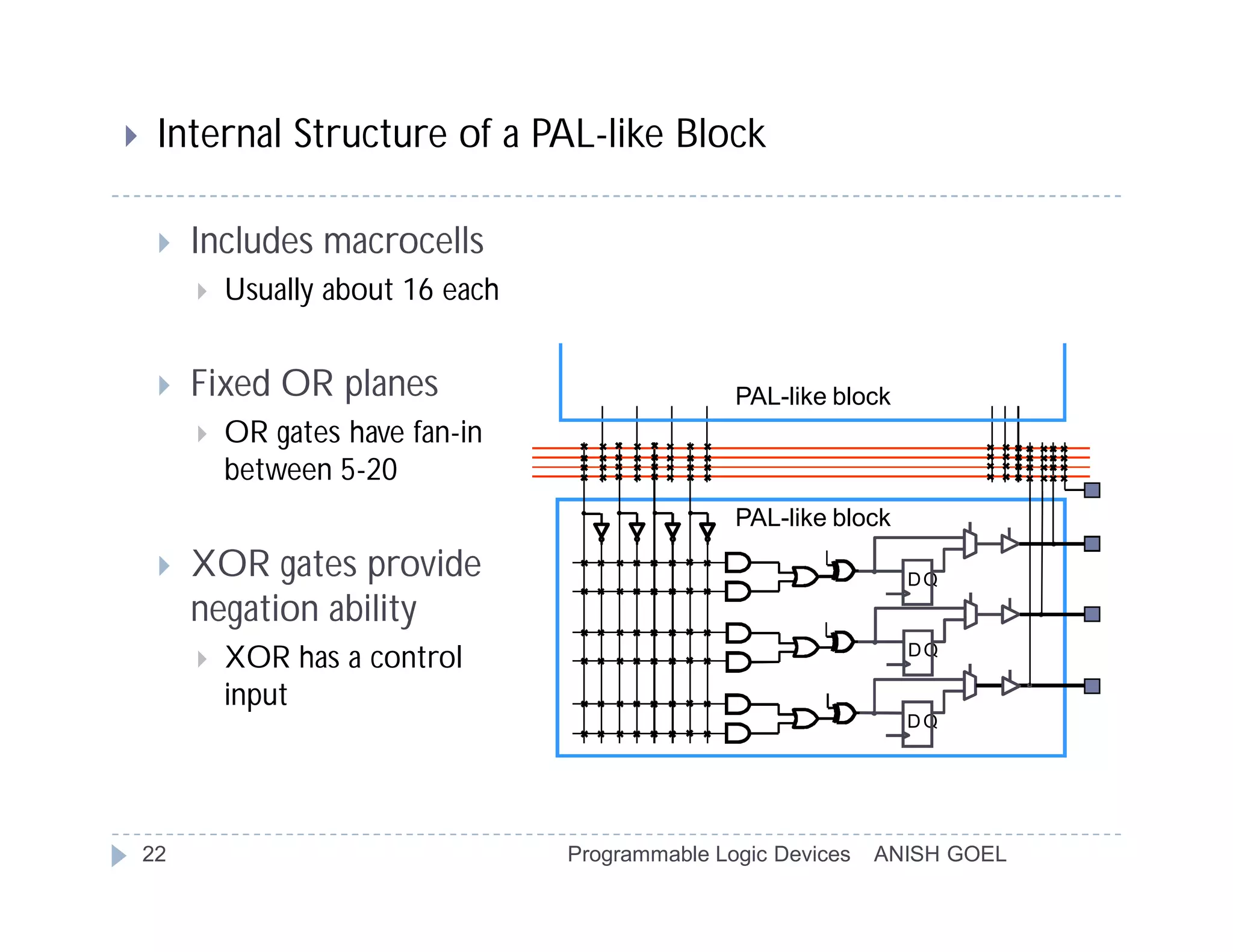

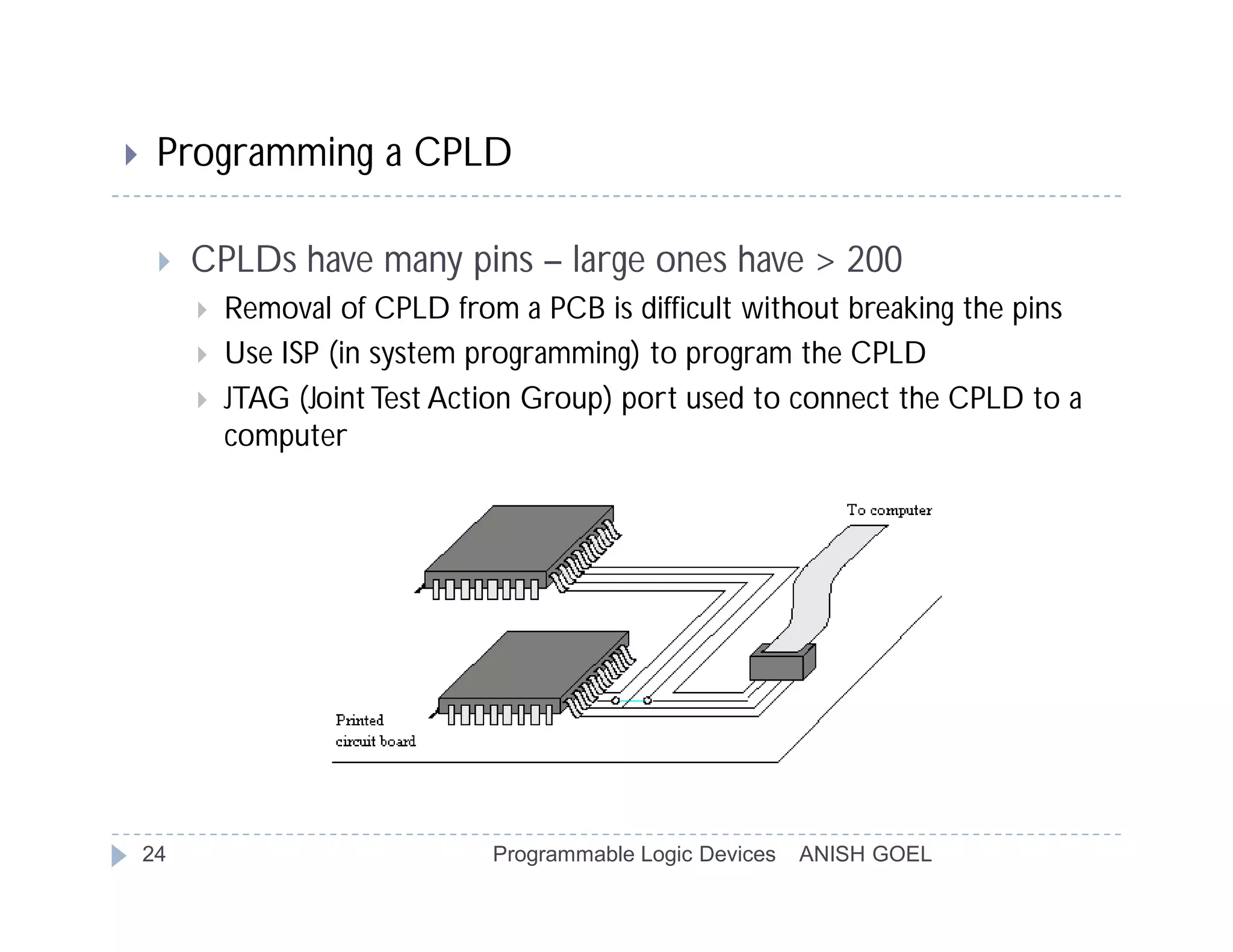

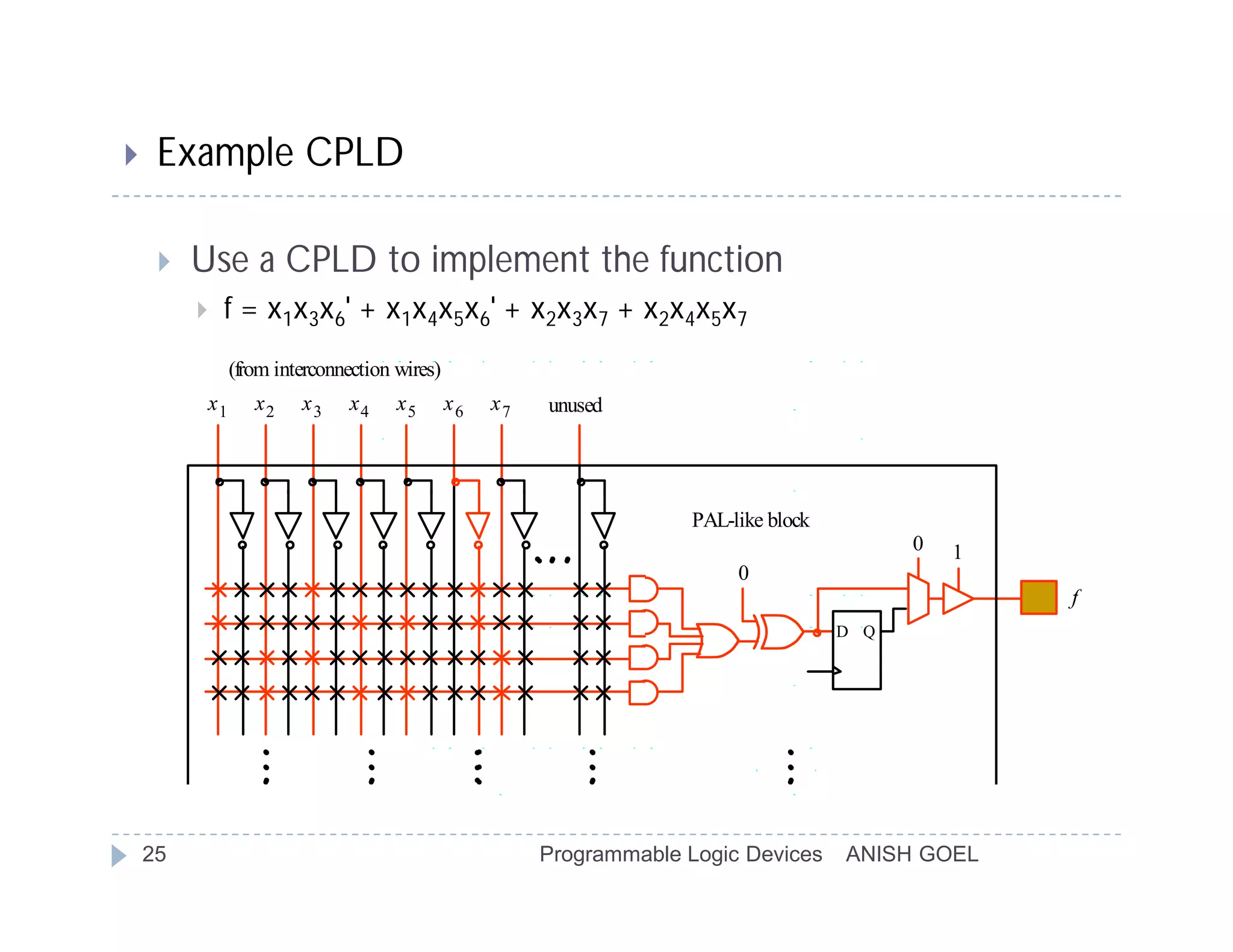

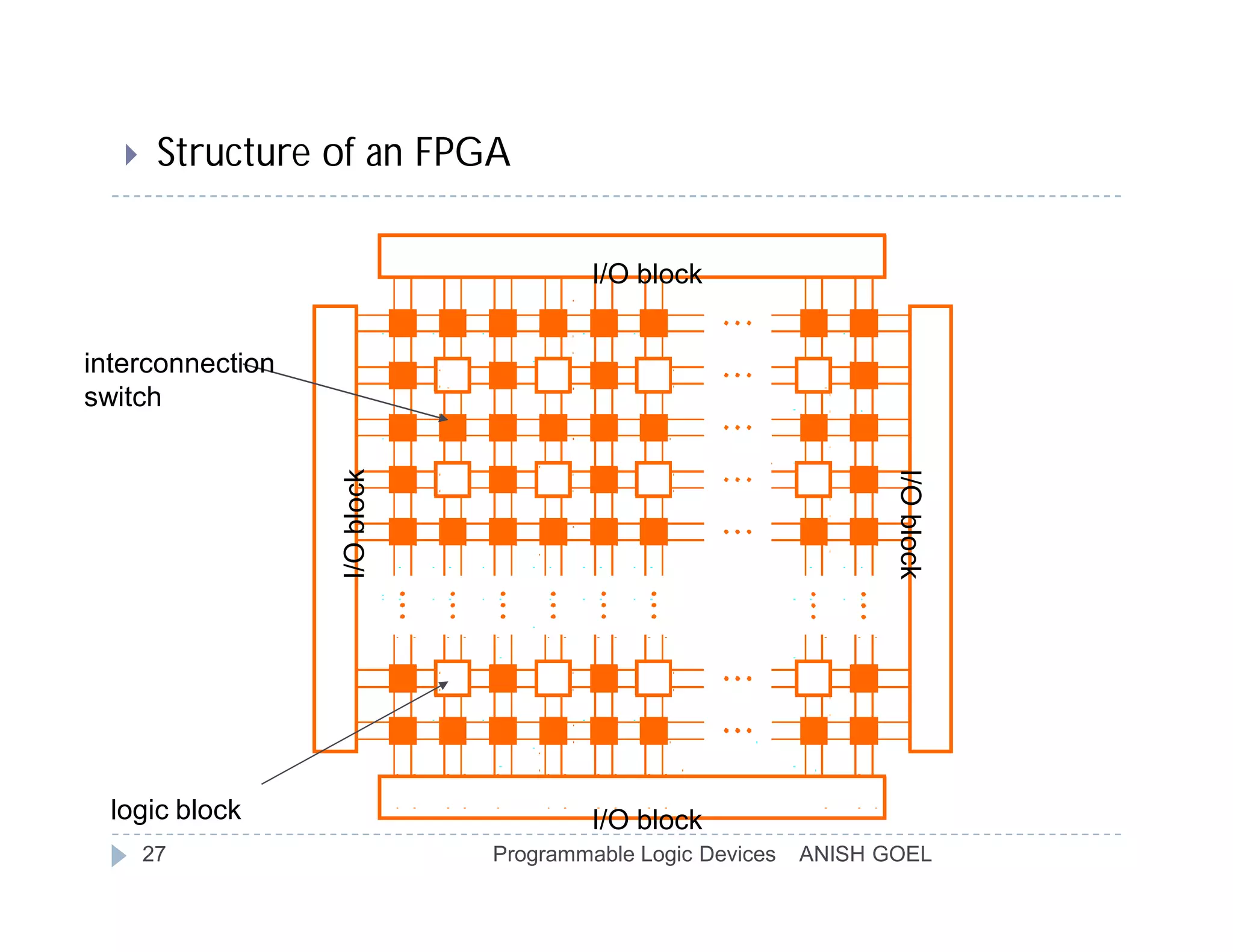

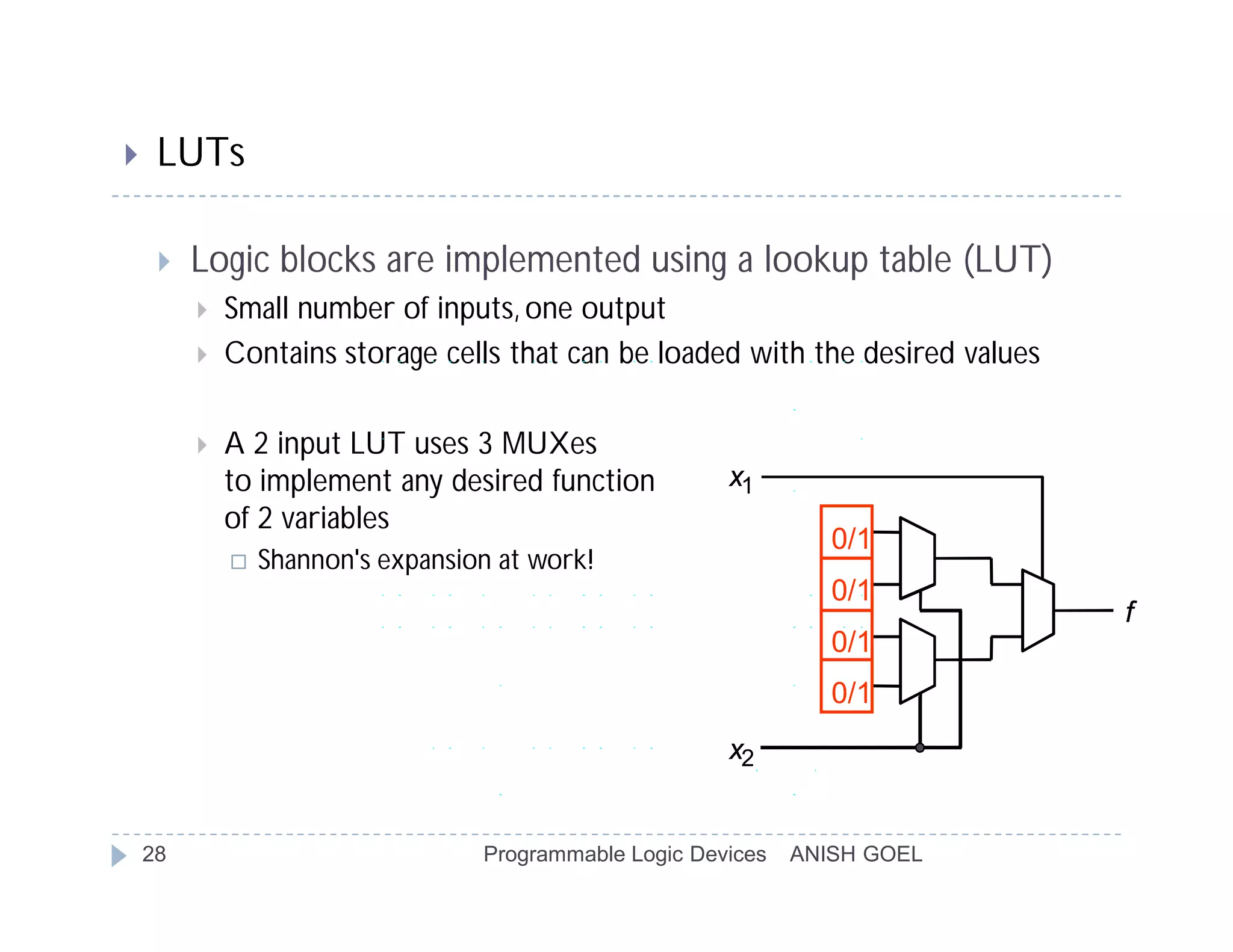

The document discusses several types of programmable logic devices (PLDs) including PLAs, PALs, ROMs, CPLDs, and FPGAs. It provides details on how PLAs and PALs are structured, including their AND planes and OR planes. PALs are simpler than PLAs but less flexible. The document also describes how PALs can be used for multi-level logic design using macrocells and feedback to the AND plane. ROMs have a fixed AND plane and programmable OR plane to map logic functions. SPLDs refer to simpler PLDs like PLAs, PALs, and ROMs.