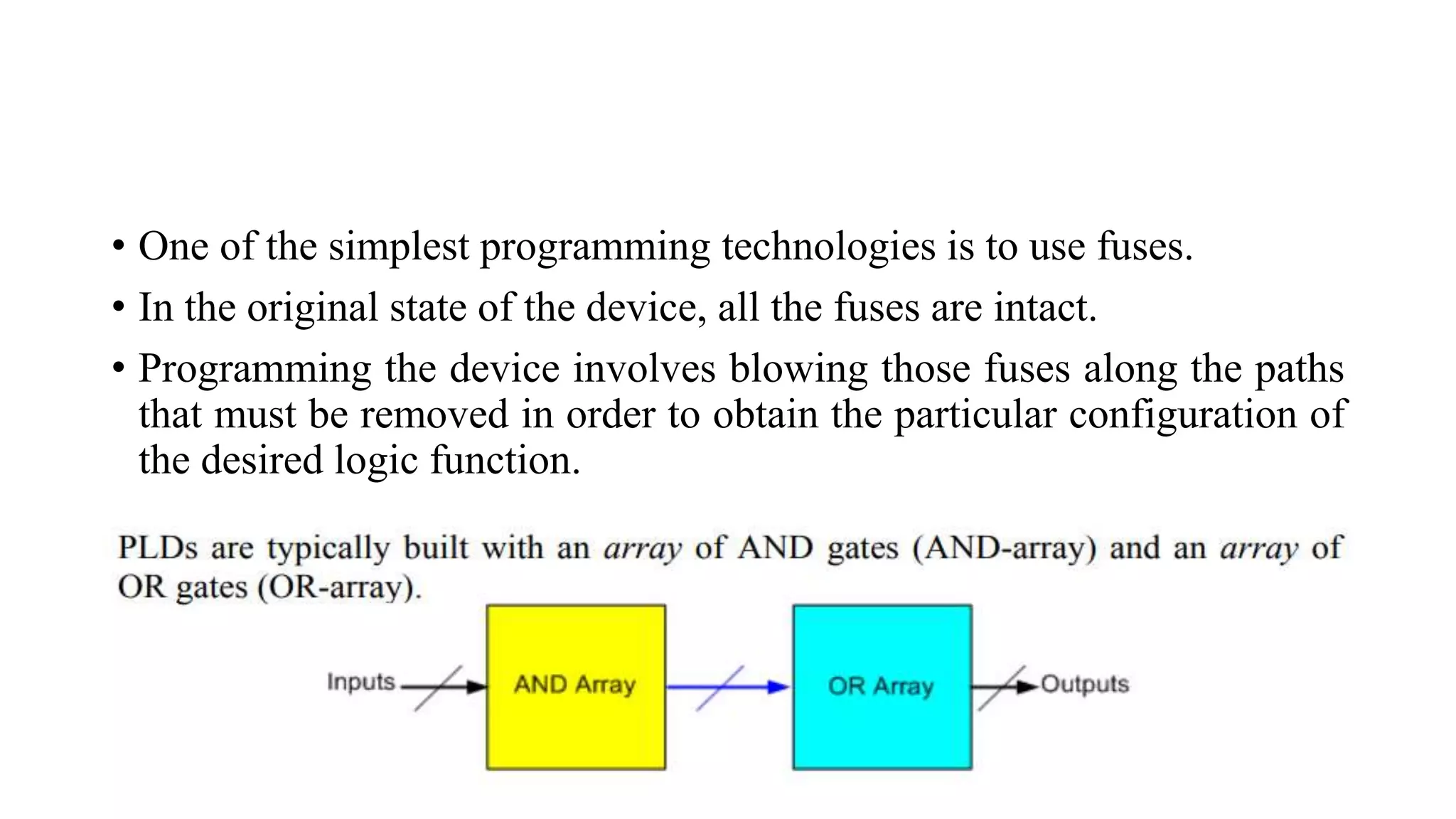

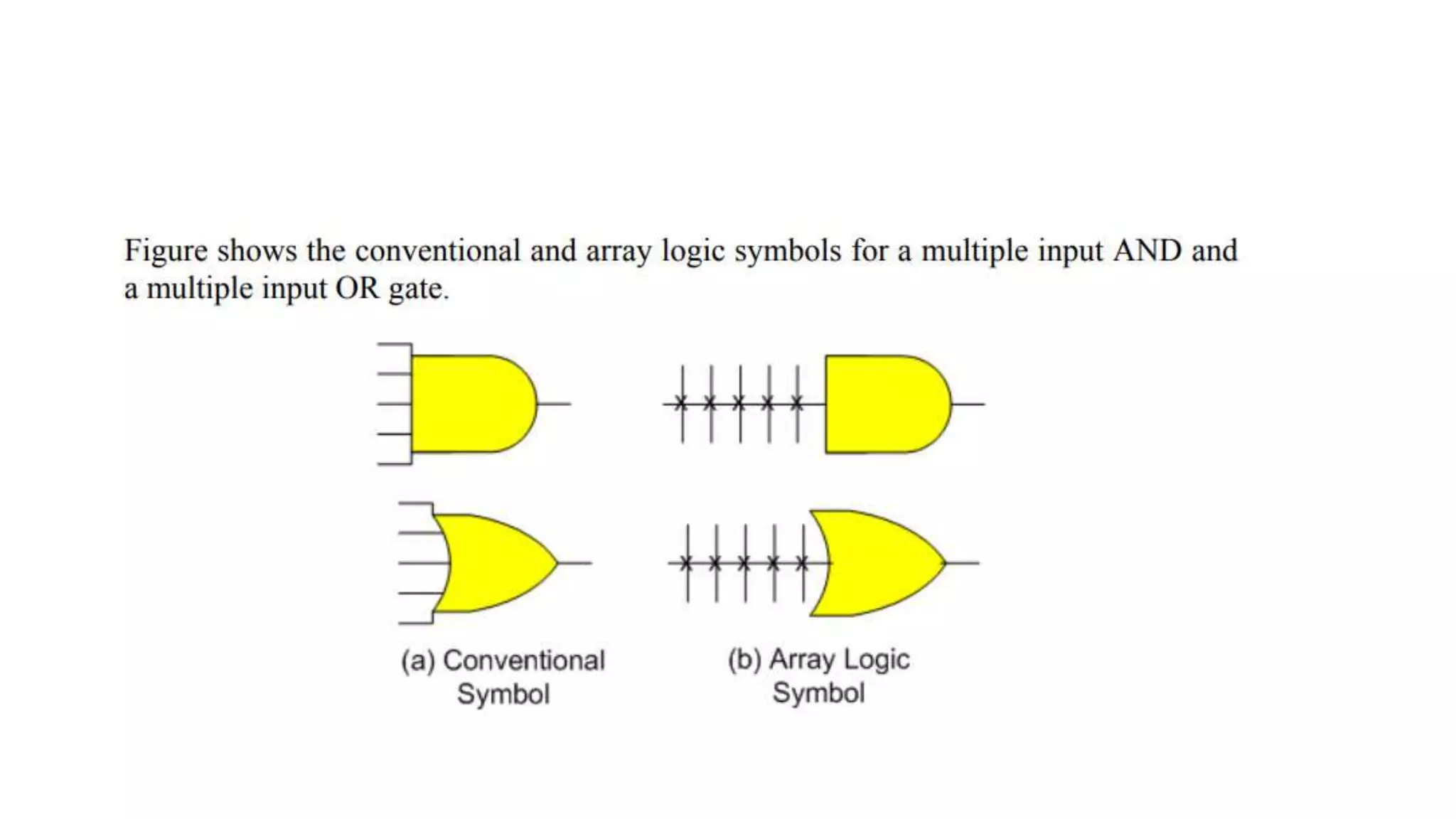

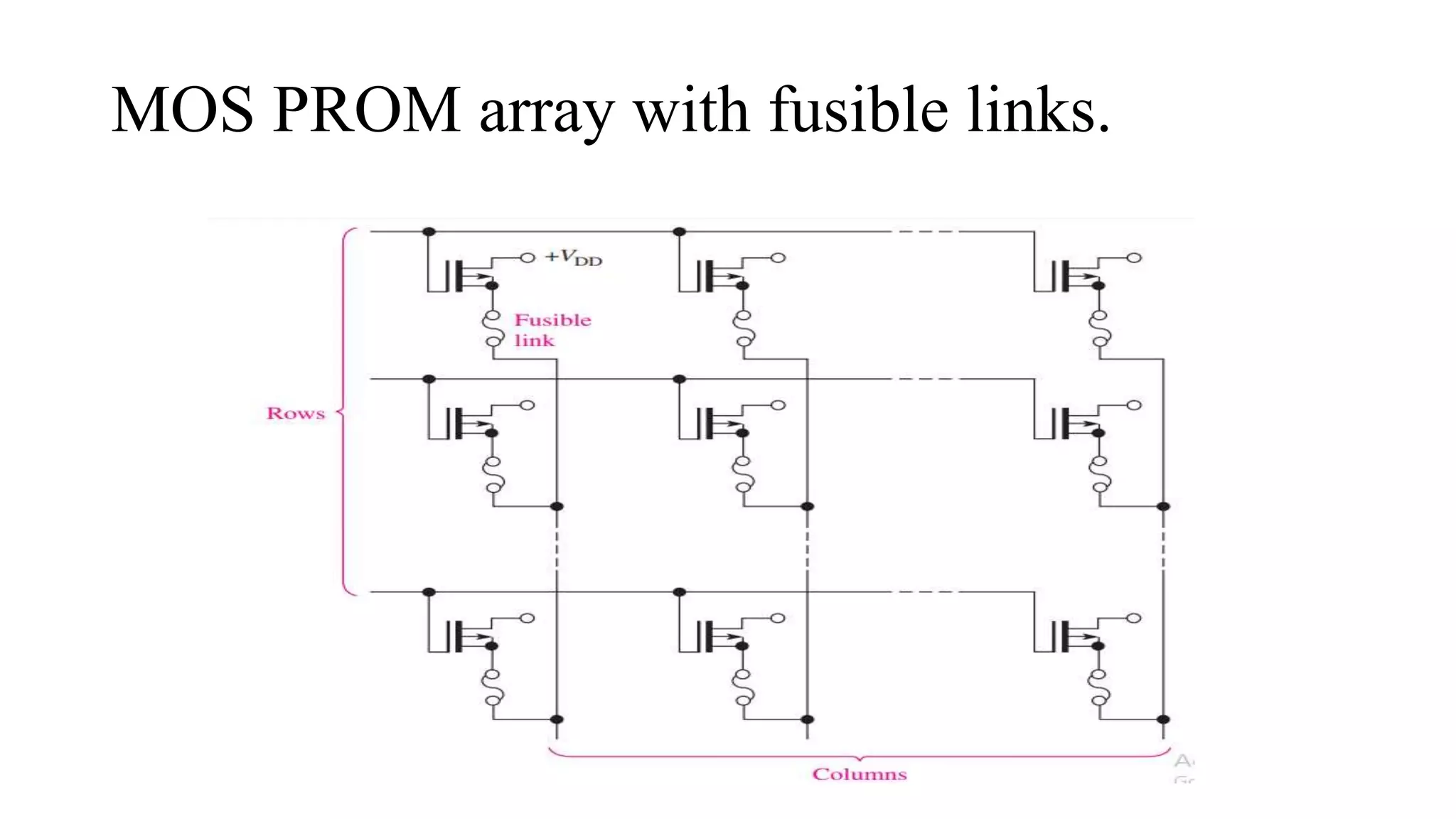

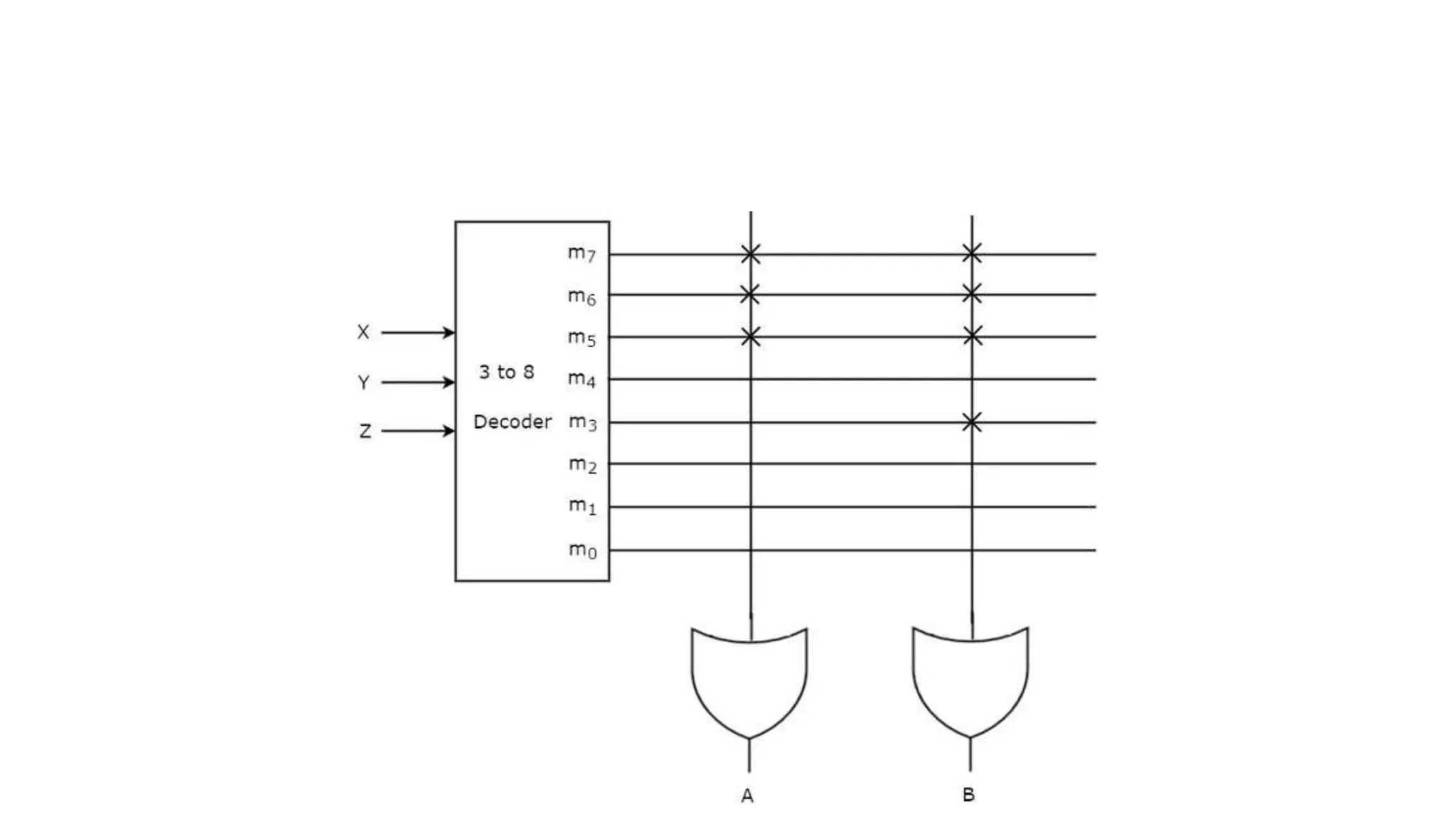

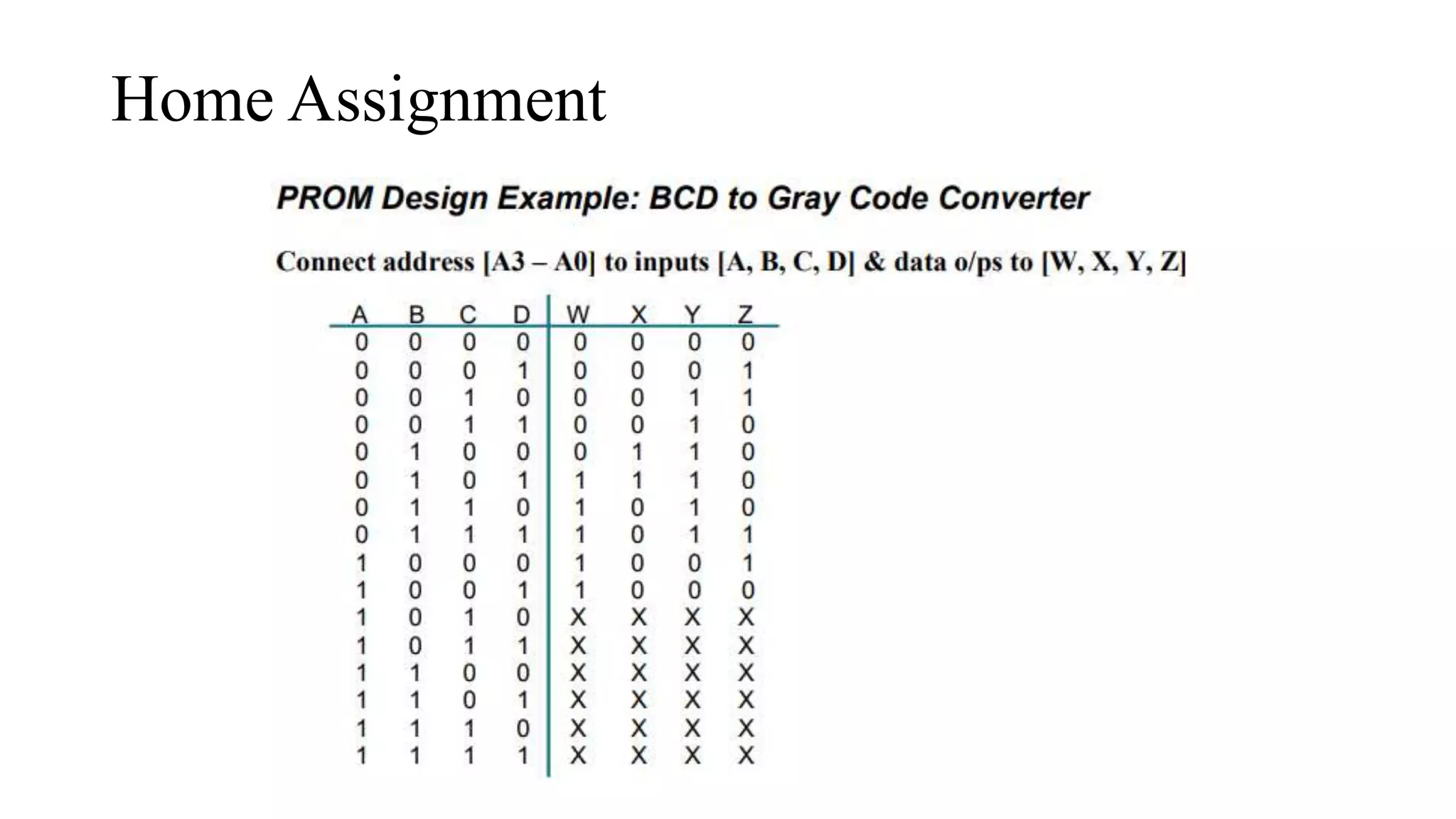

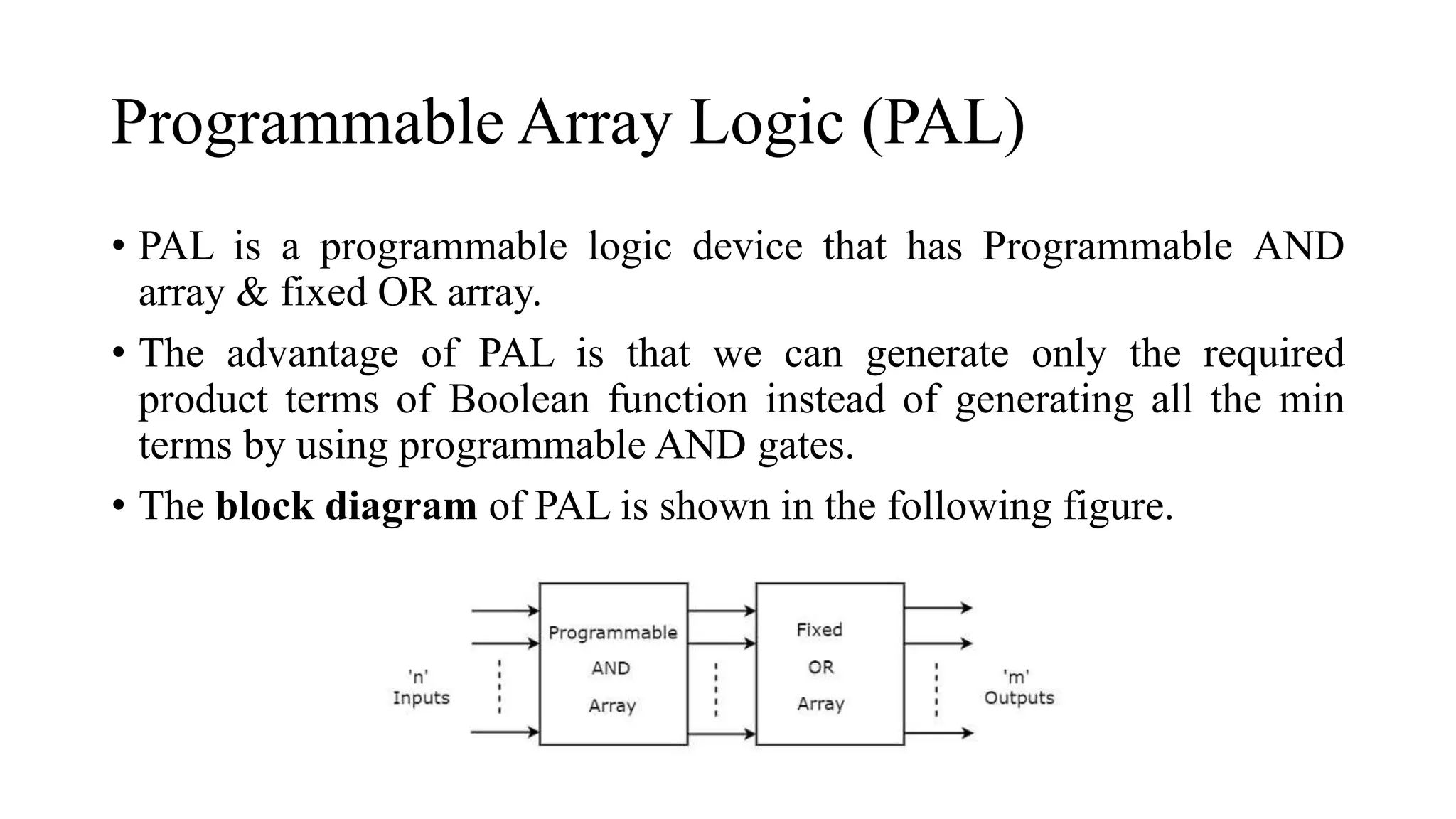

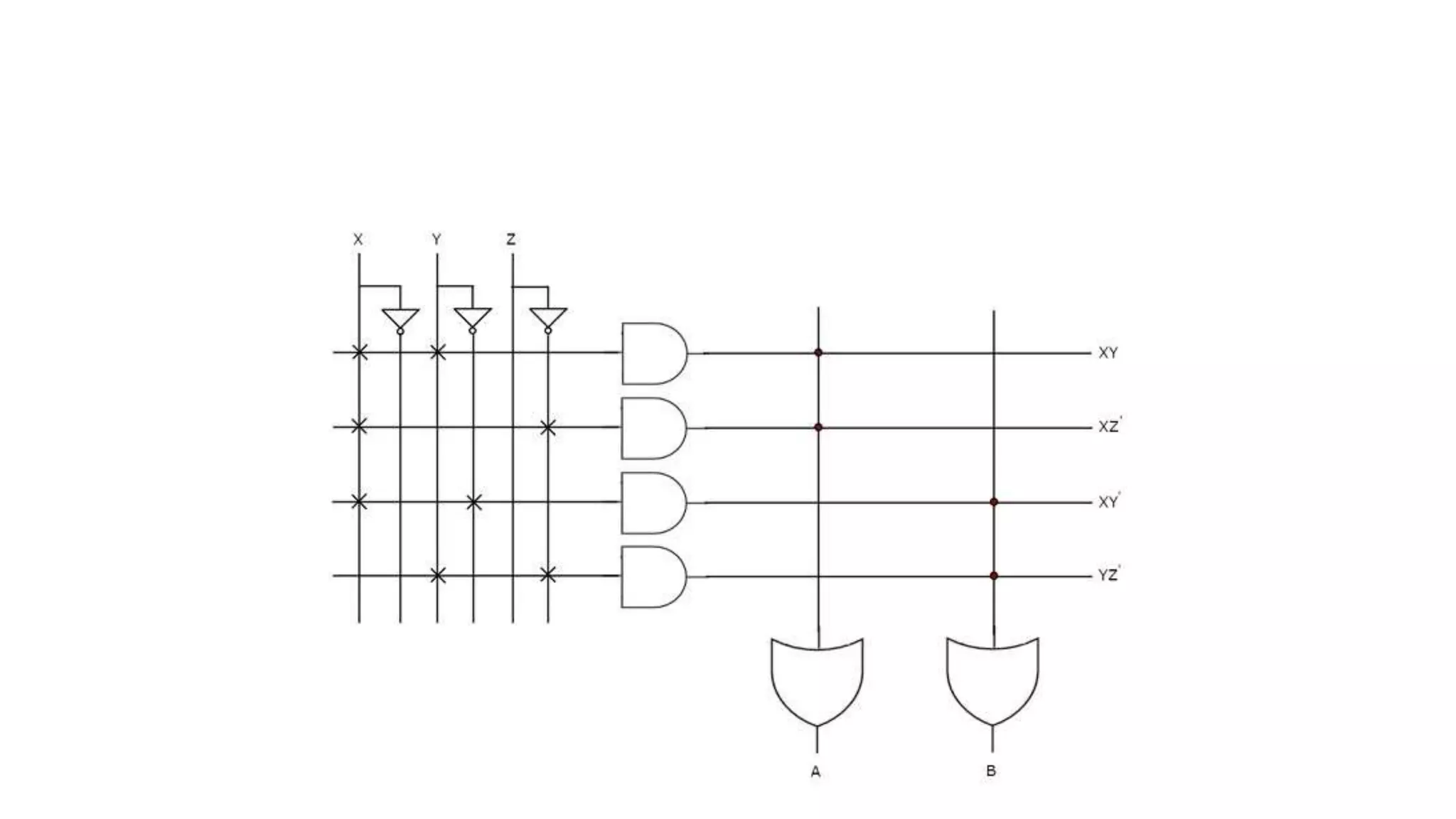

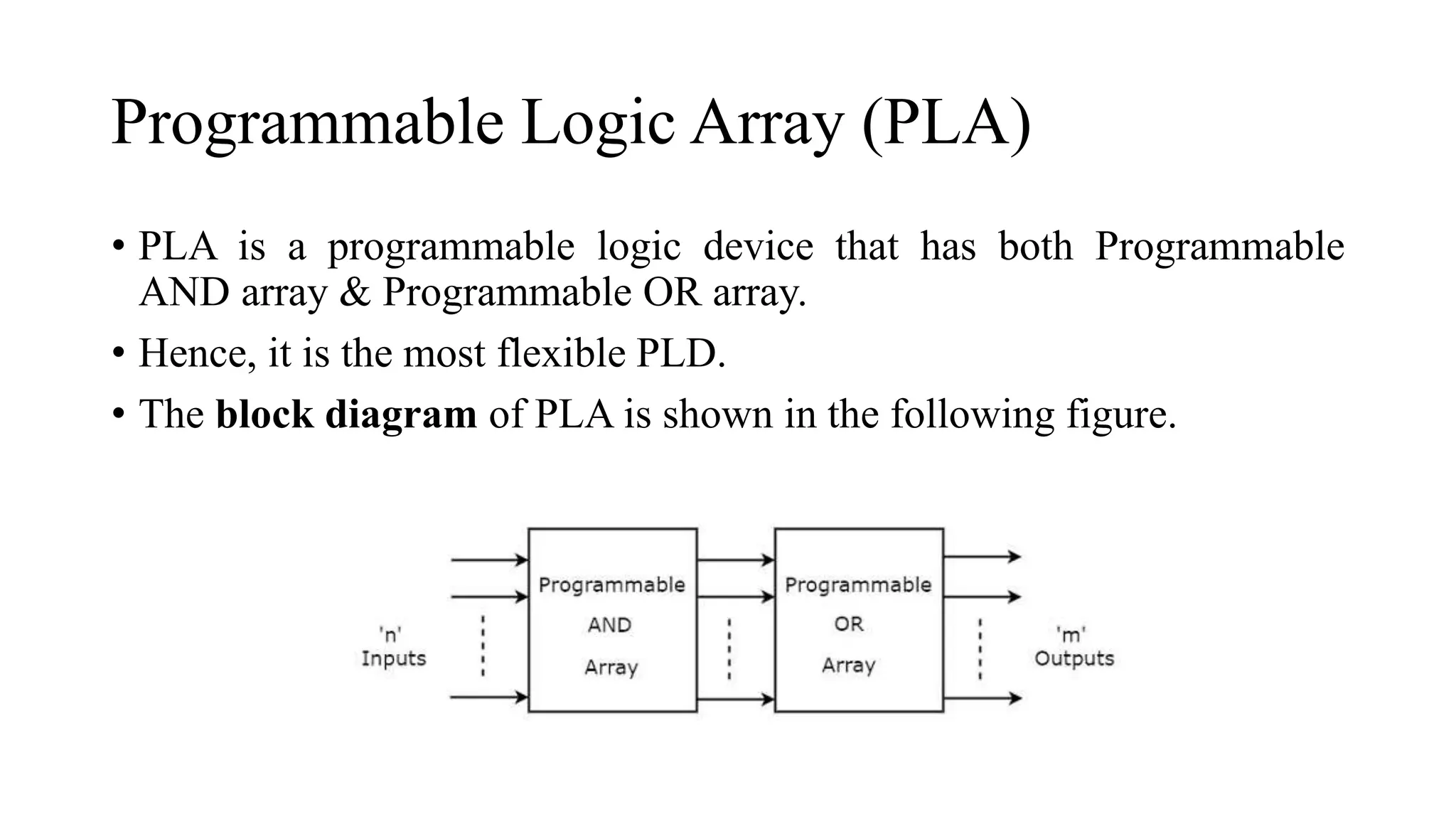

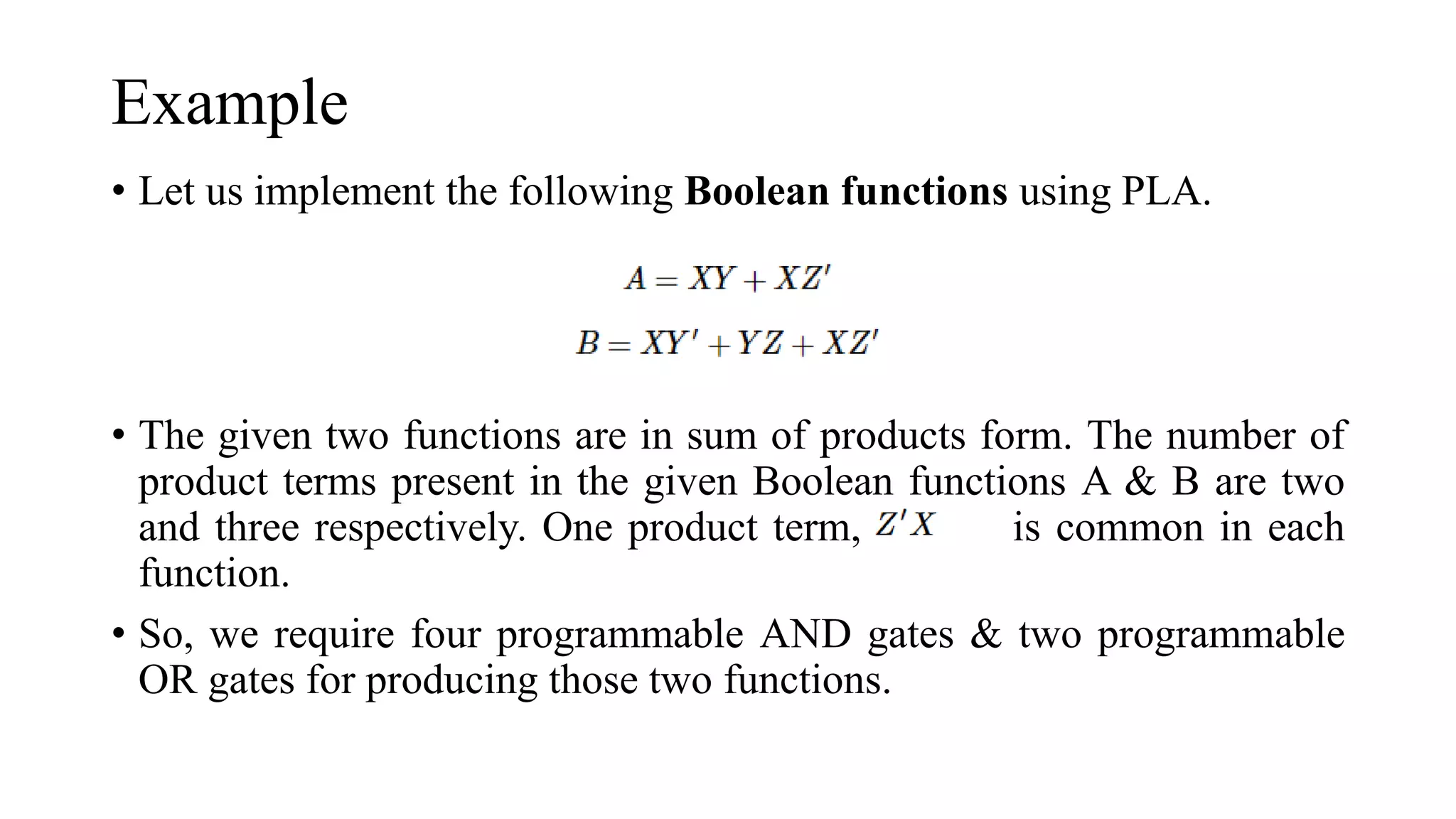

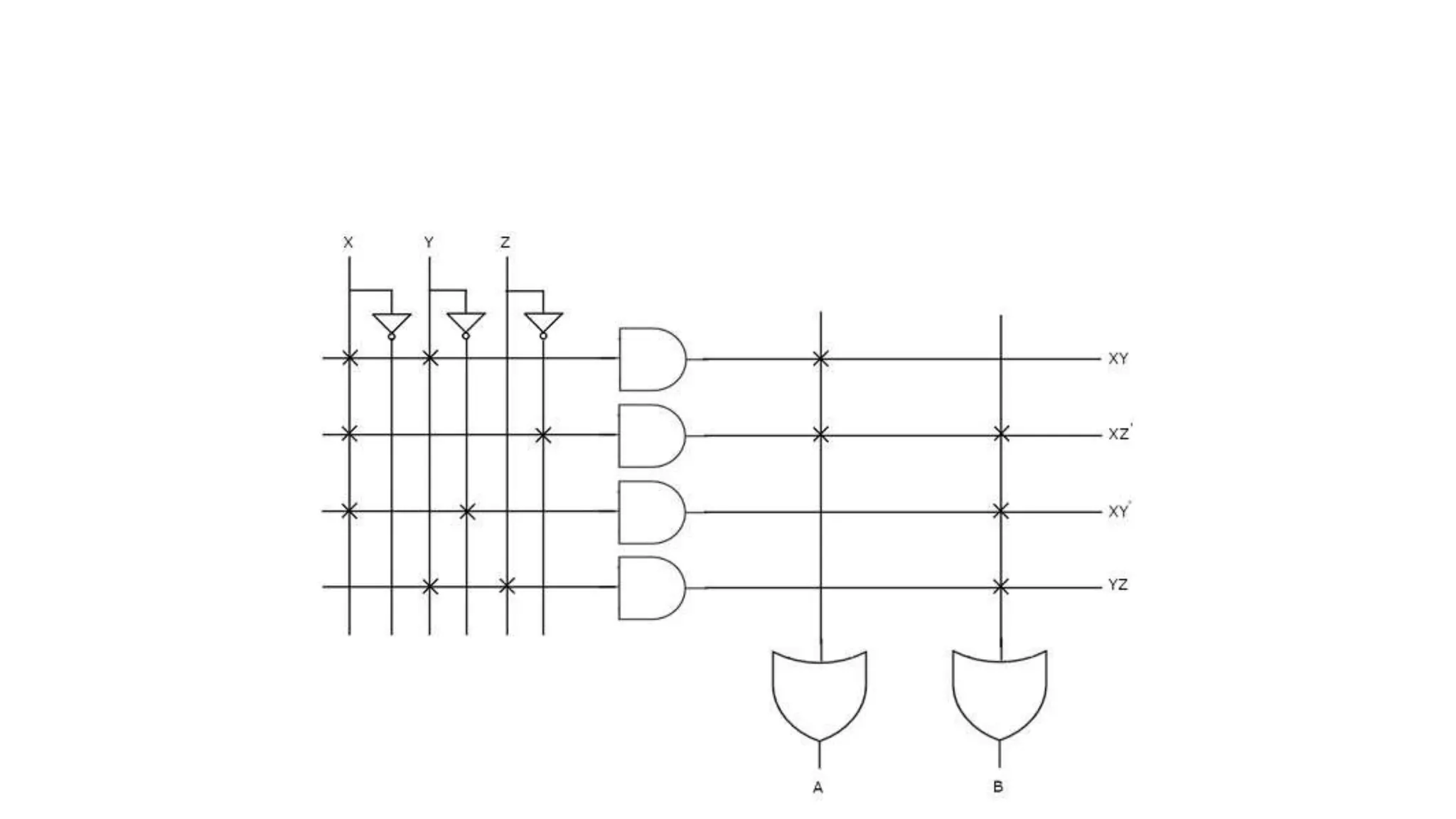

This document discusses programmable logic devices (PLDs), including their basic components and types. PLDs are integrated circuits that can be configured by the user to perform different logic functions. They contain programmable AND and OR gates that allow the user to define the logic function by programming the connections between the gates. Common types of PLDs include PROM, PAL, and PLA, which differ in whether their AND gates and/or OR gates are programmable. The document provides examples and diagrams to illustrate how basic logic functions can be implemented using each type of PLD.