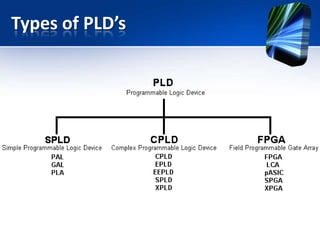

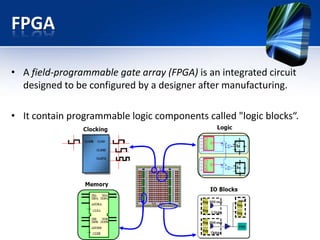

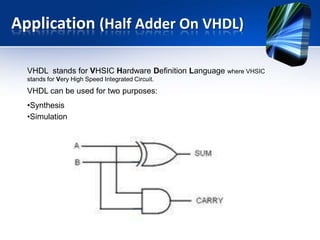

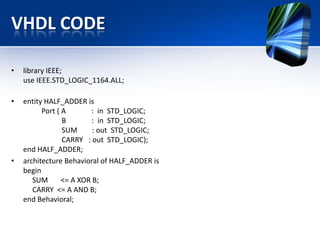

This document discusses programmable logic devices (PLDs) like field programmable gate arrays (FPGAs). It provides details on FPGA types and vendors like Xilinx. FPGAs offer efficient resource utilization and flexibility. Xilinx is a major FPGA vendor and the document describes Xilinx FPGA families and features. It also includes an example VHDL code for a half adder circuit implemented on an FPGA.