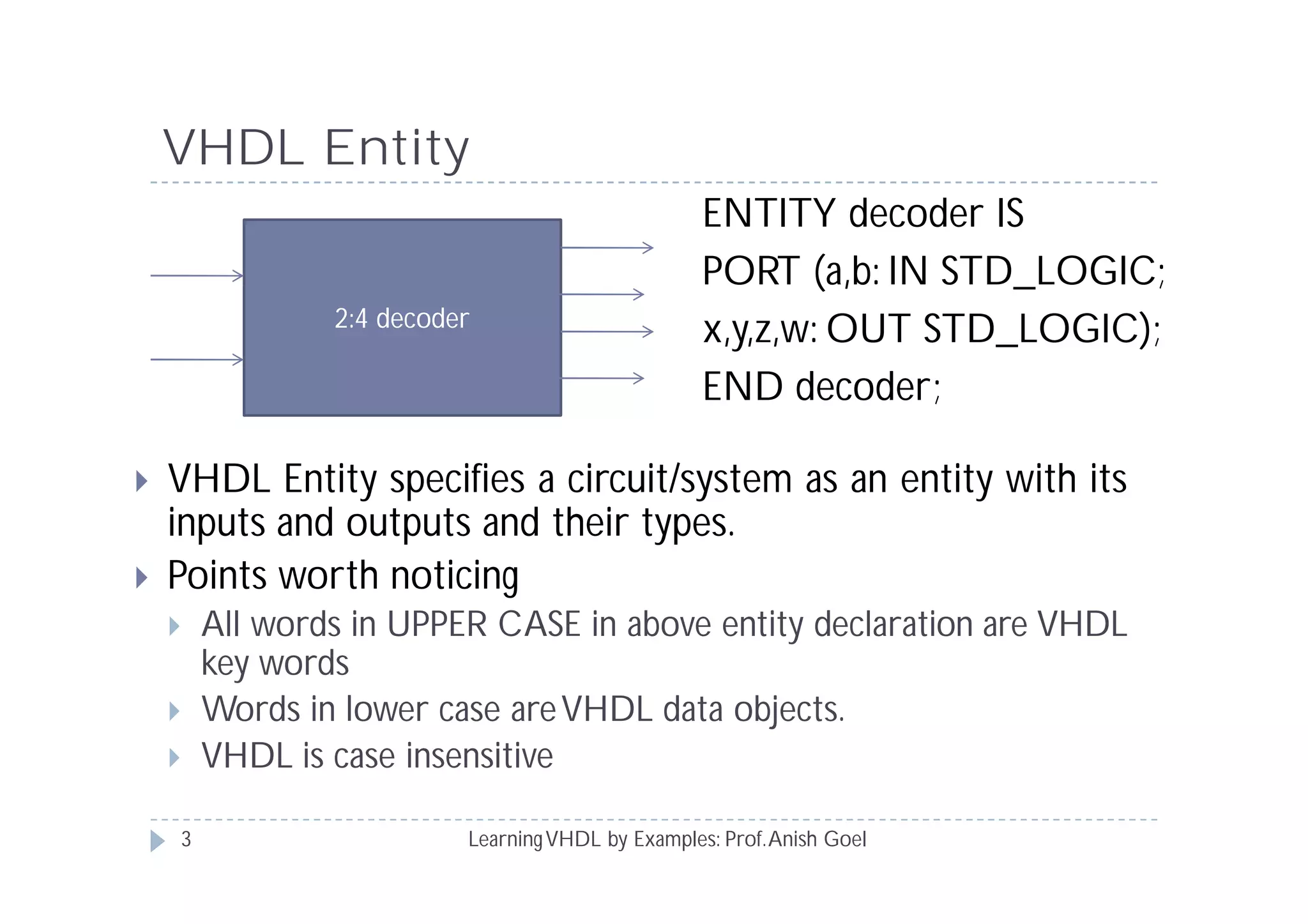

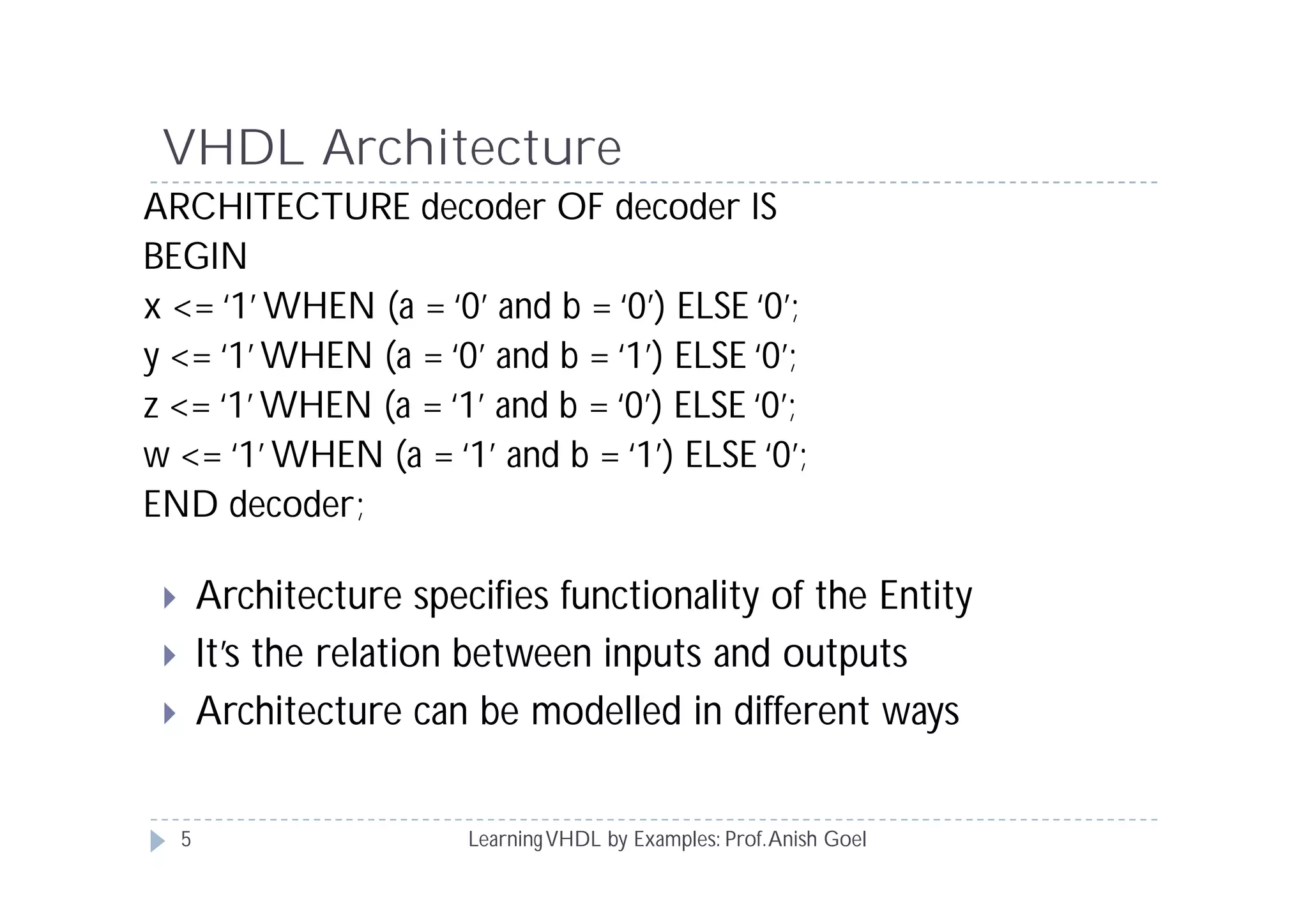

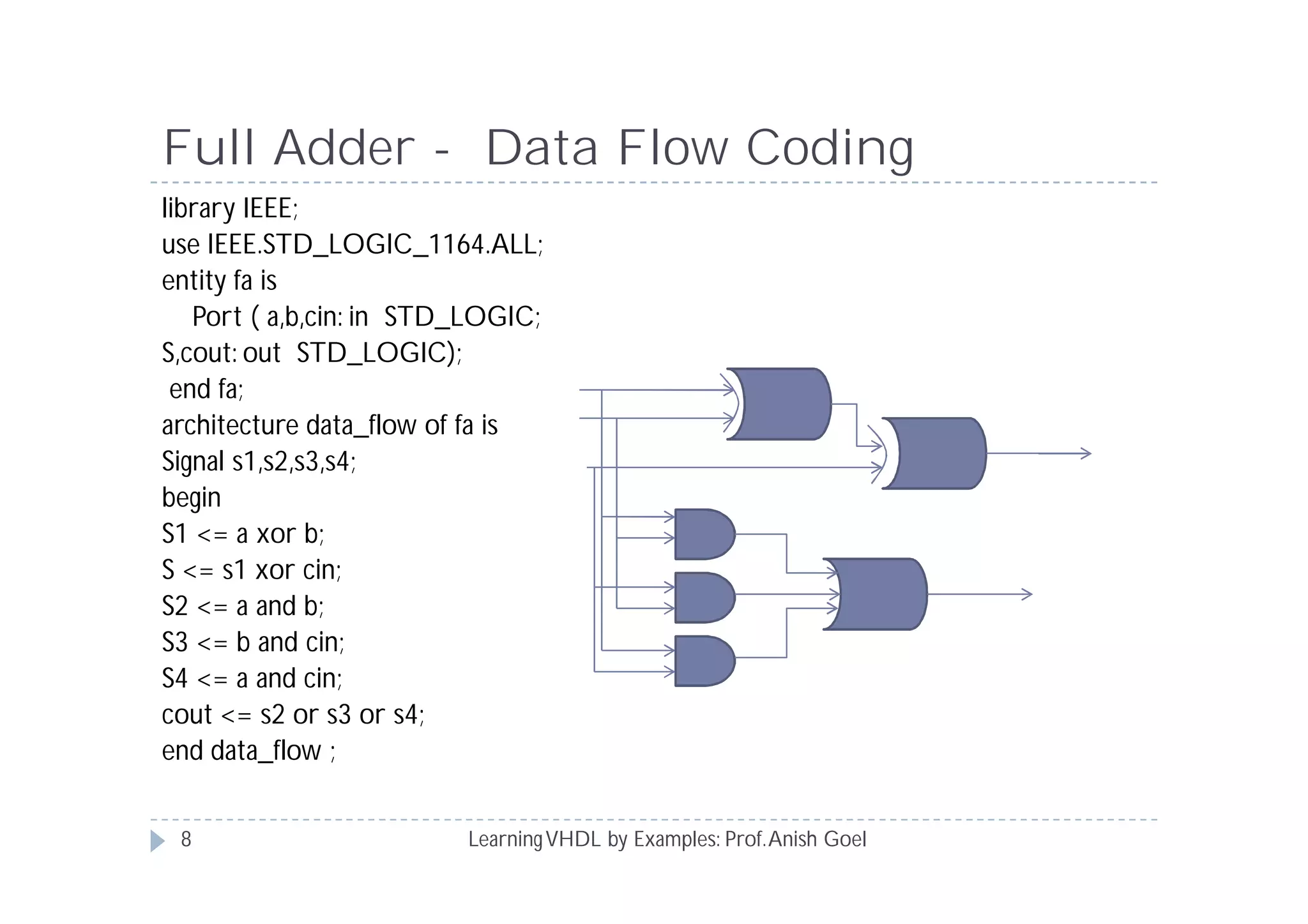

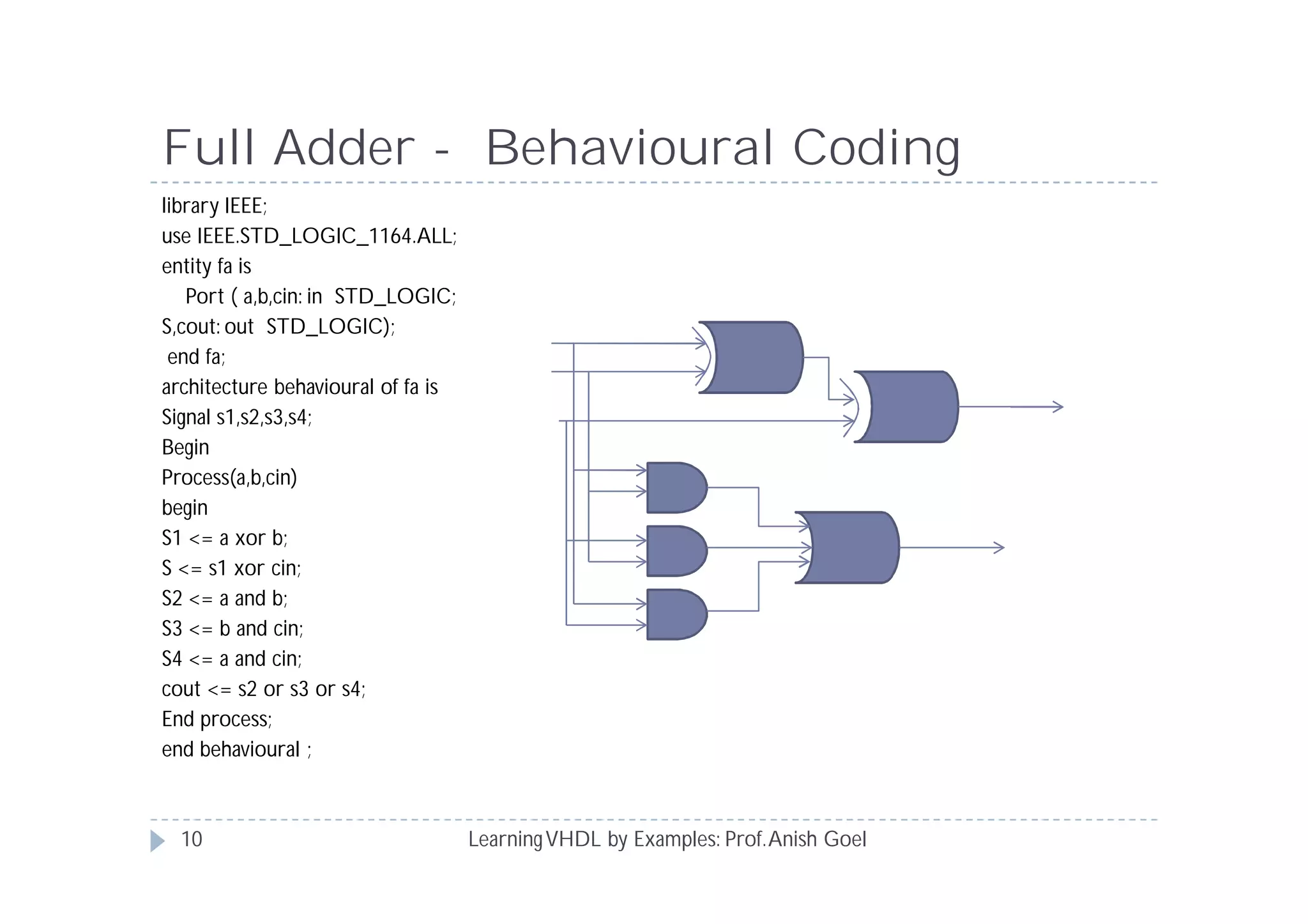

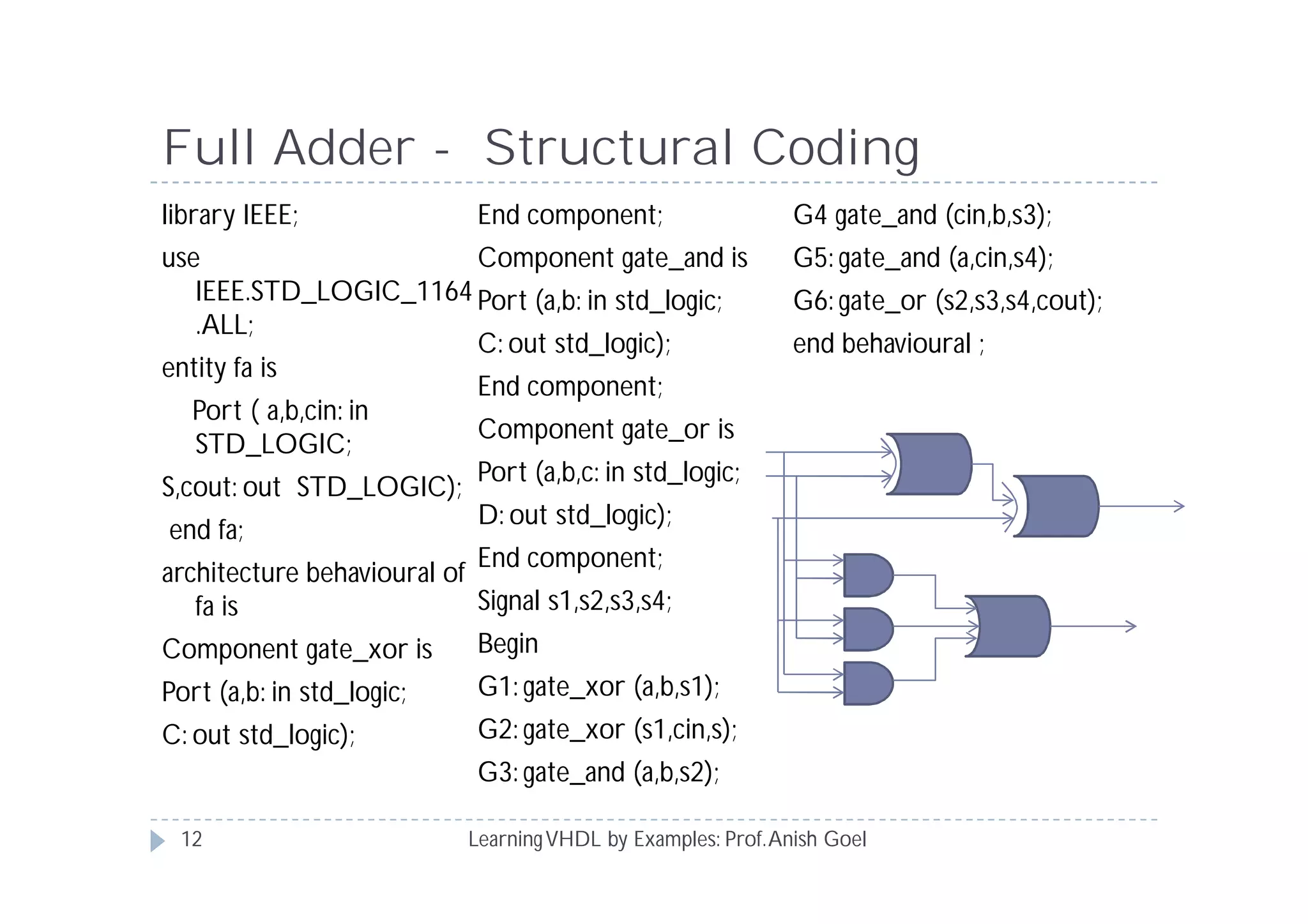

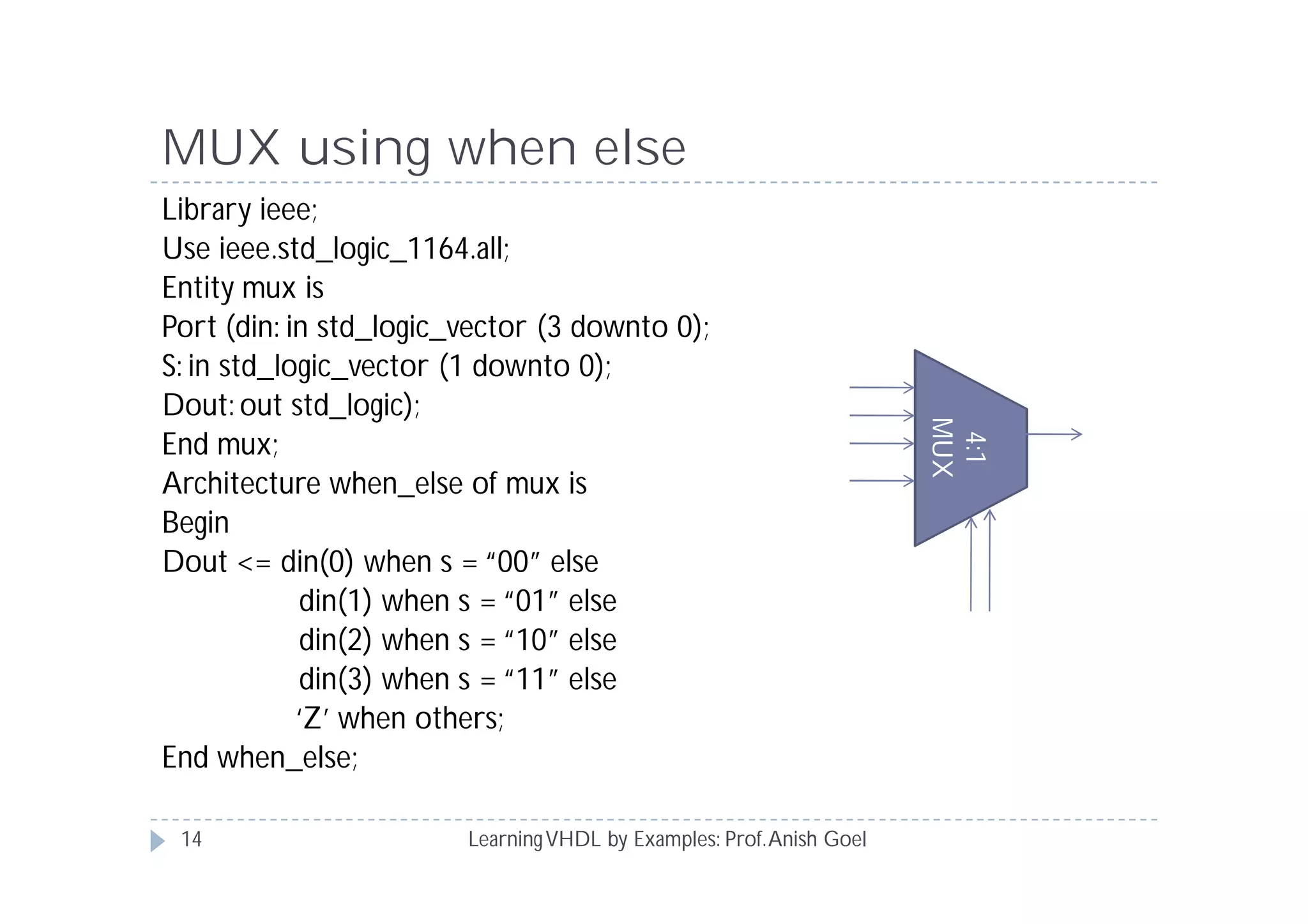

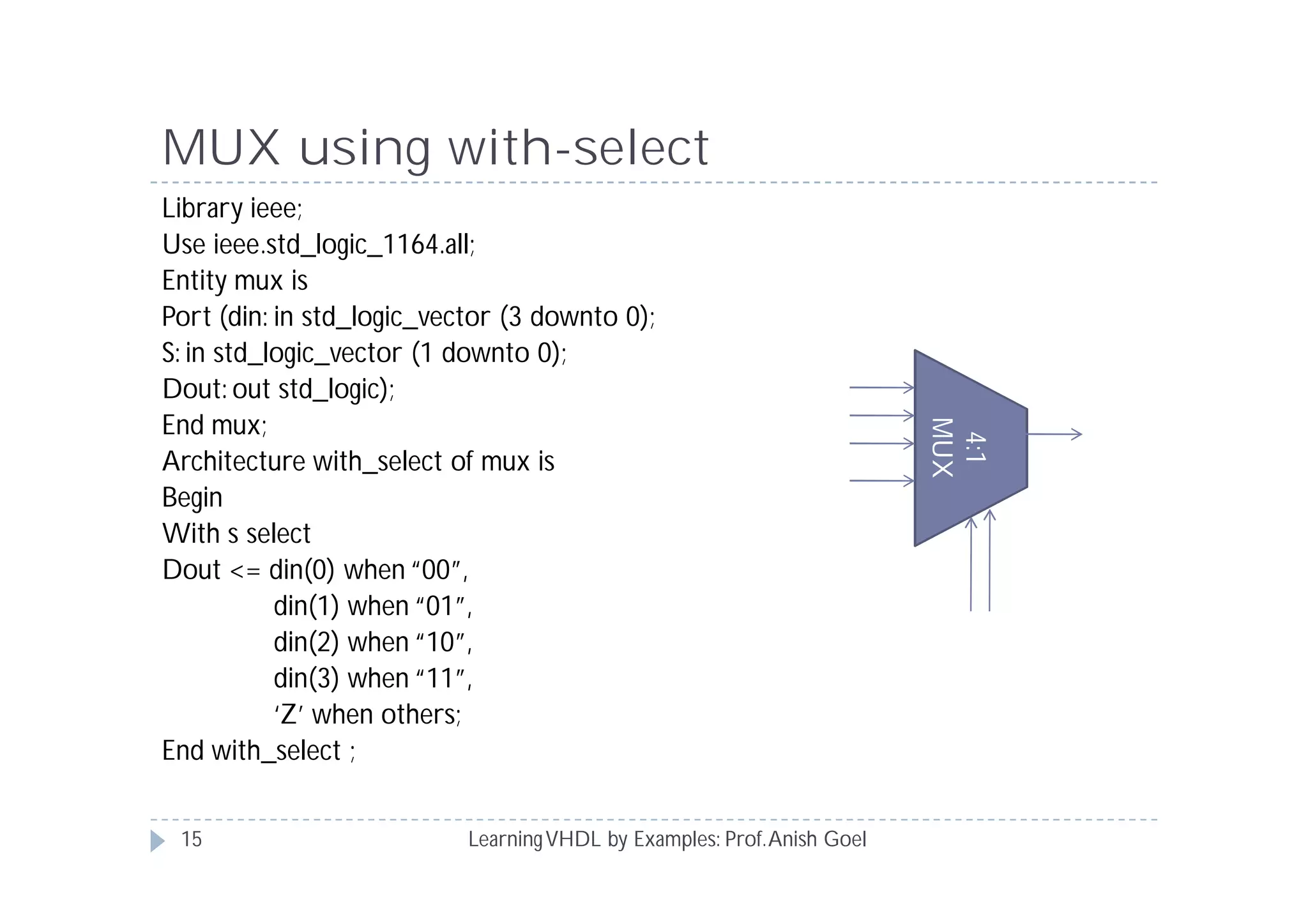

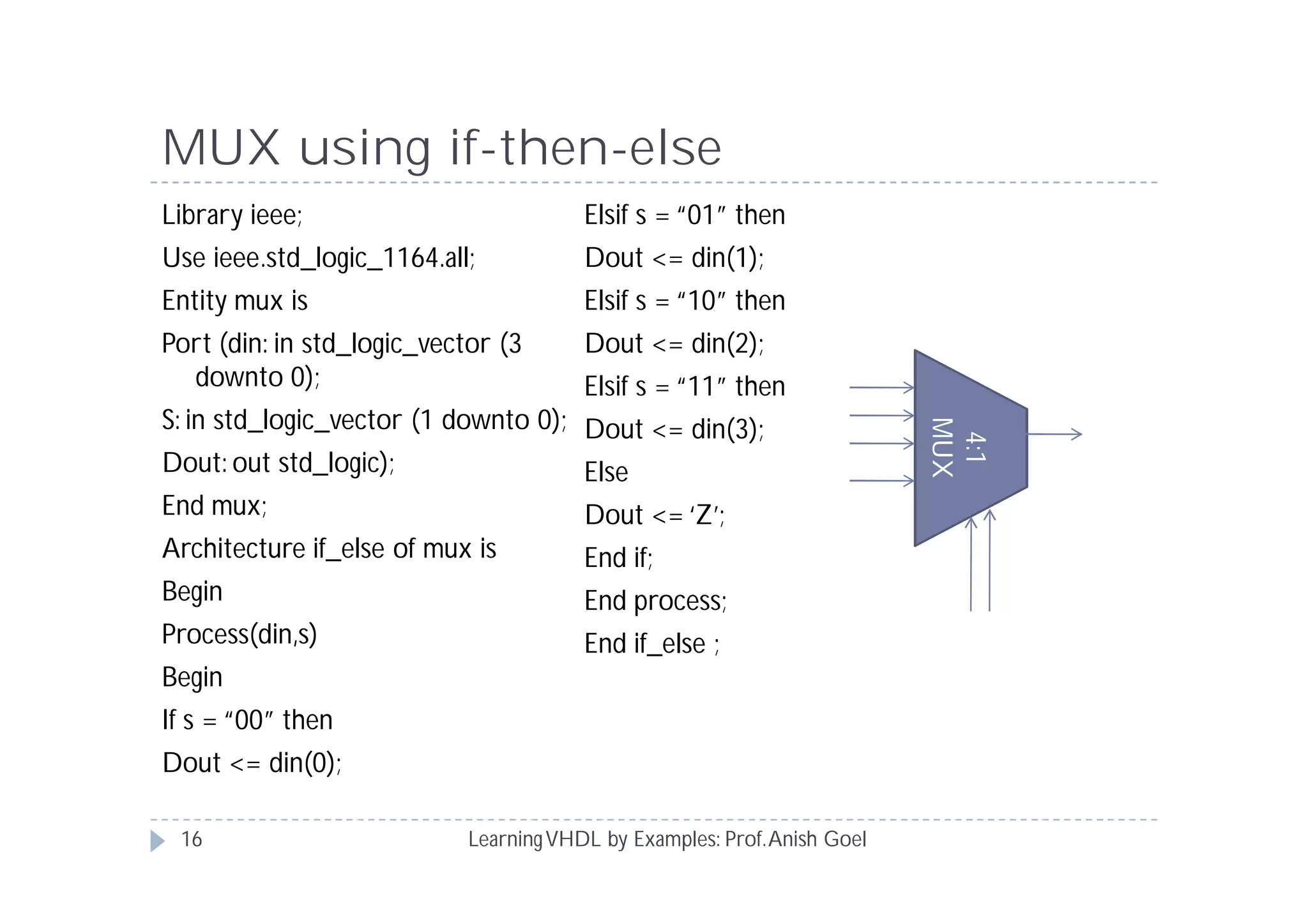

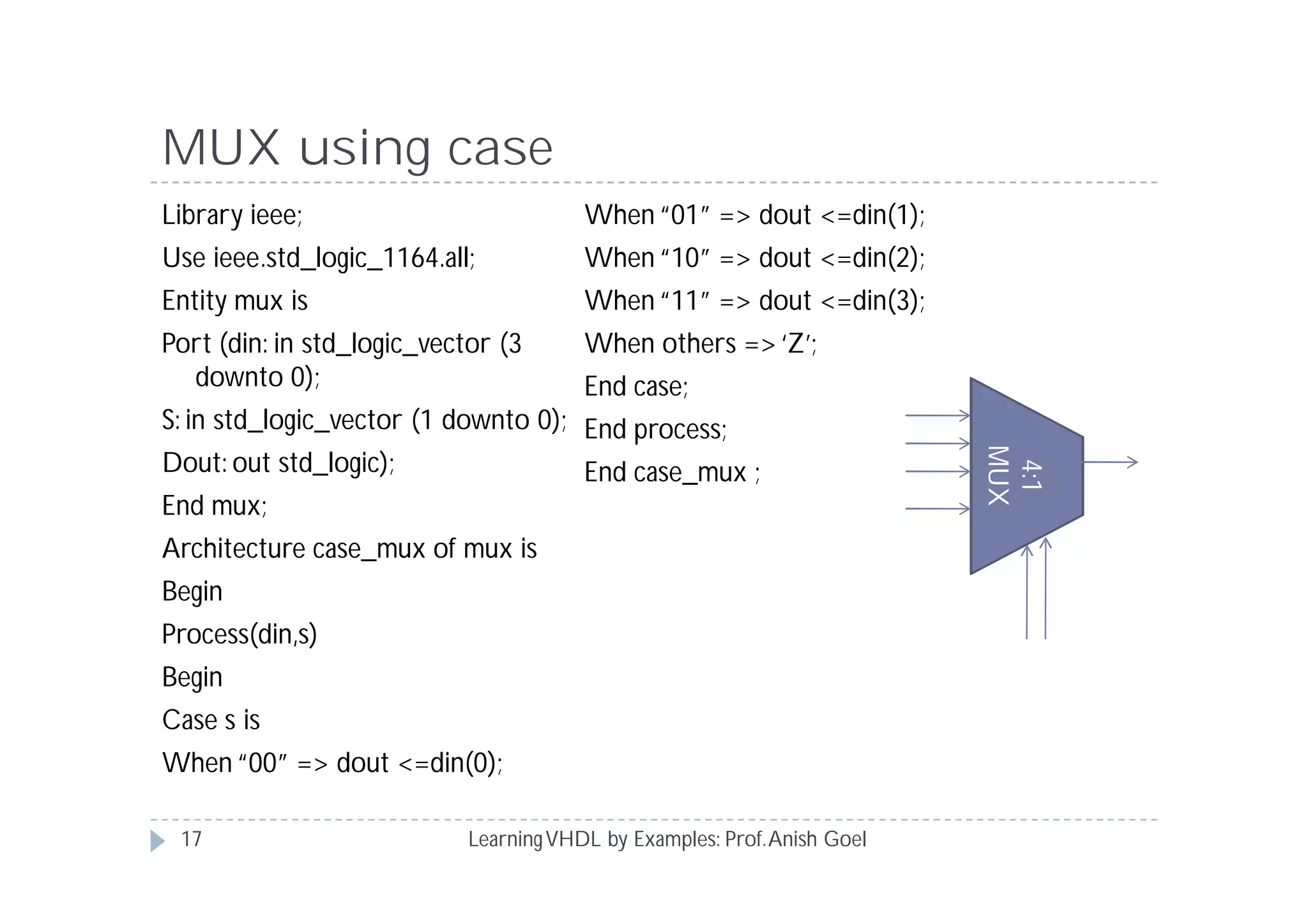

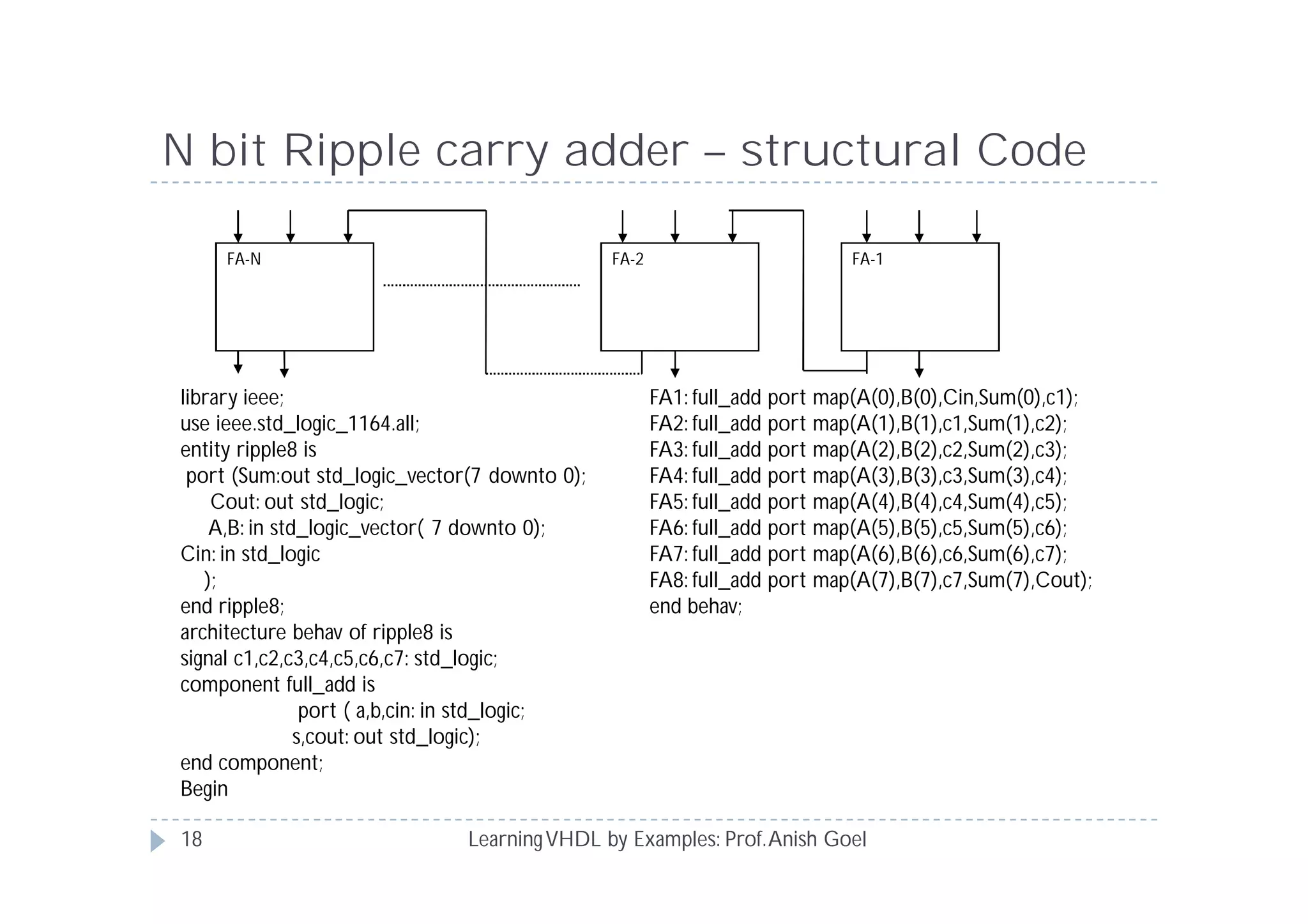

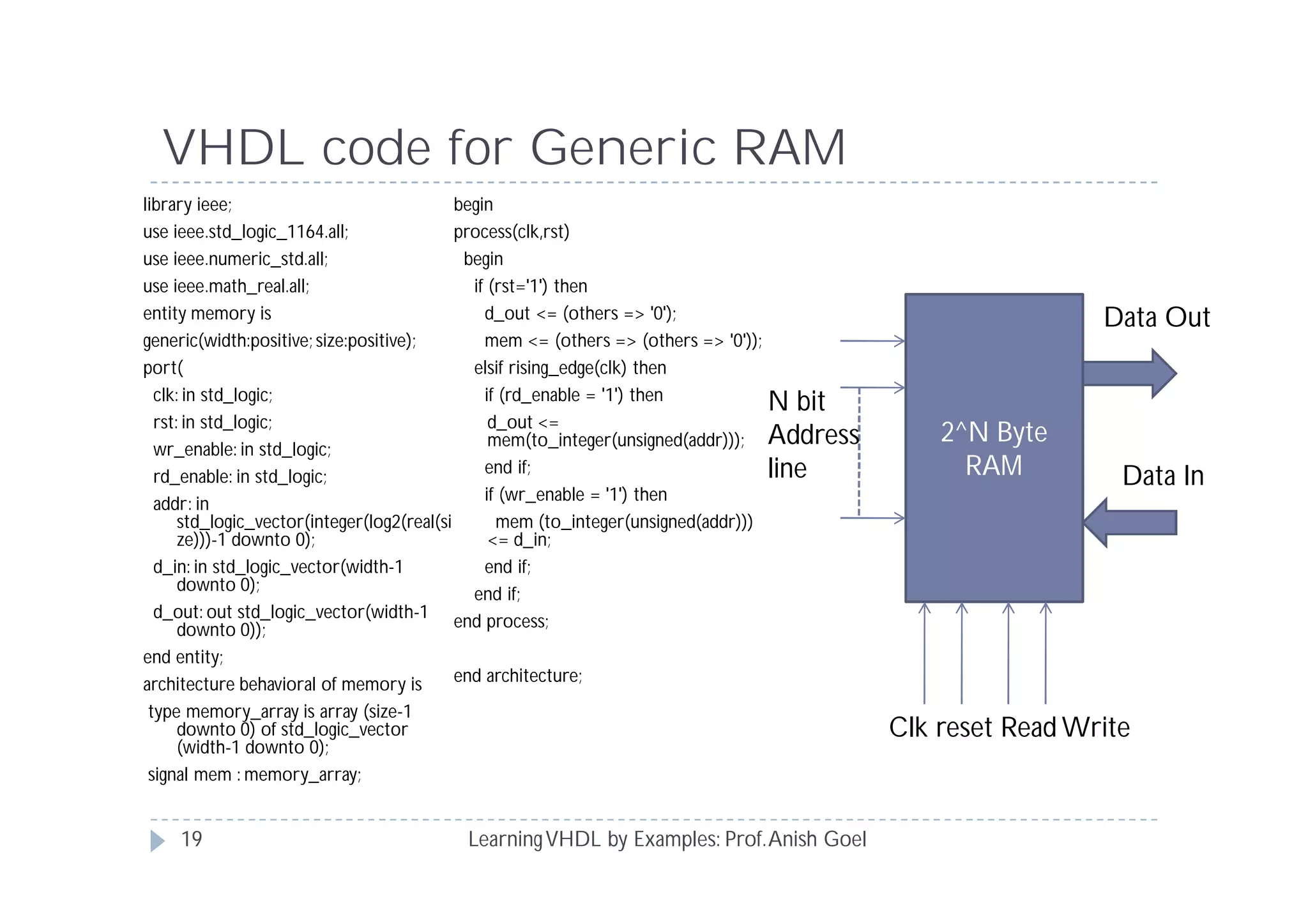

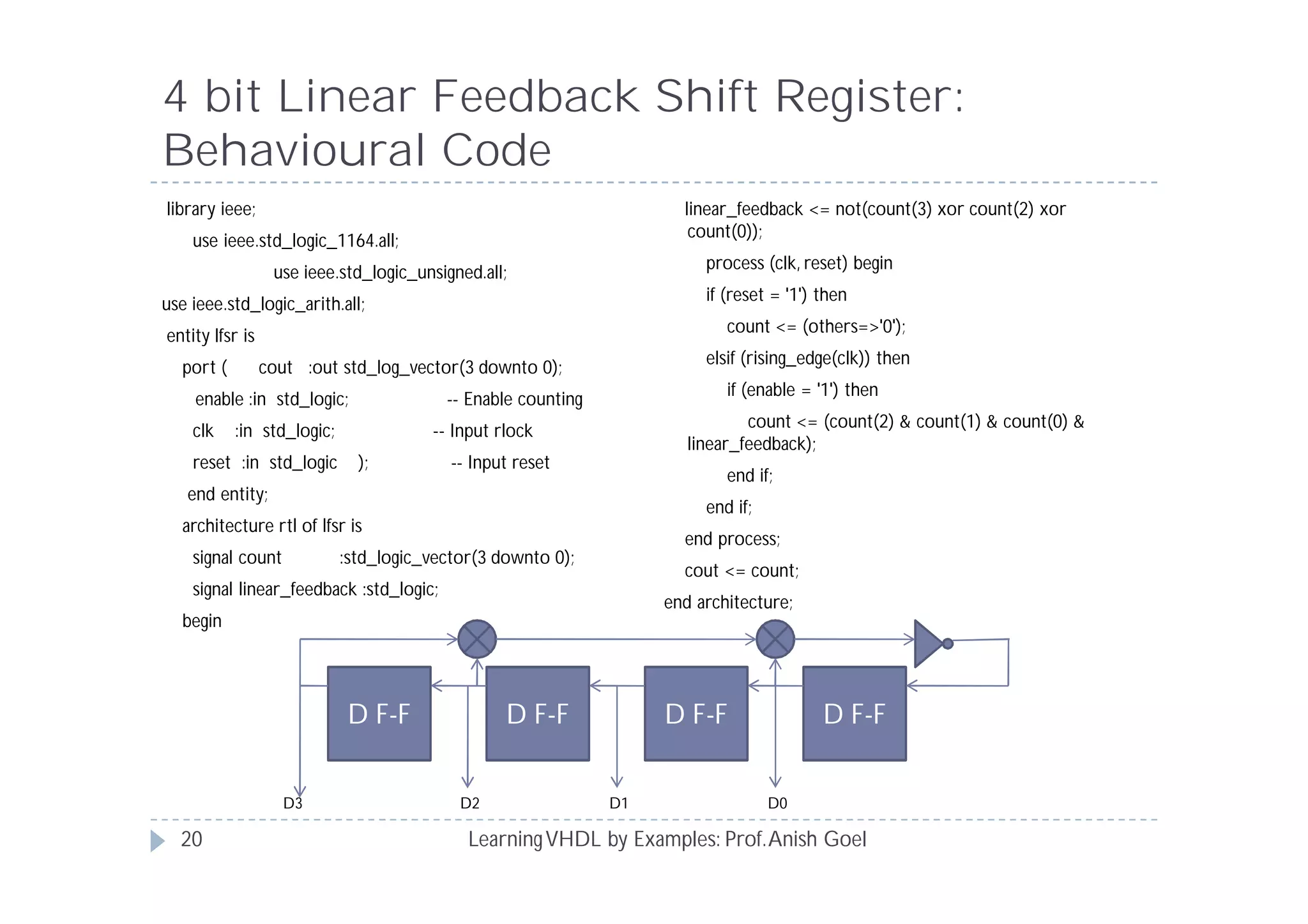

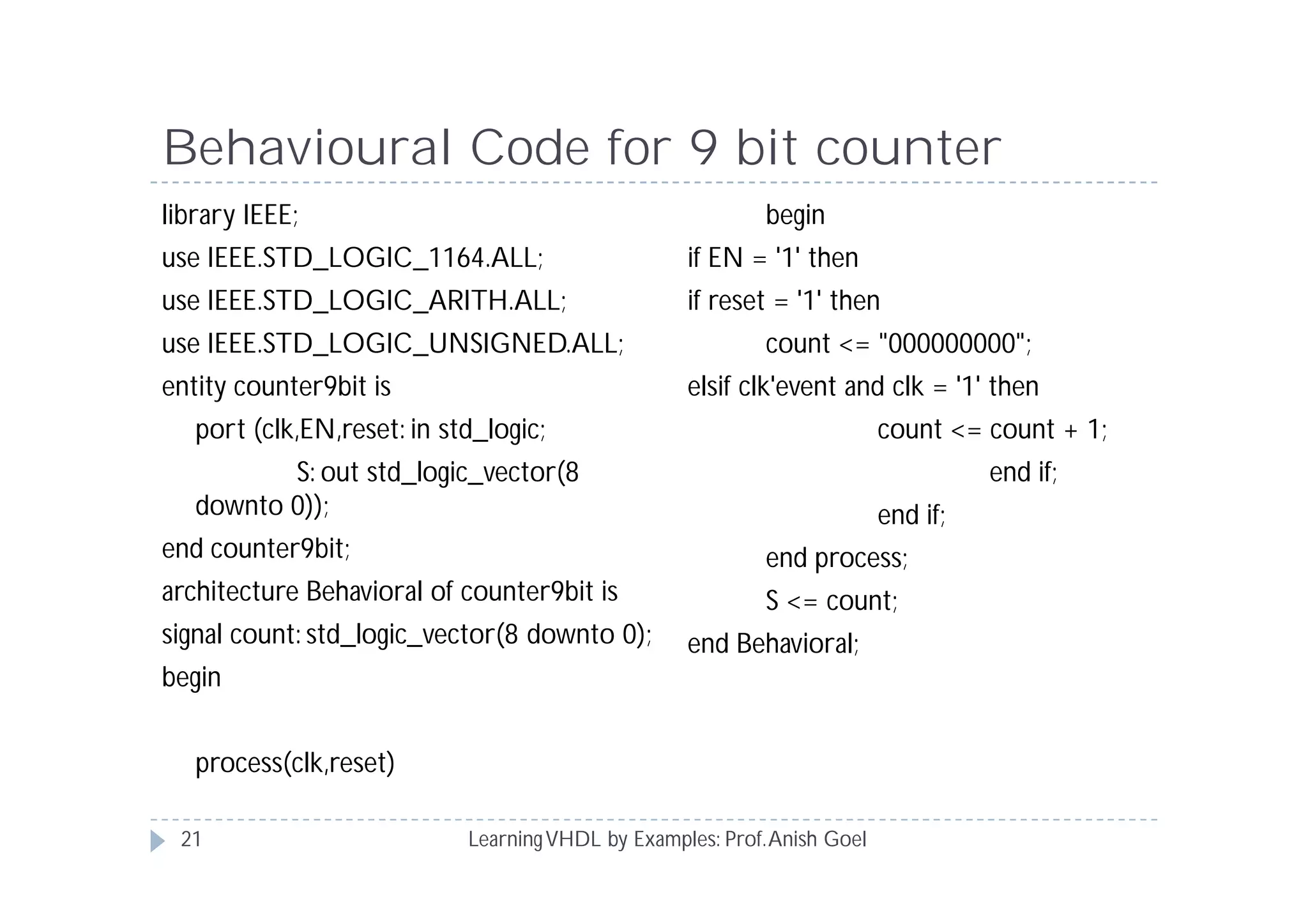

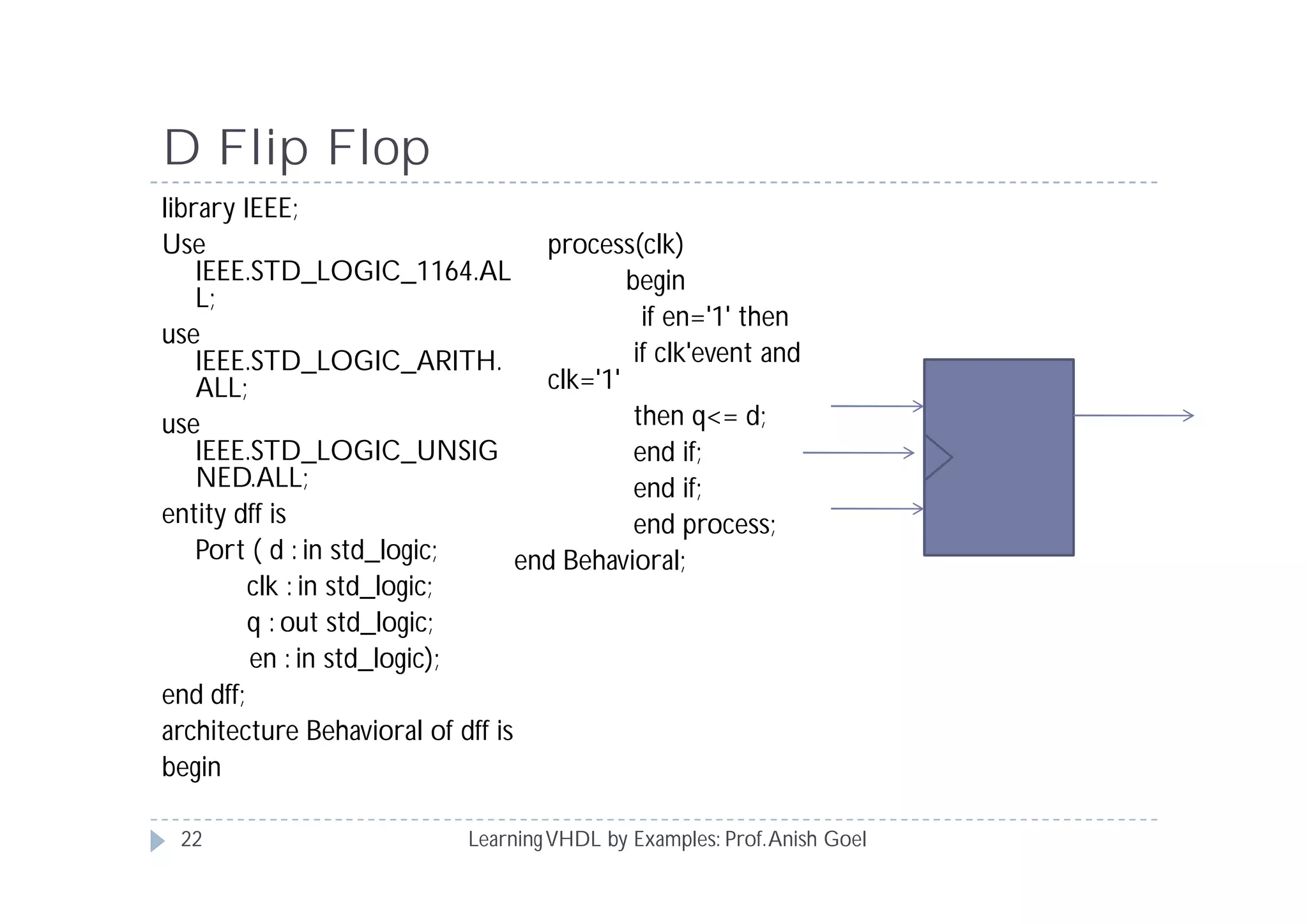

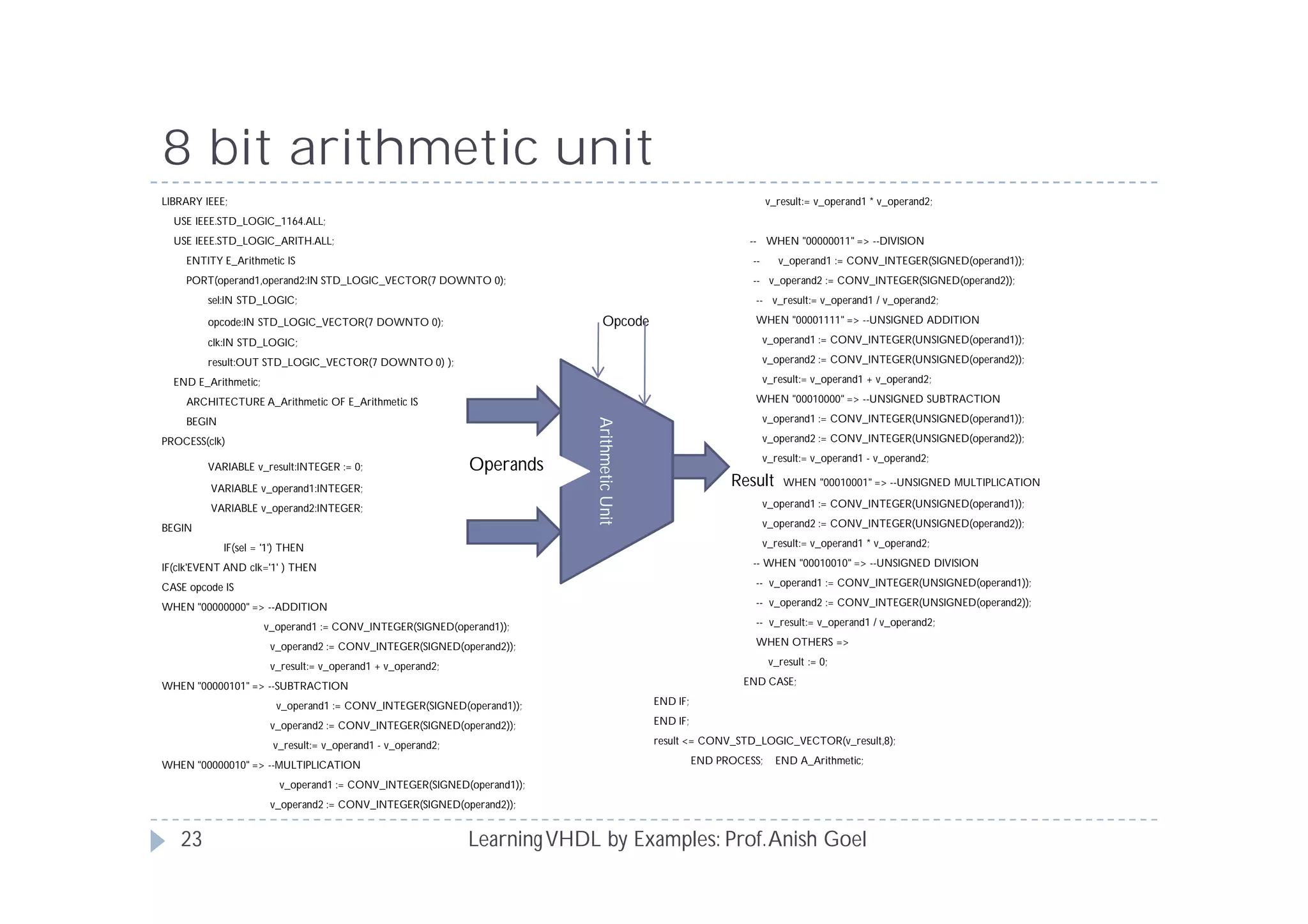

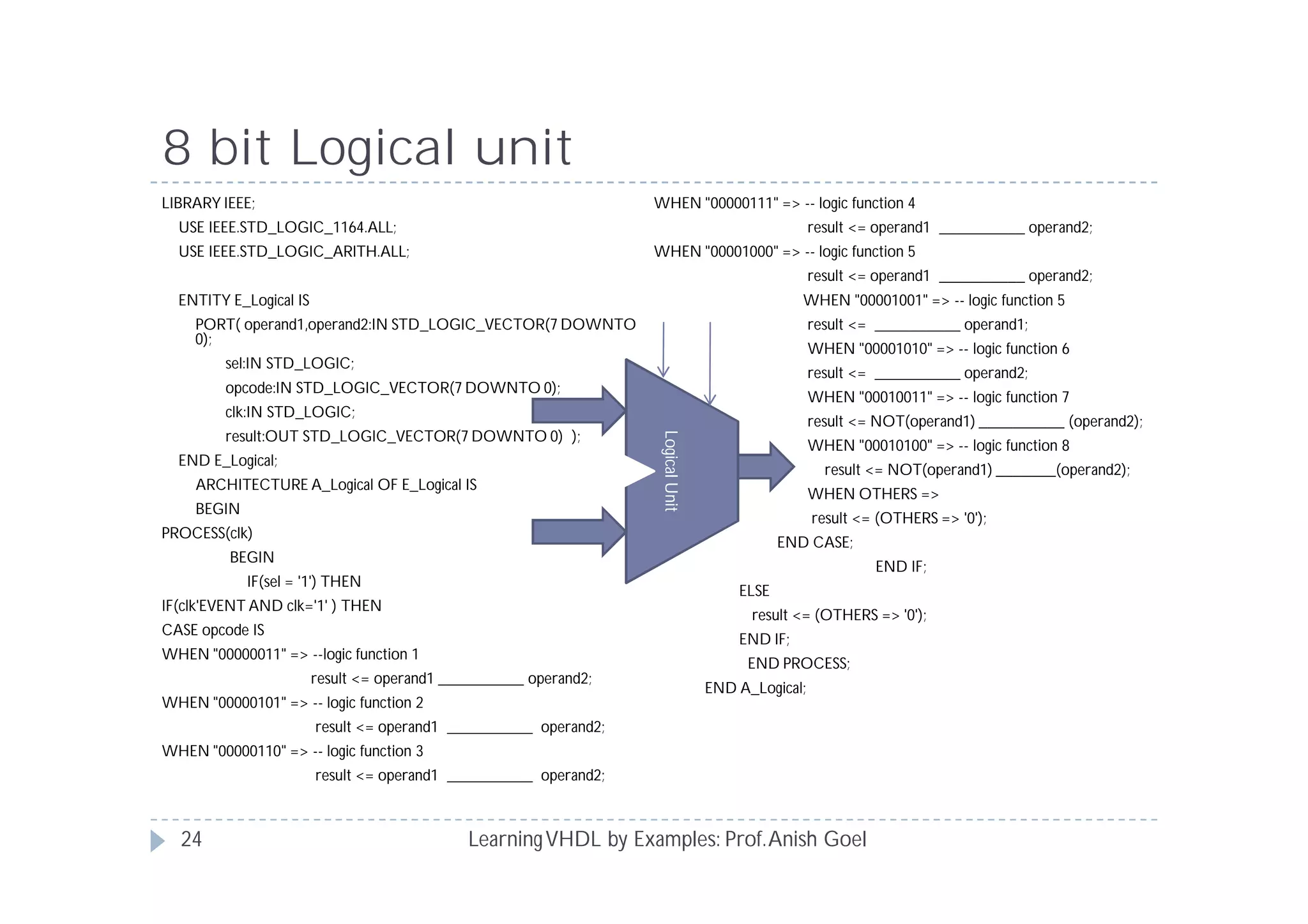

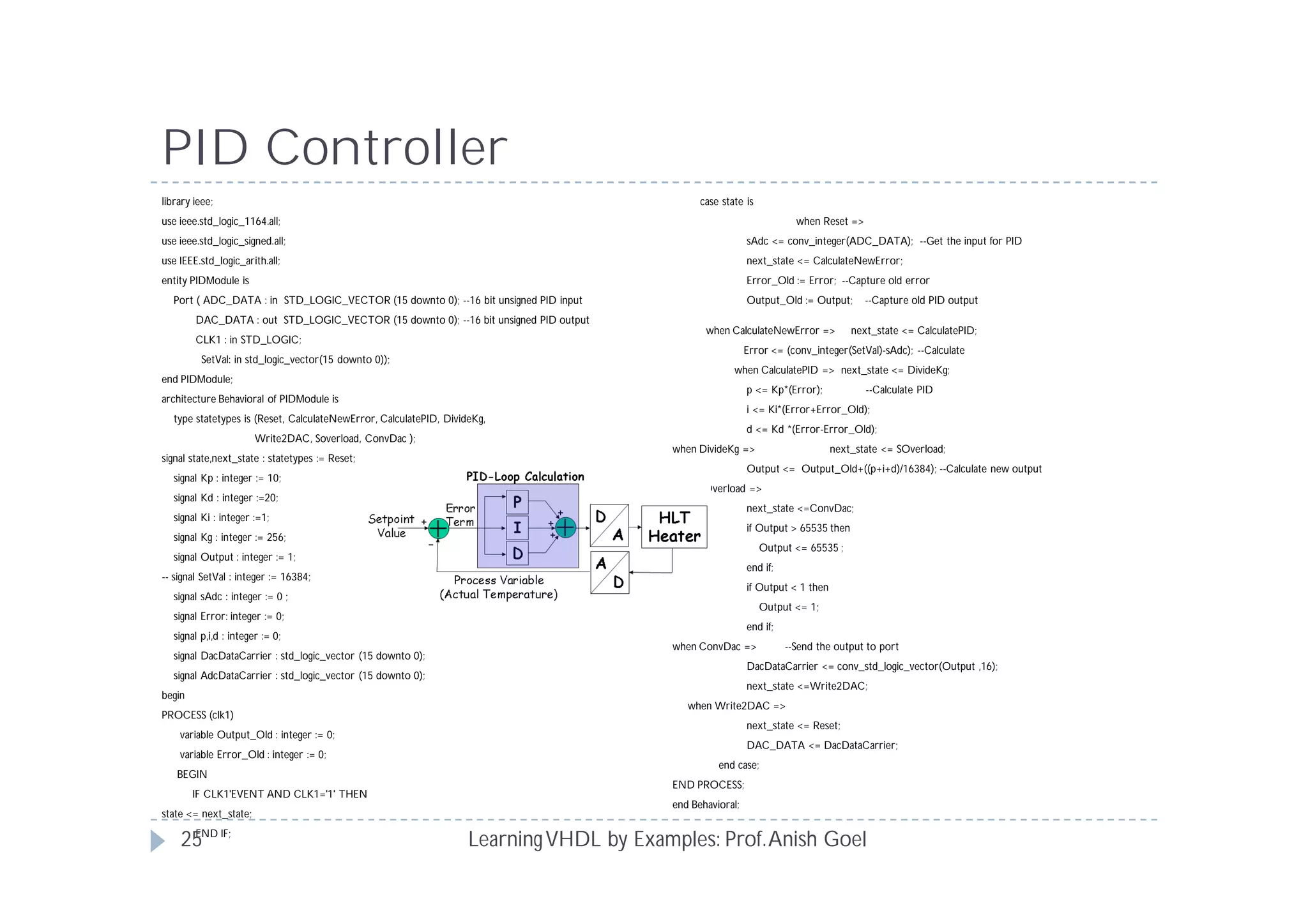

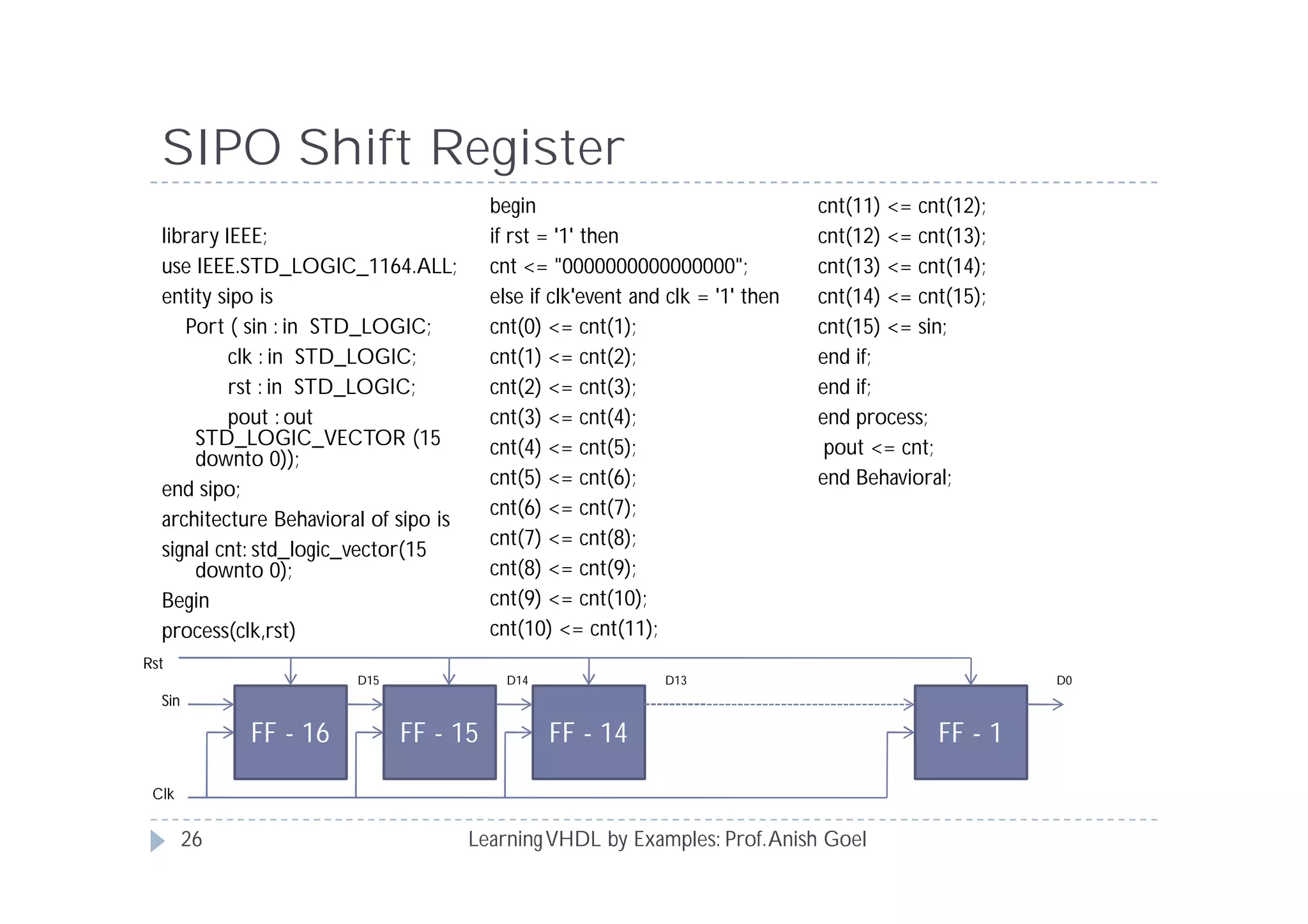

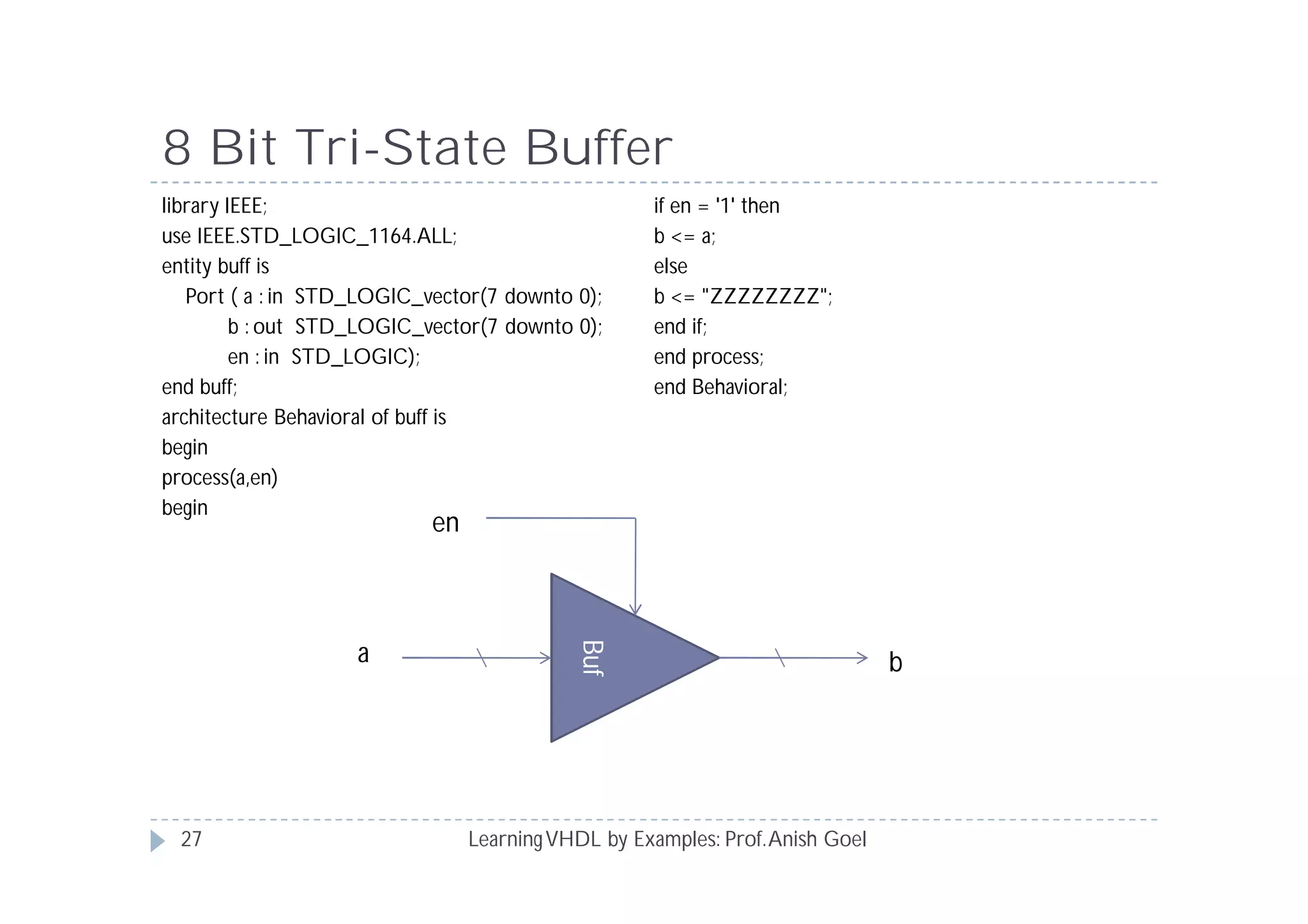

This document provides an overview of VHDL concepts including entity, architecture, data types, modeling styles, assignment statements, and examples. It discusses how to define an entity with inputs and outputs, use architectures to specify functionality, and model systems using data flow, behavioral, and structural styles. It also gives examples of using conditional and concurrent statements like if/case and when/else. Application examples include decoders, multiplexers, counters, arithmetic units, and shift registers.