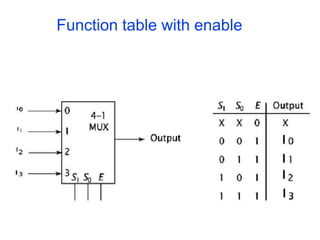

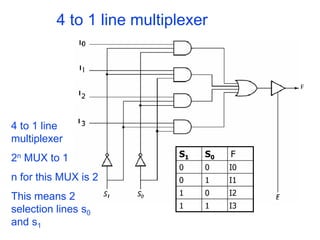

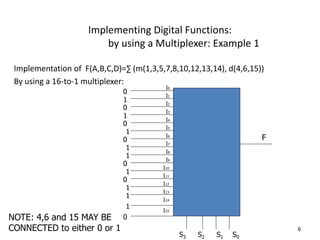

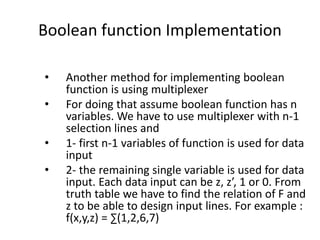

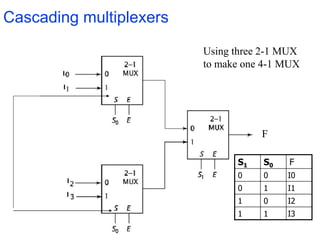

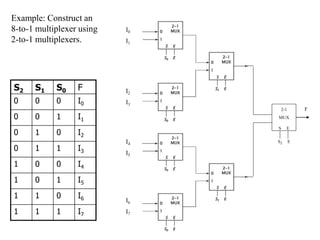

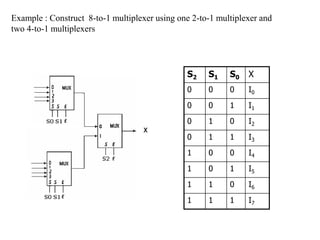

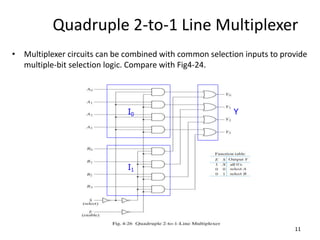

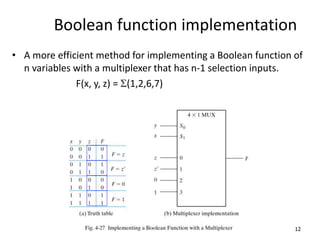

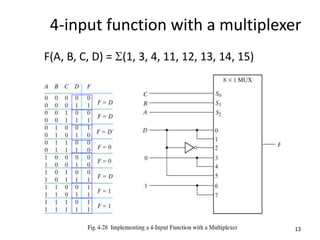

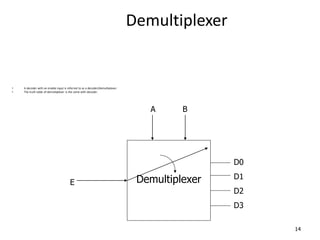

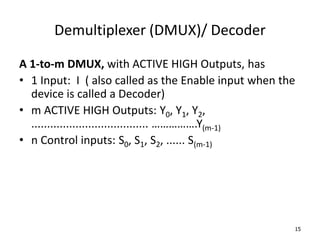

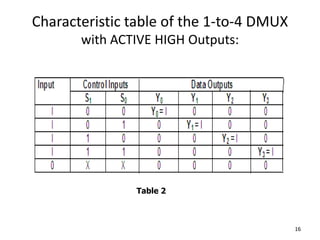

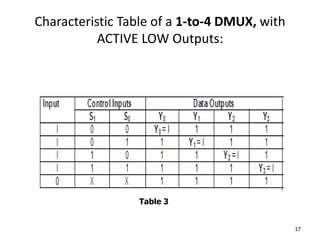

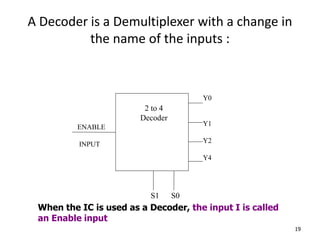

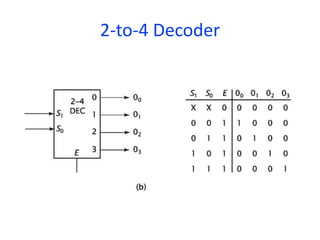

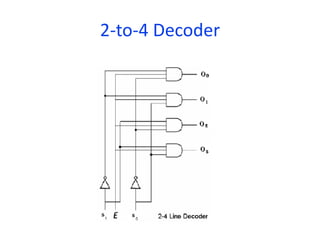

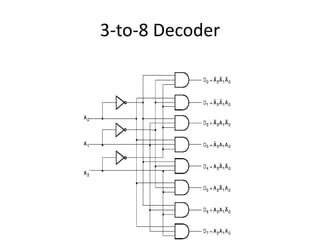

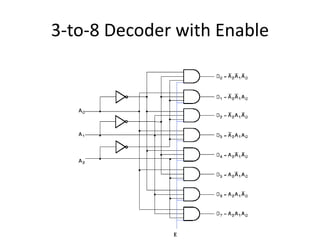

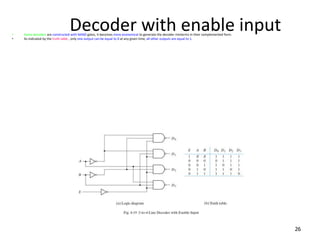

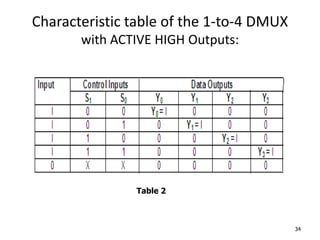

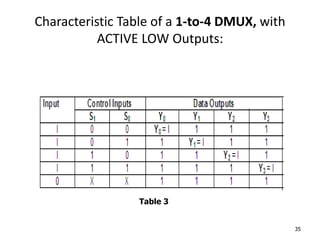

A multiplexer is a combinational logic circuit that selects one of several input lines and outputs the data on that line. It has 2n input lines and n selection lines, where the values on the selection lines determine which input line is output. For example, a 2-to-1 multiplexer has two inputs and one selection line, outputting either the first or second input depending on the selection line value. Multiplexers can be cascaded to build larger multiplexers. Boolean functions can also be implemented using multiplexers. A demultiplexer is similar but has one input and multiple outputs, using the selection lines to determine which output is activated. Decoders are similar to demultiplexers but are used to