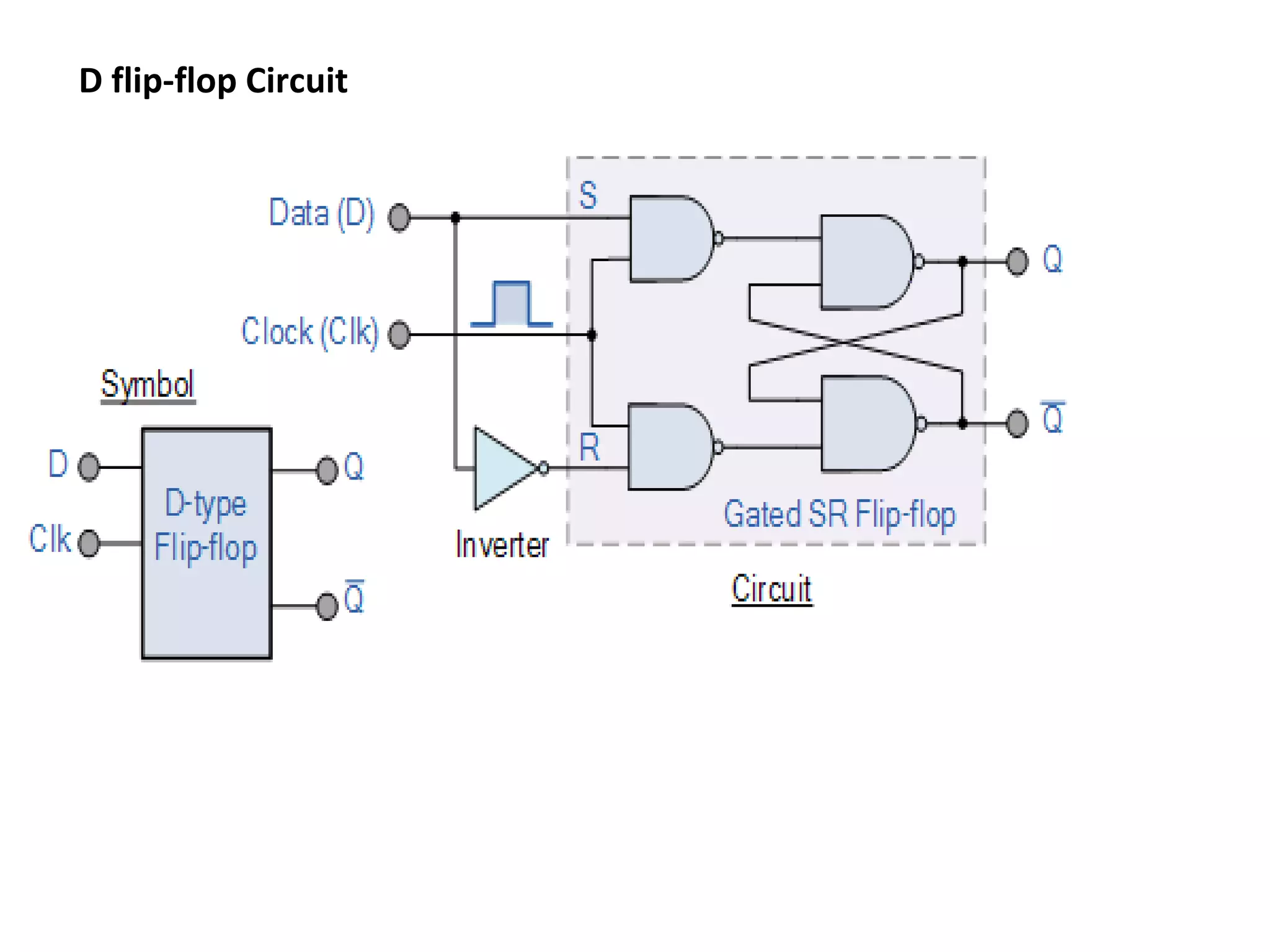

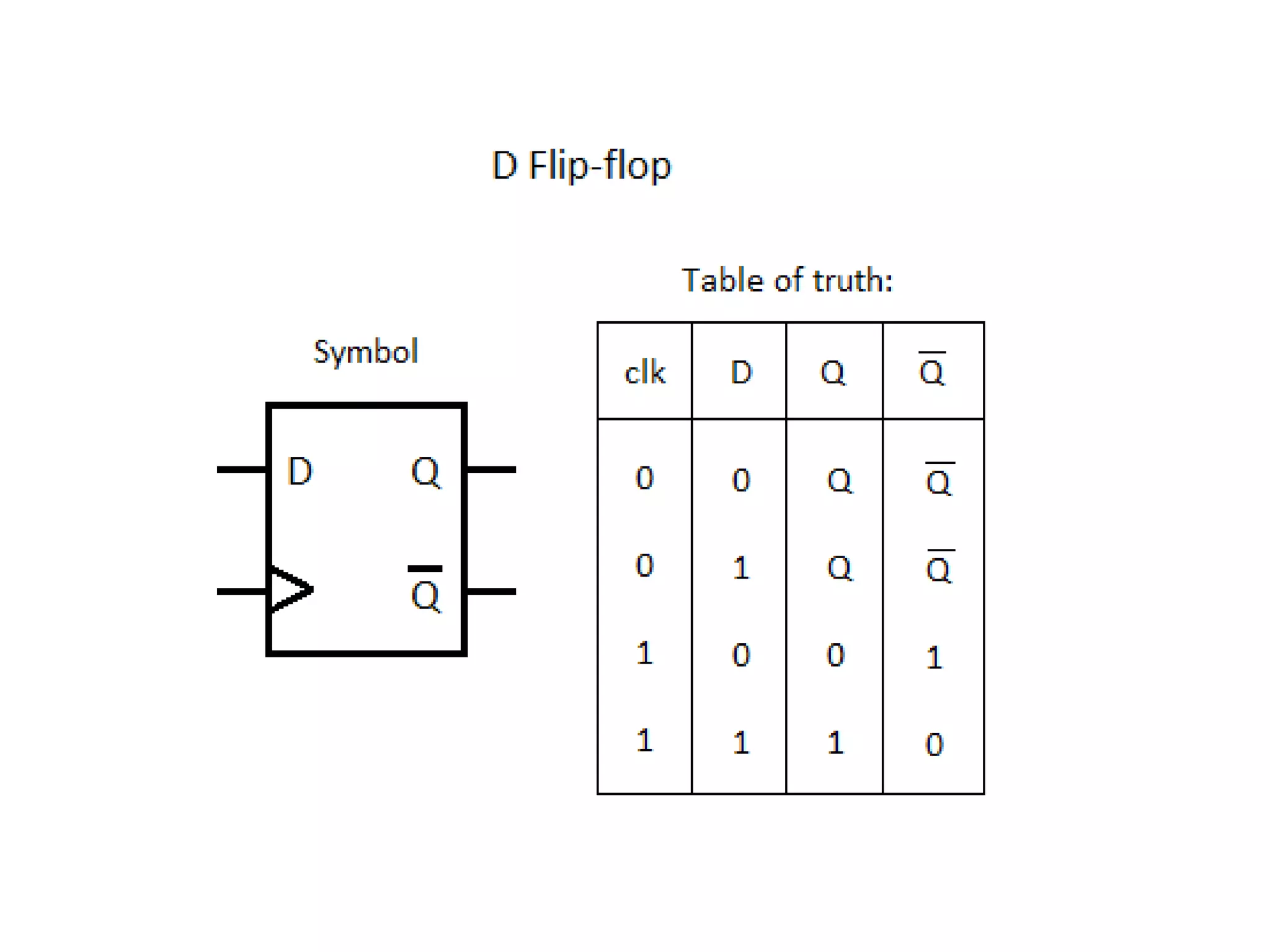

The document discusses the design and analysis of a D-flip flop. It begins by introducing flip flops and their use for storing state information. It then discusses the need for a D-flip flop due to limitations in the basic SR flip flop. A D-flip flop overcomes these limitations using a gated SR flip flop with an inverter between the S and R inputs, allowing a single data input. The circuit and working of the D-flip flop are shown, noting it will store and output the data input while the clock is high.