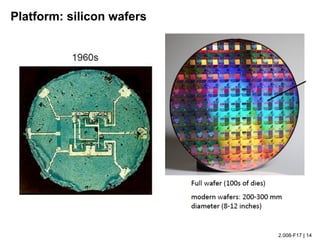

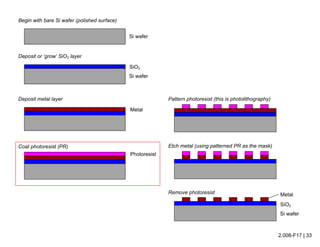

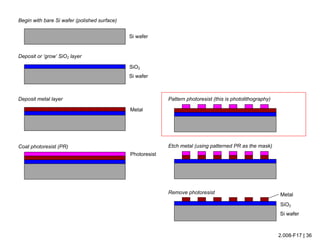

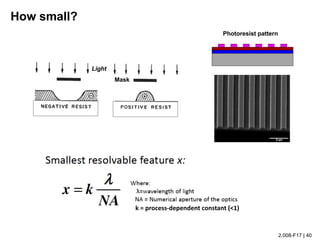

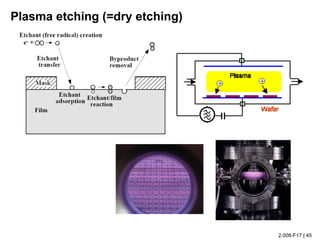

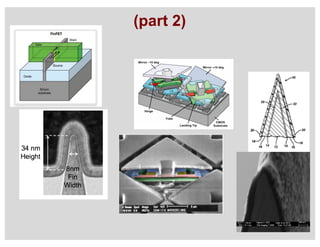

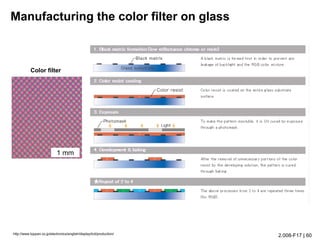

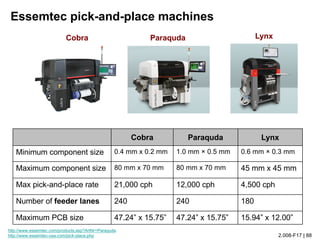

The document discusses key manufacturing technologies for electronic products, focusing on semiconductor manufacturing processes including integrated circuit processing and circuit board assembly. It highlights various techniques such as photolithography, etching, and thin film deposition, as well as equipment costs and design considerations. Additionally, it addresses developments in transistor technology and discusses the implications of manufacturing on electronic product design and functionality.