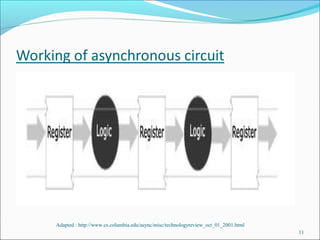

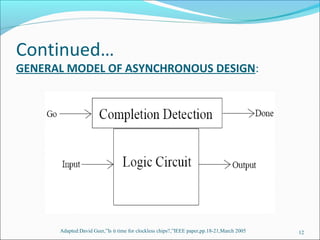

This document discusses synchronous and asynchronous circuits. Synchronous circuits use a global clock signal to coordinate timing, but this limits speed and wastes power. Asynchronous circuits coordinate activity through local handshaking signals instead of a clock. They can run at each component's natural speed without wasted idle time. Asynchronous circuits have advantages like higher speed, lower power usage, and less electromagnetic interference compared to synchronous circuits. However, asynchronous design is more complex and lacks mature design tools.