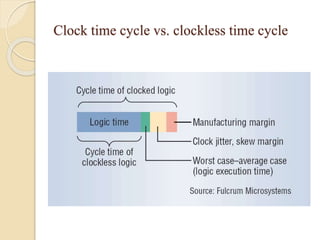

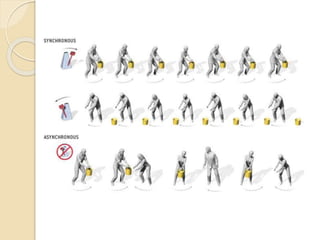

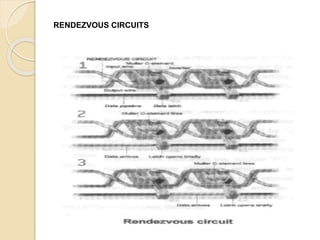

This document discusses asynchronous computer chips as an alternative to traditional synchronous chips. Synchronous chips rely on a central clock, which poses problems like slow speed, wasted energy distributing the clock globally, and high power consumption from the clocks themselves. Asynchronous chips do not use a central clock and instead rely on handshake signals between components to transfer data only when needed. They allow different parts to work at different speeds and immediately pass results. While asynchronous chips have advantages like lower power usage and less noise, challenges remain in interfacing them with synchronous devices and a lack of expertise and tools available. Overall, the document argues that asynchronous chips may help address future issues with clocked designs as chip complexity increases.