This document provides an overview of digital systems fundamentals, including:

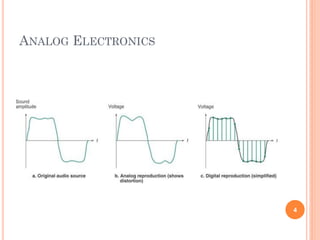

- Analog signals have continuous values while digital signals can only have discrete values (0 or 1).

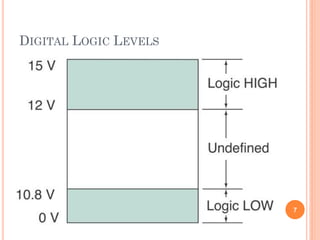

- Digital electronics uses binary logic levels to represent information, with a high voltage representing 1 and a low voltage representing 0.

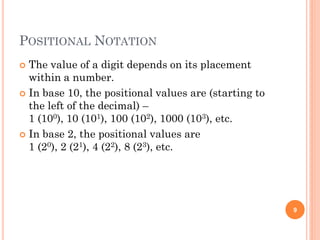

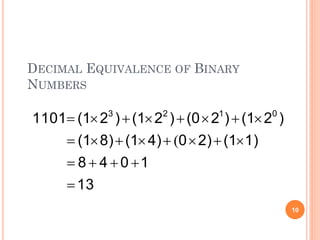

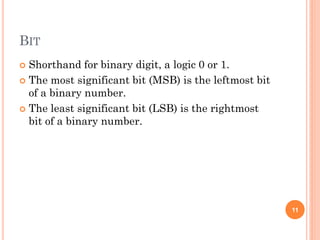

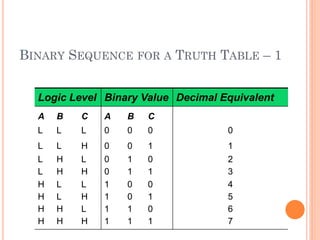

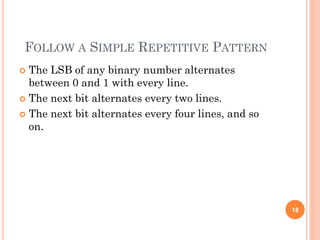

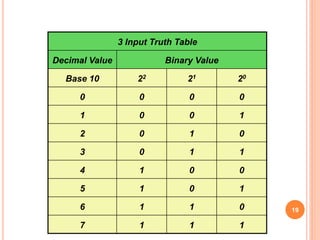

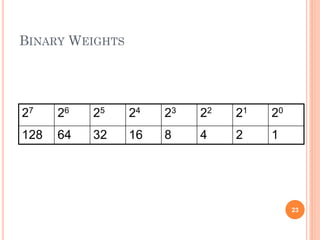

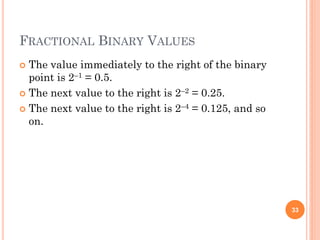

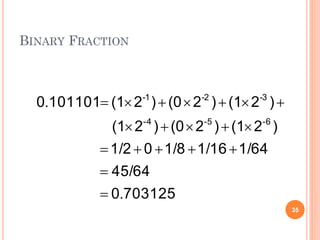

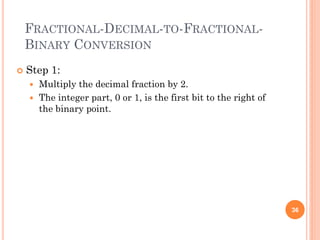

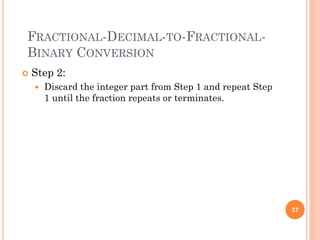

- The binary number system uses positional notation to represent numbers using only the digits 0 and 1.

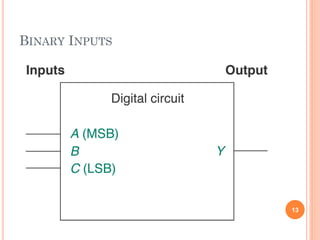

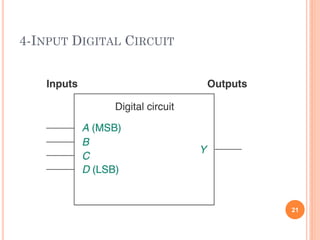

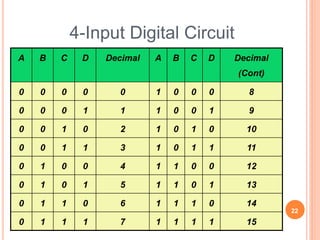

- Digital circuits operate on binary inputs and outputs, with truth tables listing all possible input-output combinations for a logic gate or circuit.