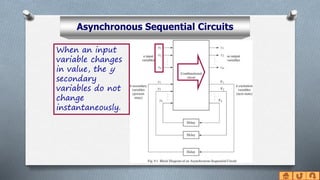

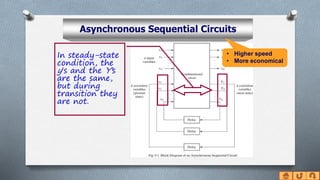

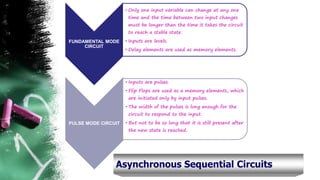

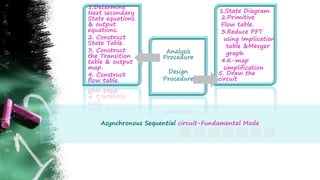

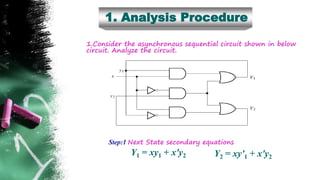

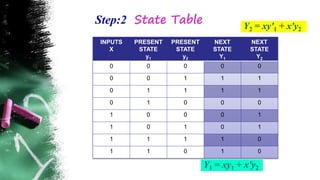

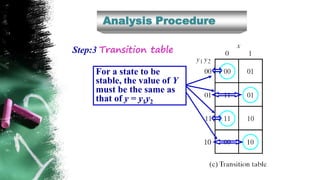

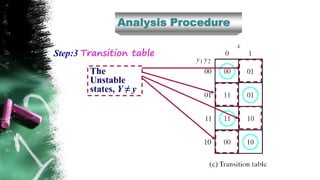

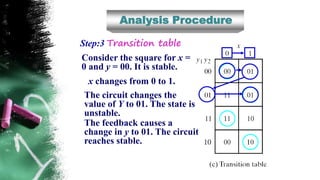

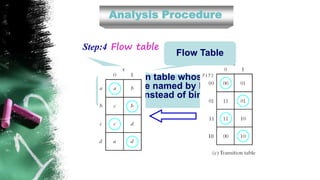

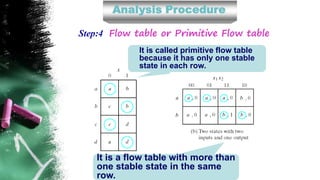

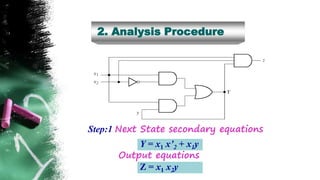

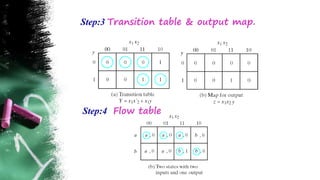

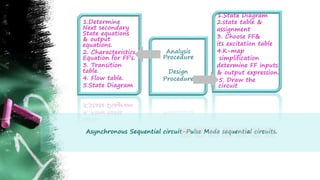

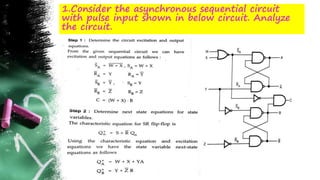

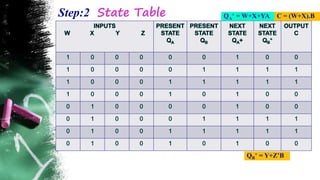

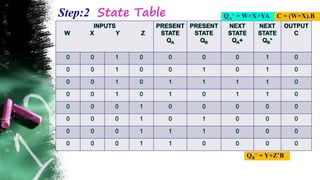

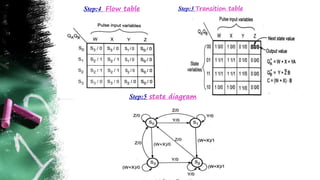

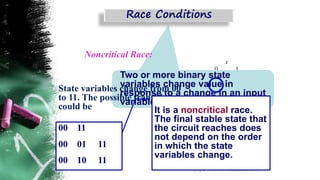

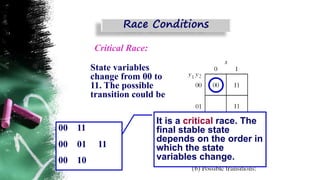

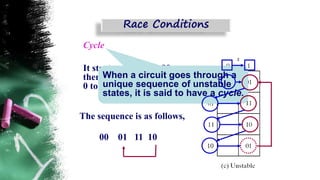

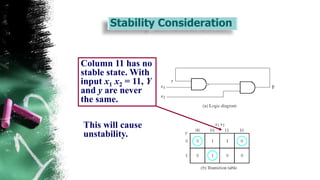

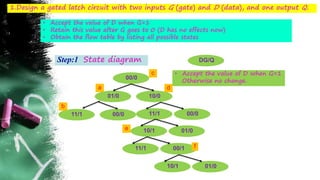

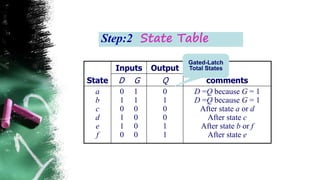

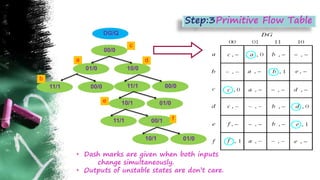

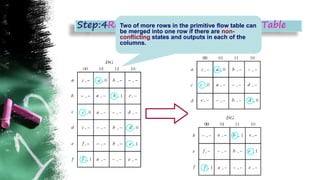

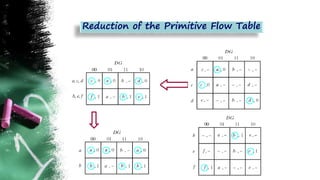

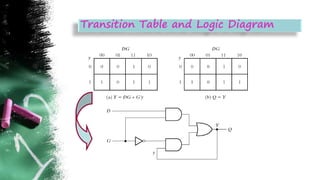

The document discusses asynchronous sequential circuits. It begins by defining asynchronous sequential circuits as circuits that do not use clock pulses, with the internal state changing in response to input variable changes. It then covers different types of asynchronous sequential circuits including fundamental mode and pulse mode circuits. The document outlines the analysis and design procedures for both types of circuits. This includes determining next state equations, constructing state and transition tables, and deriving flow tables to analyze fundamental mode circuits. It also discusses how to analyze and design pulse mode circuits using state tables and flip-flops. Race conditions and stability considerations are reviewed. An example of analyzing and designing a gated latch circuit is provided.