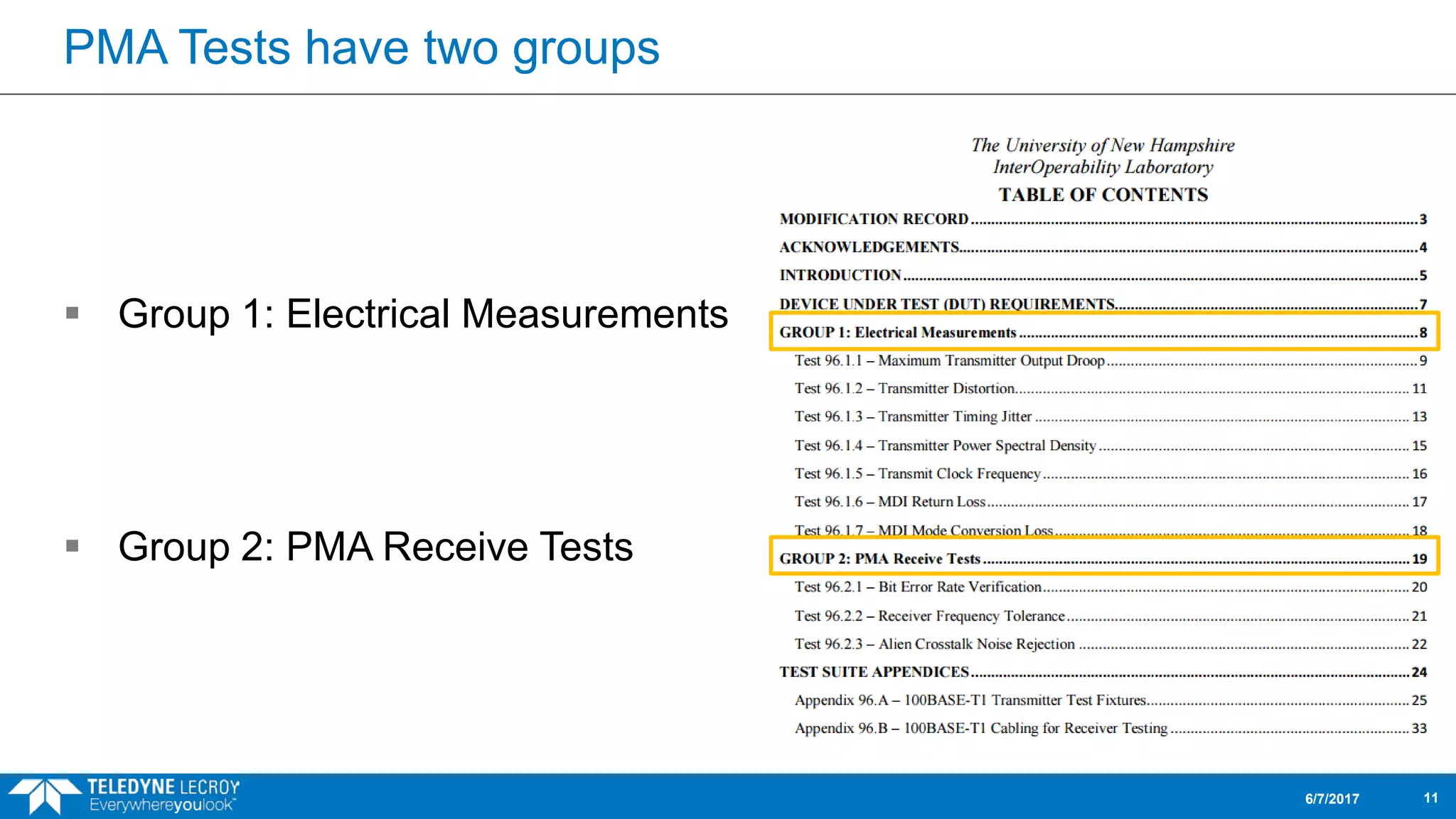

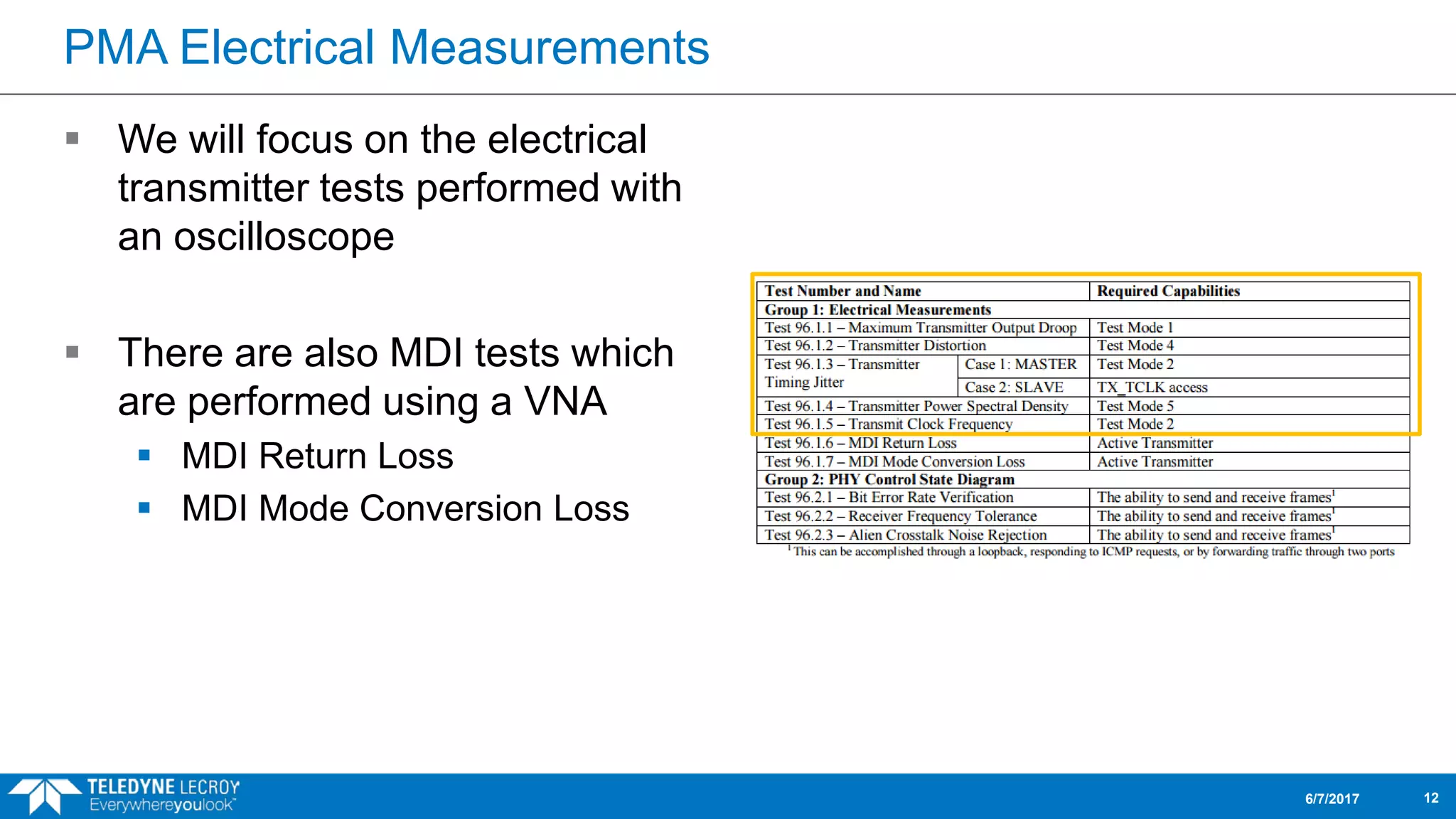

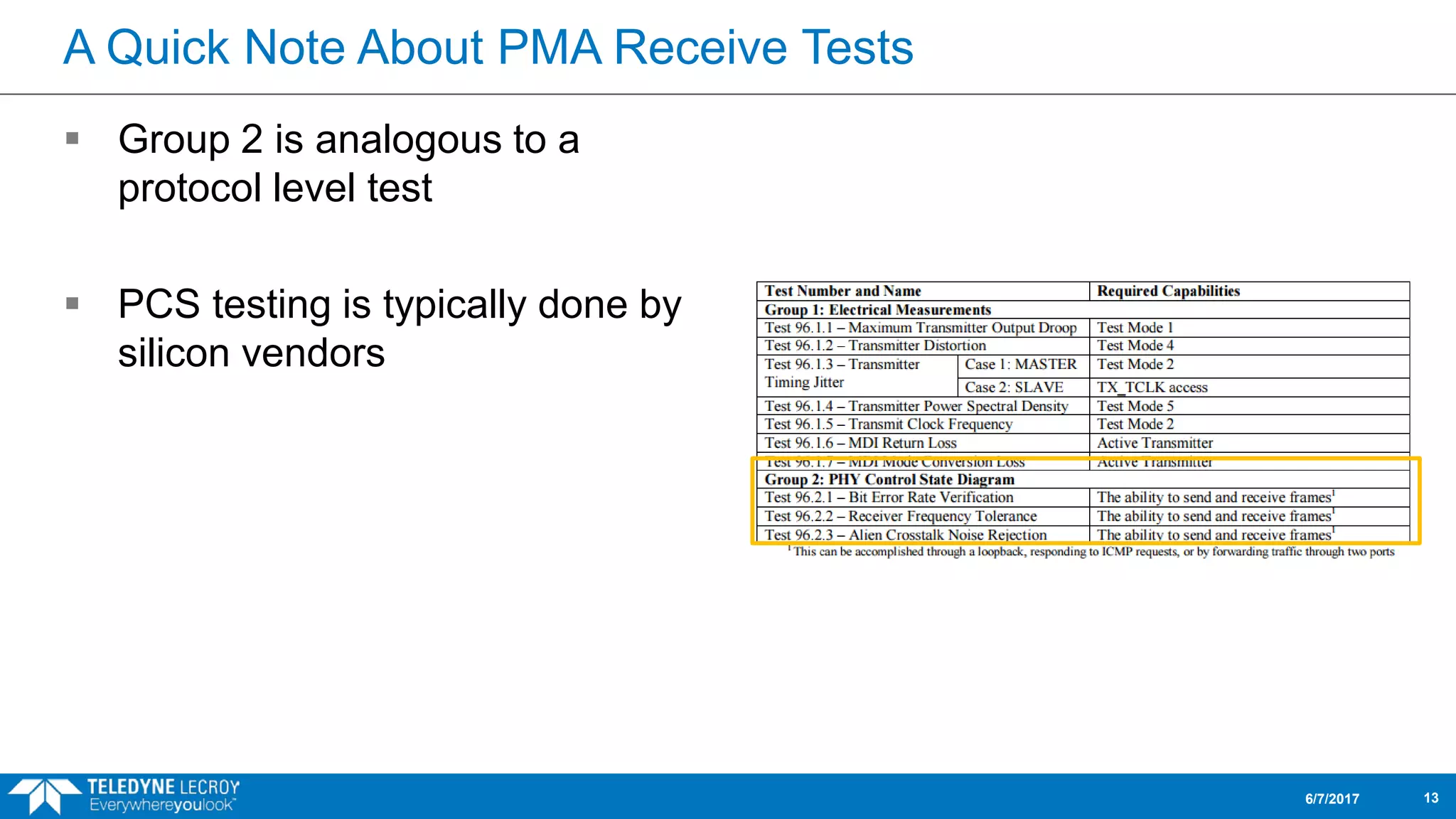

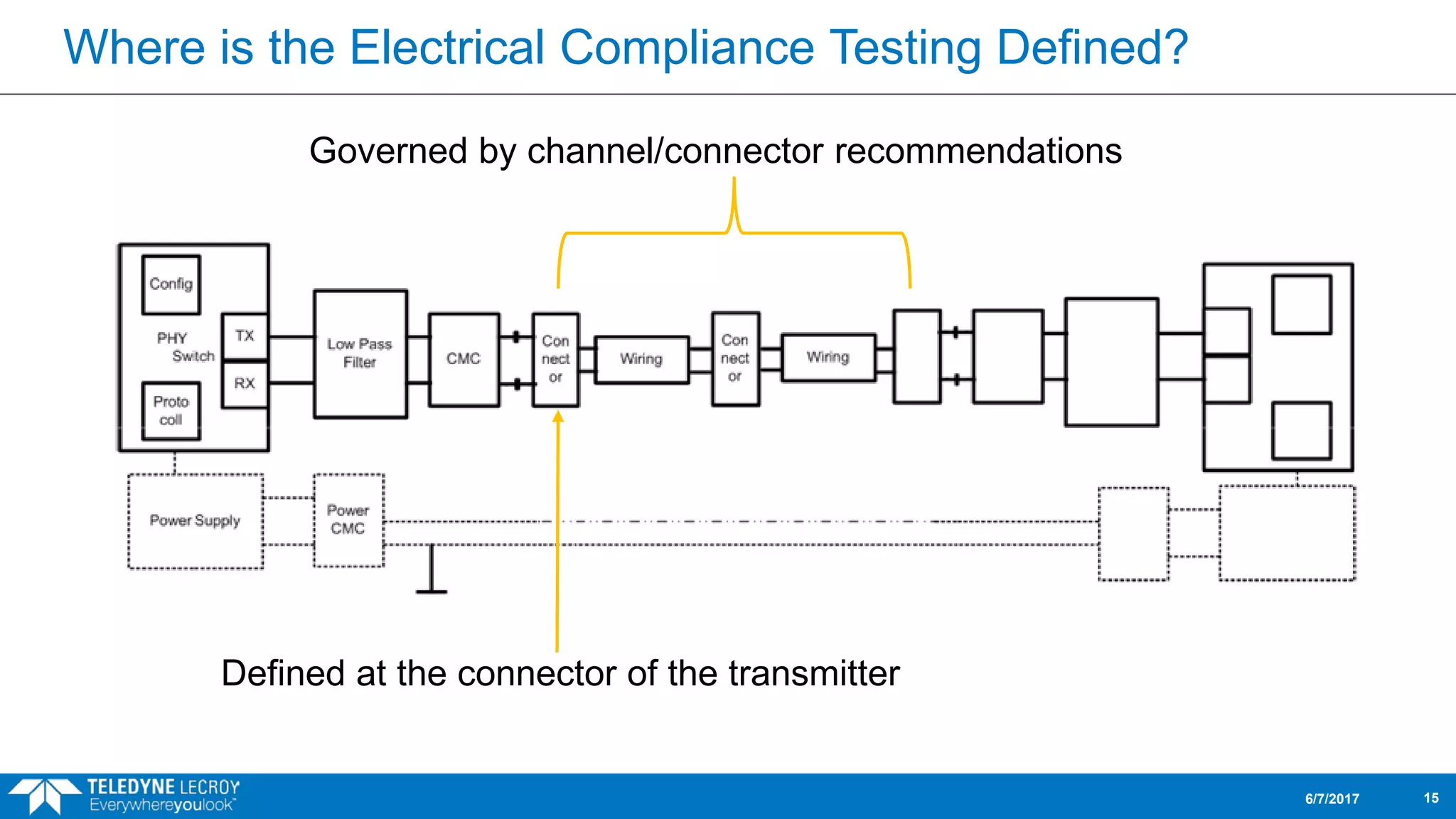

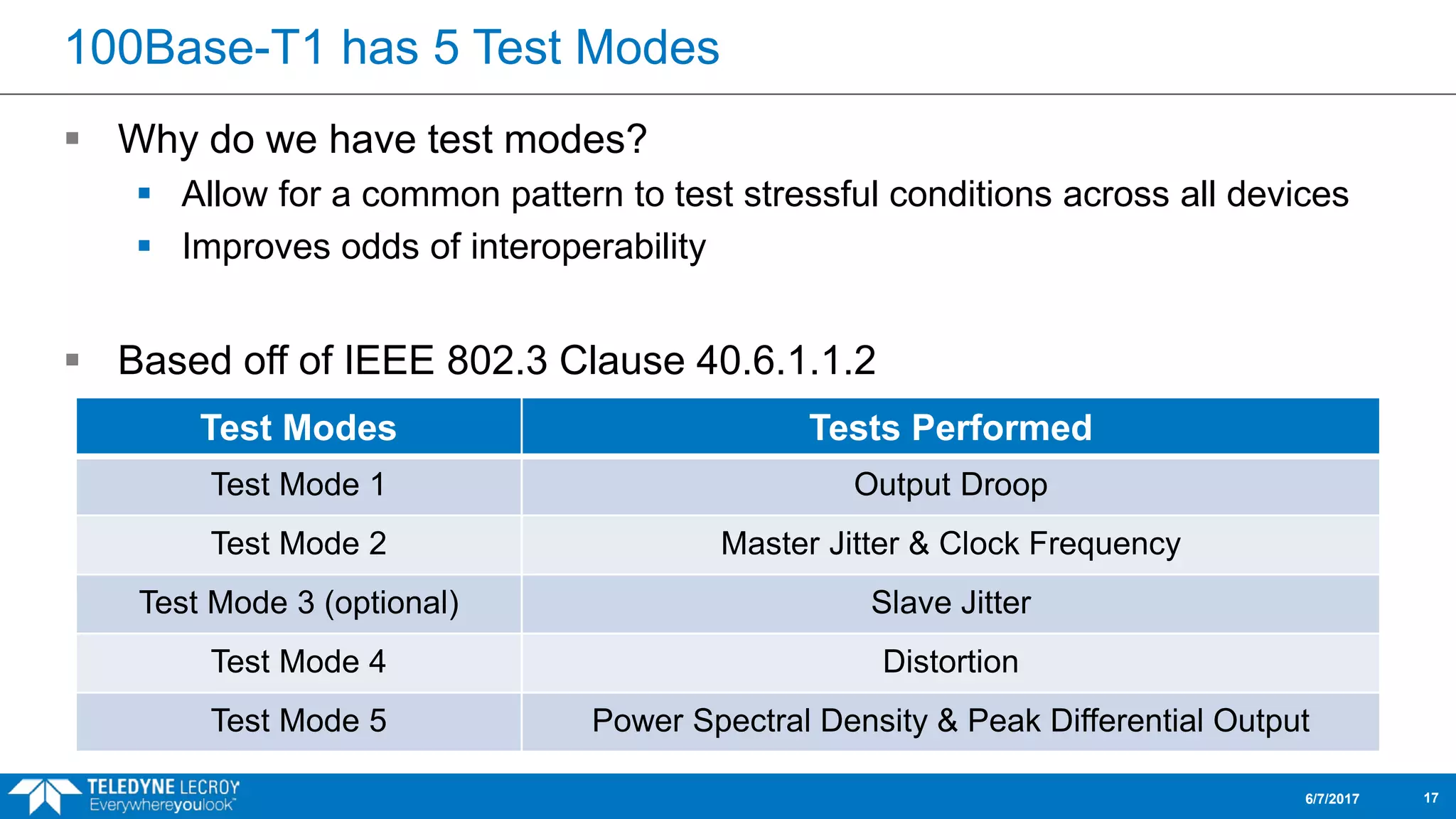

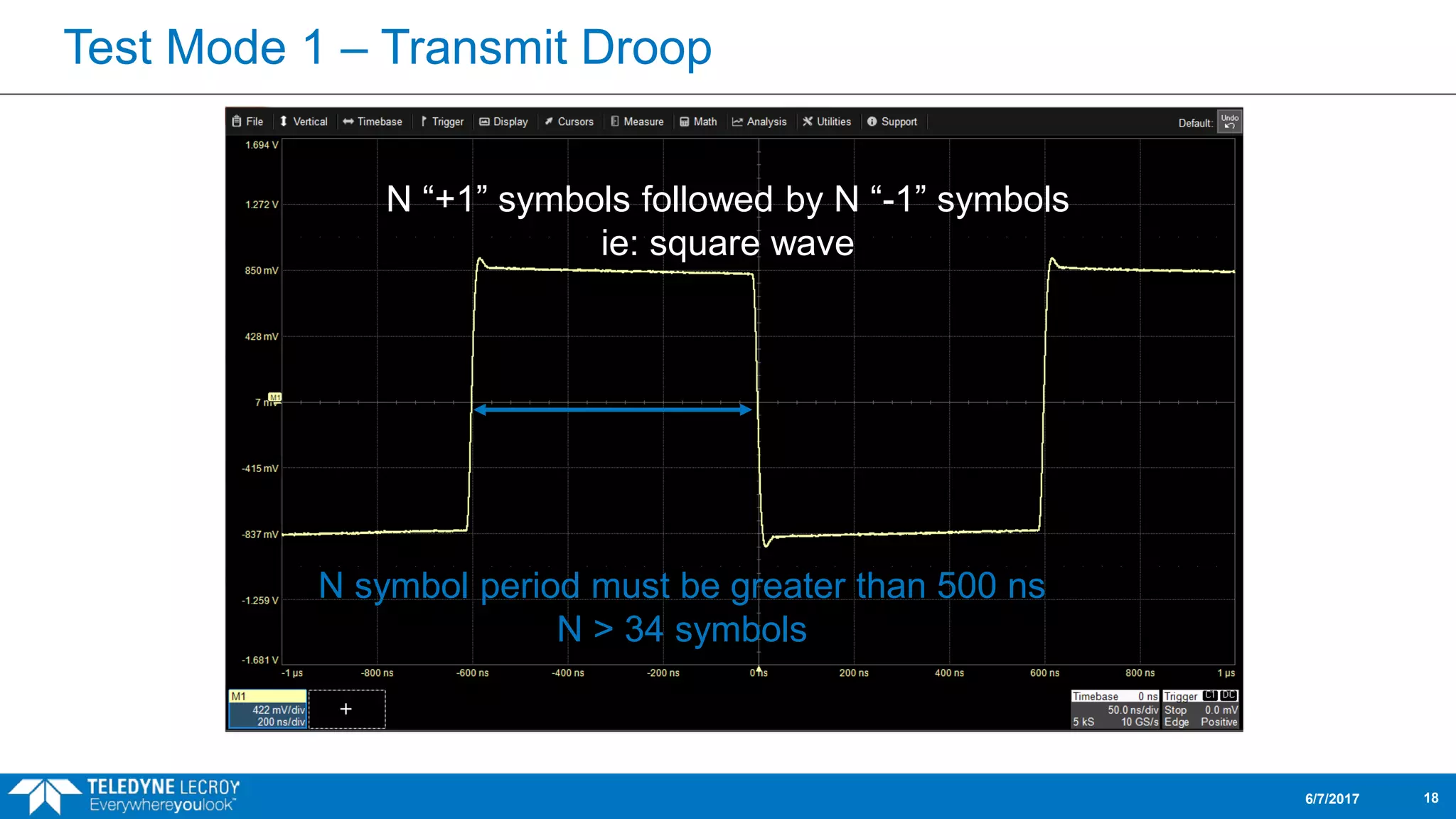

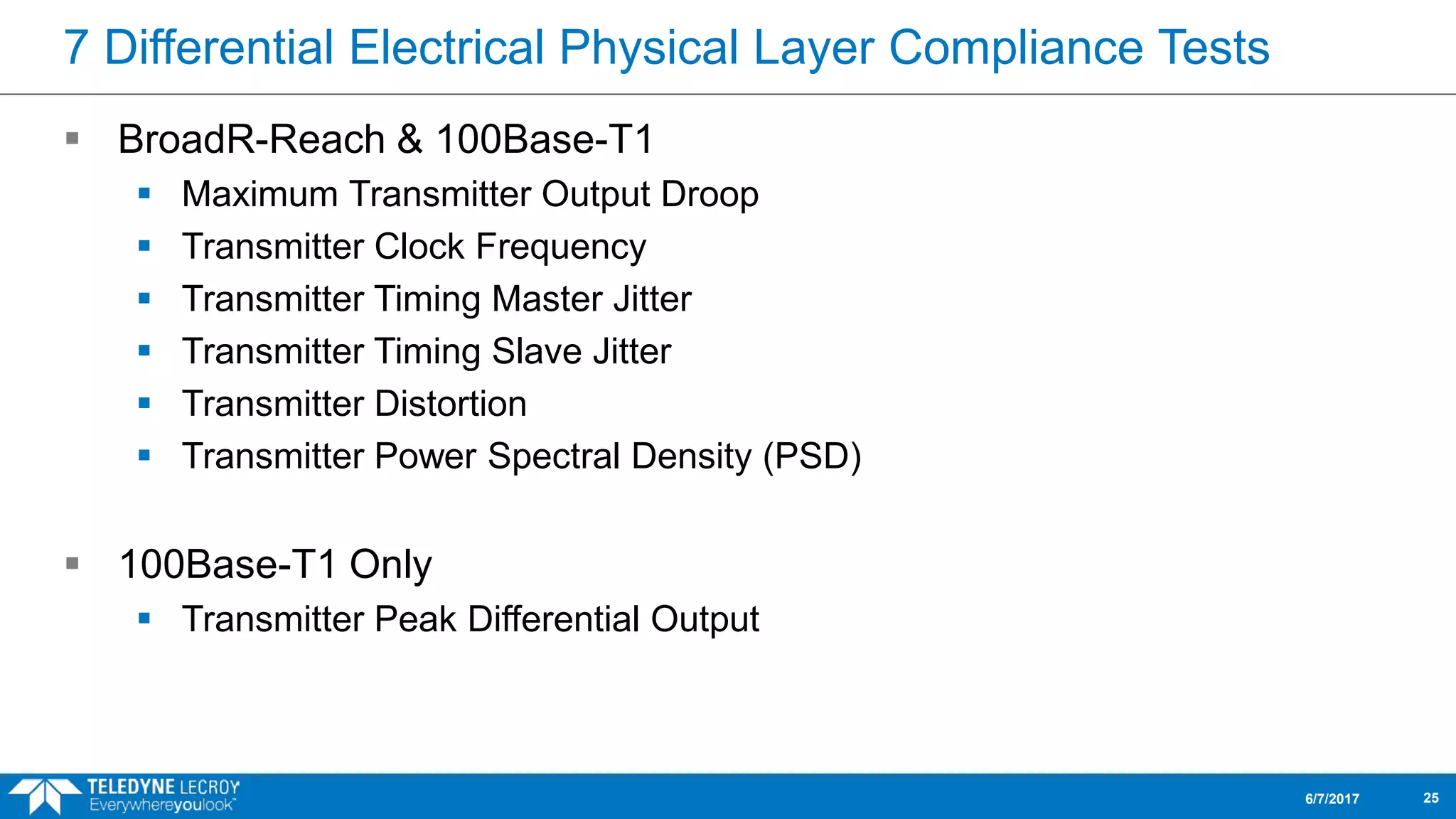

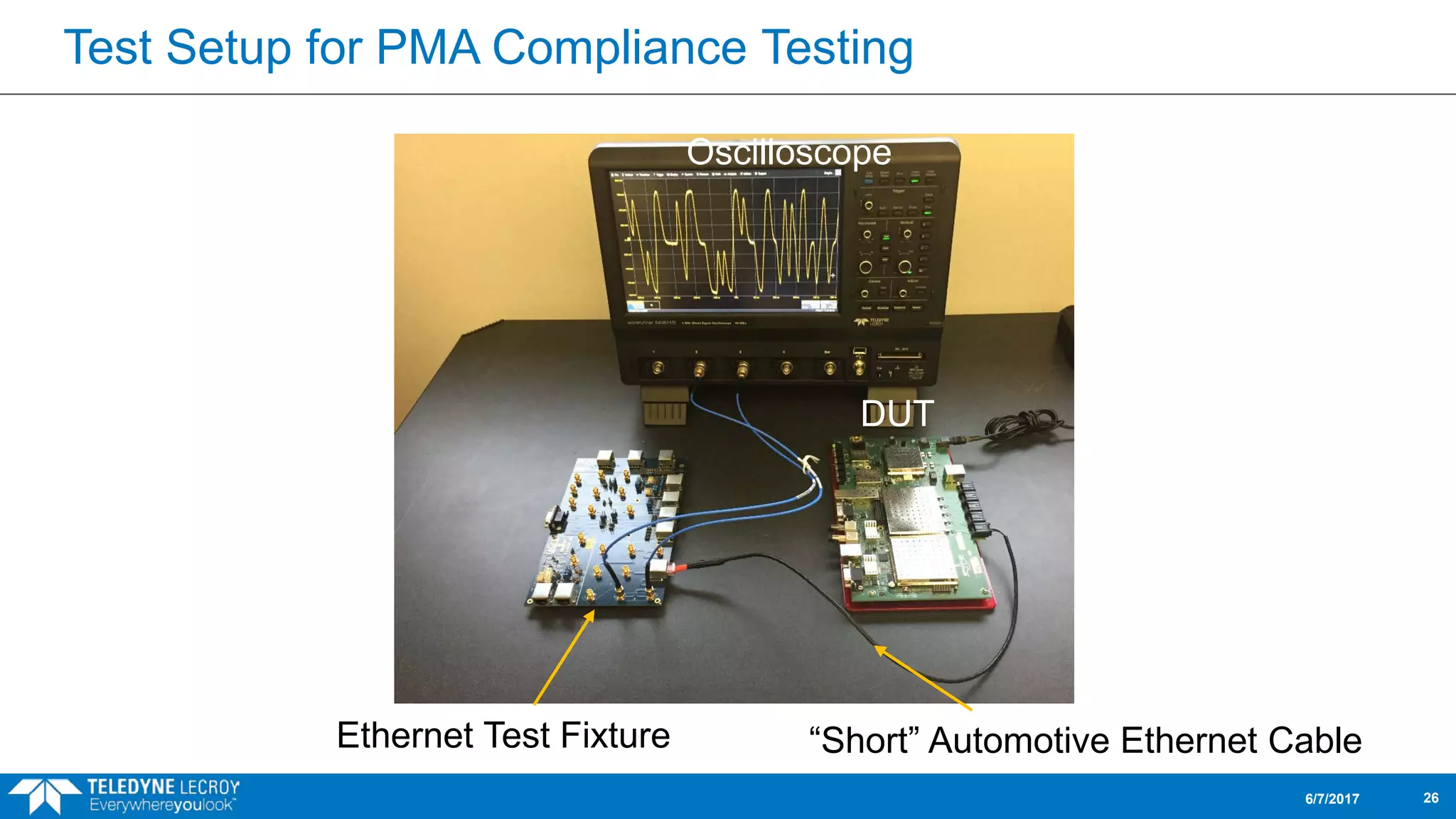

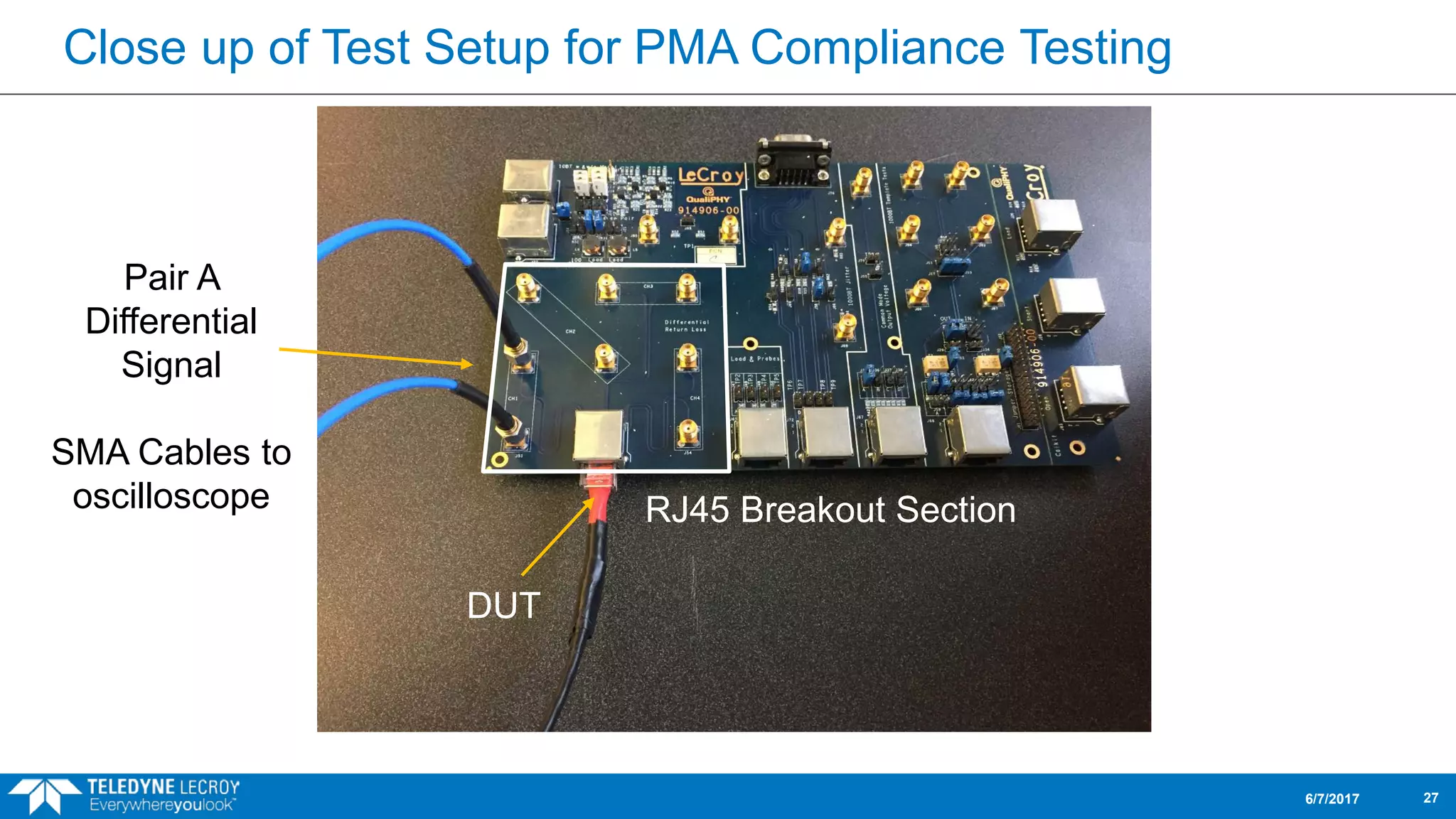

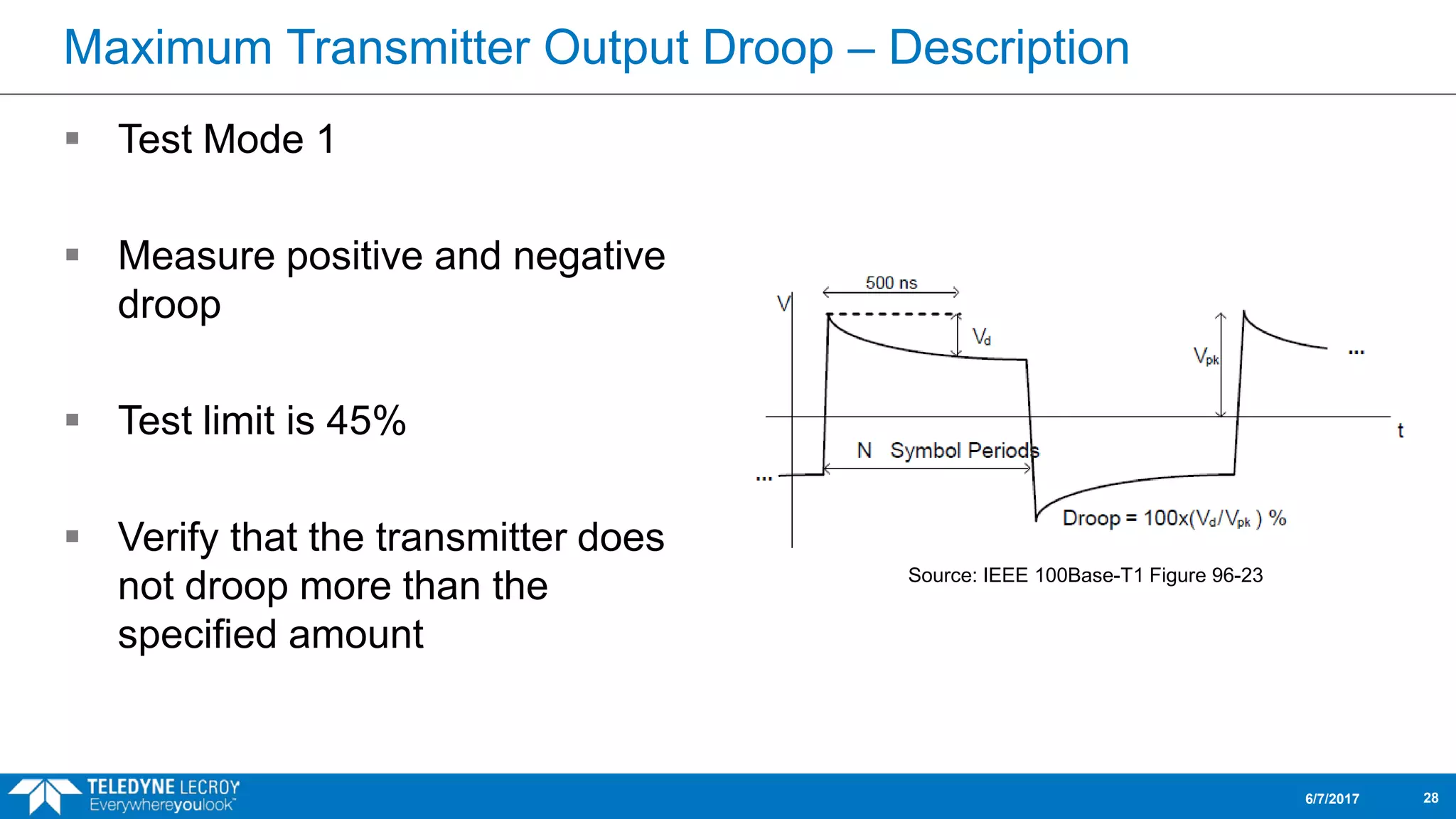

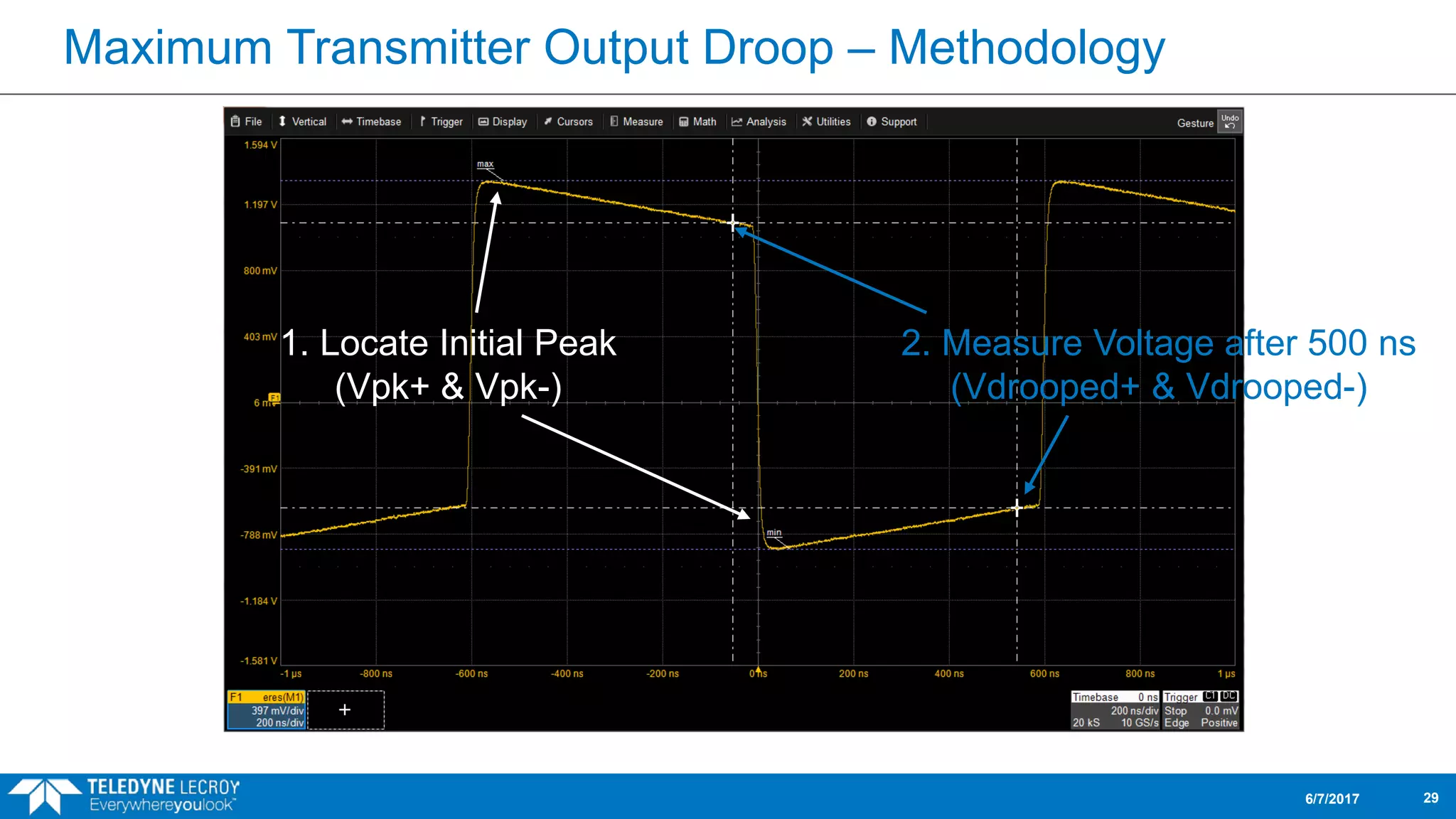

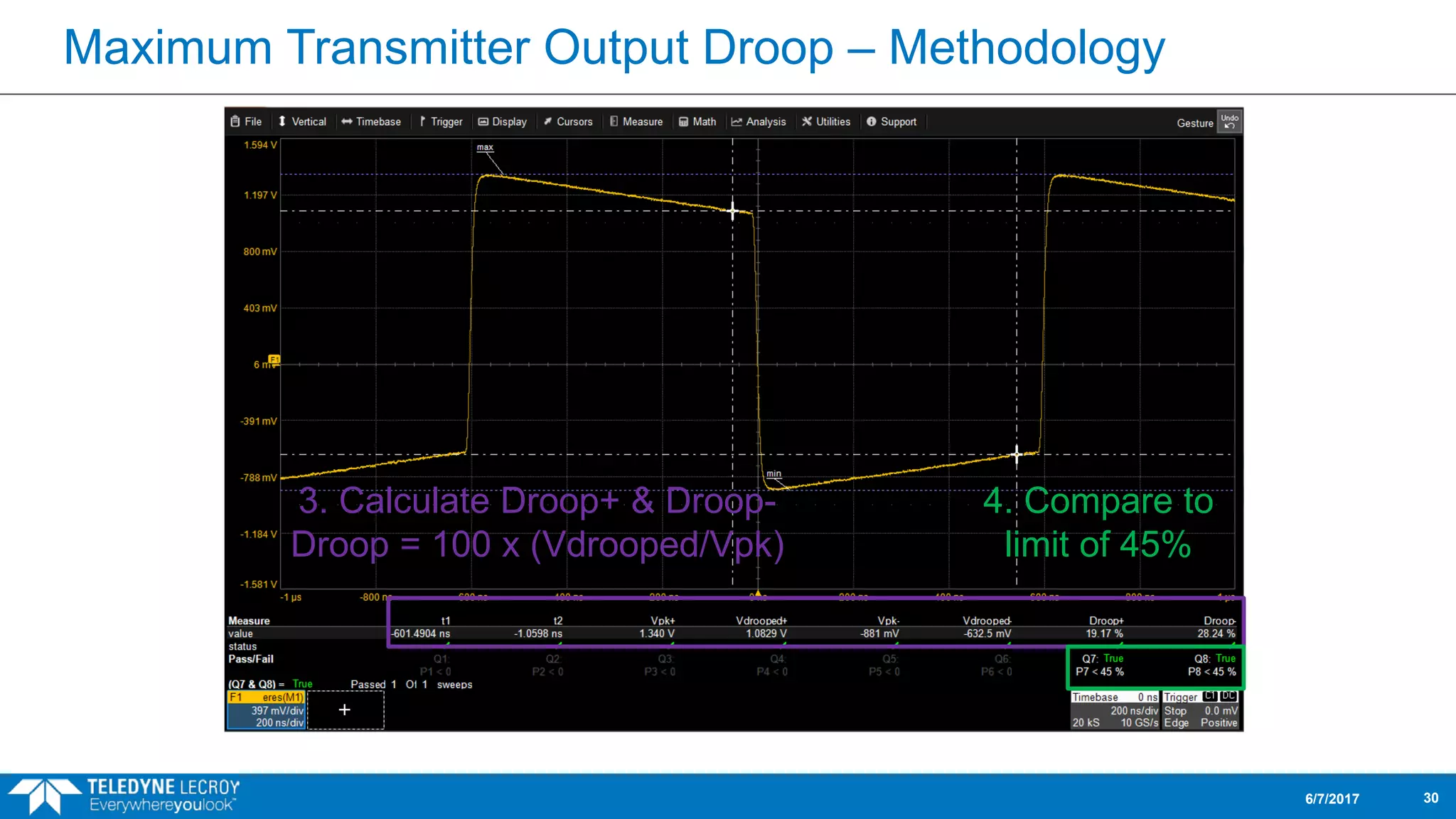

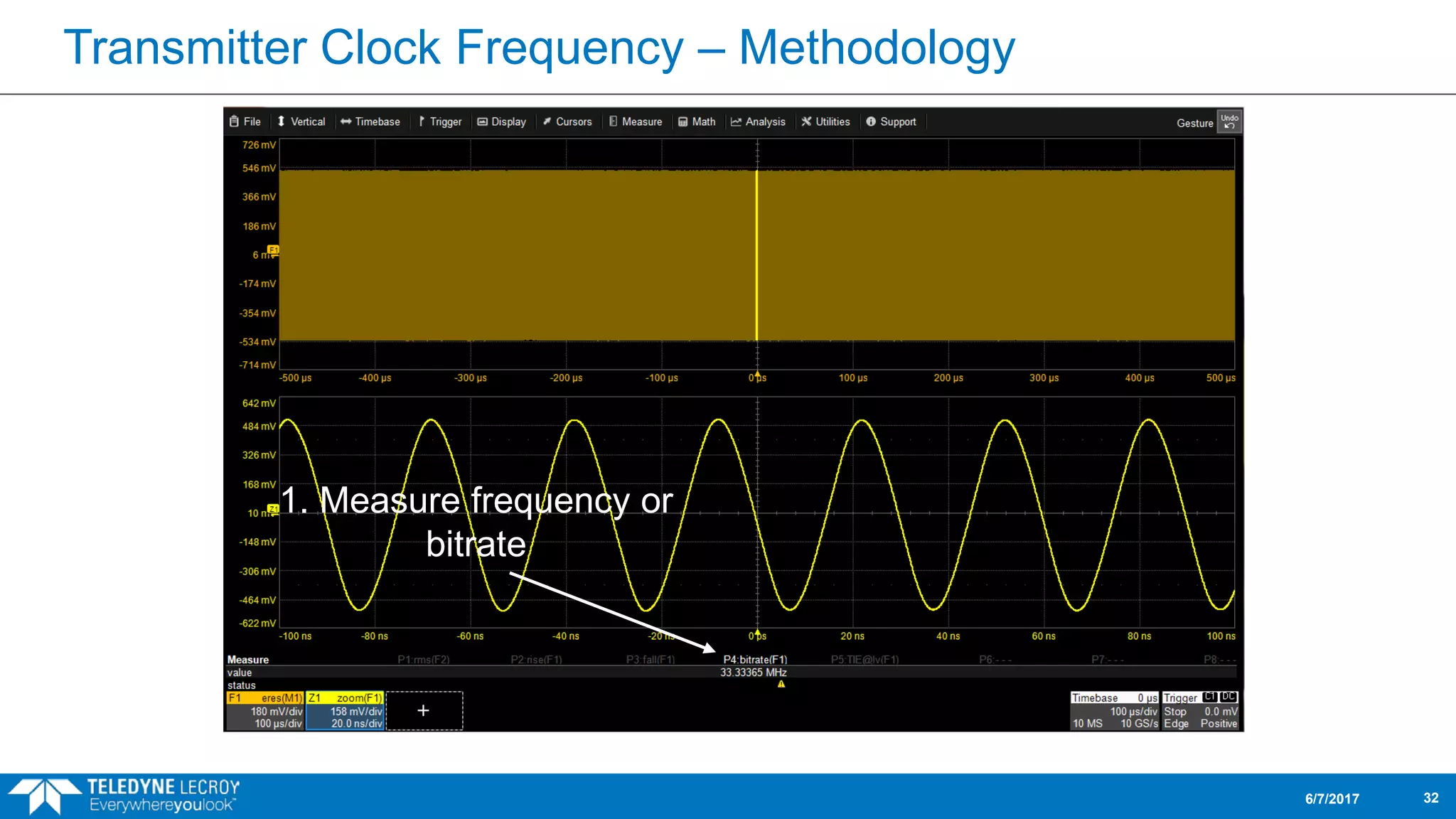

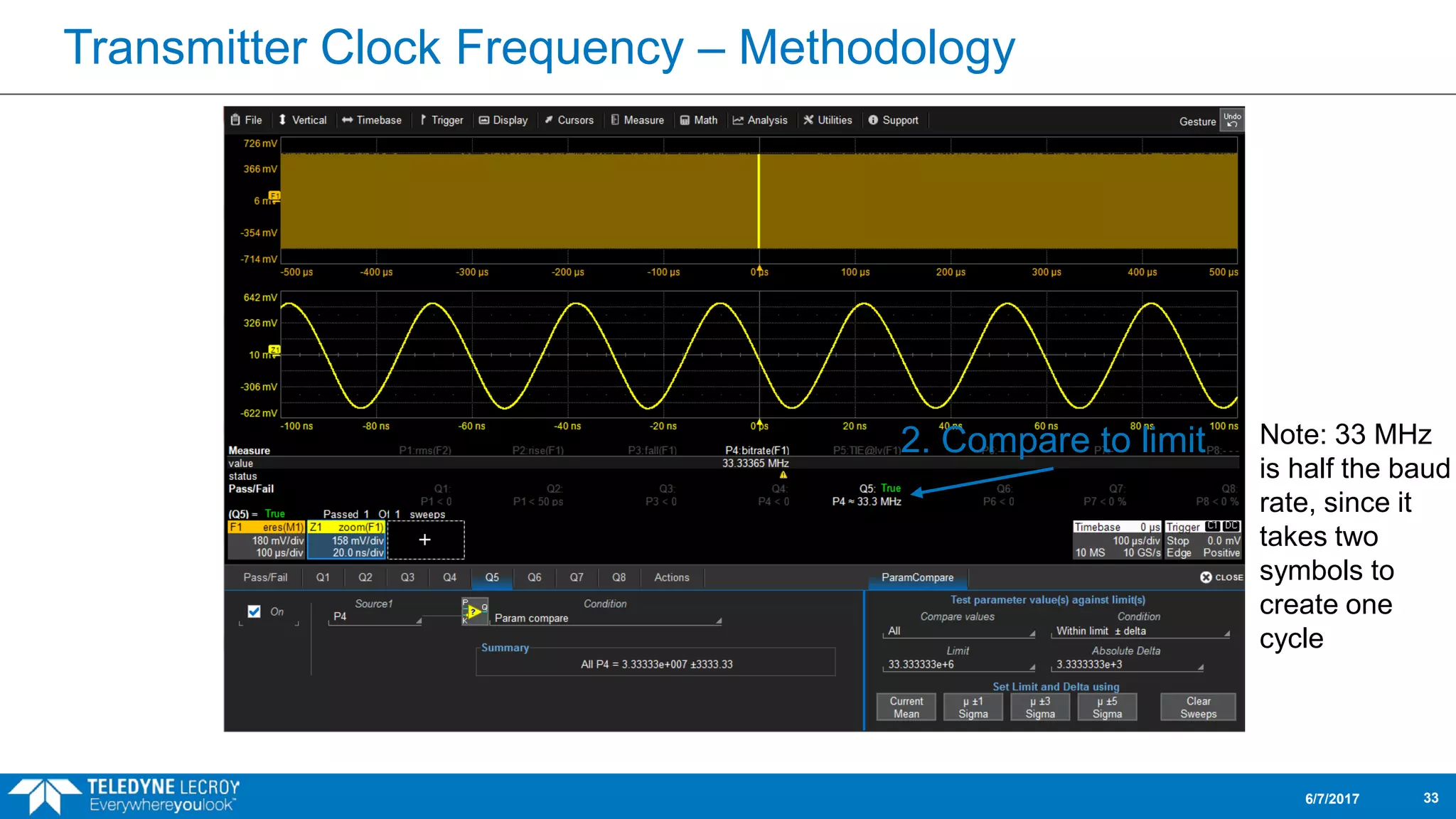

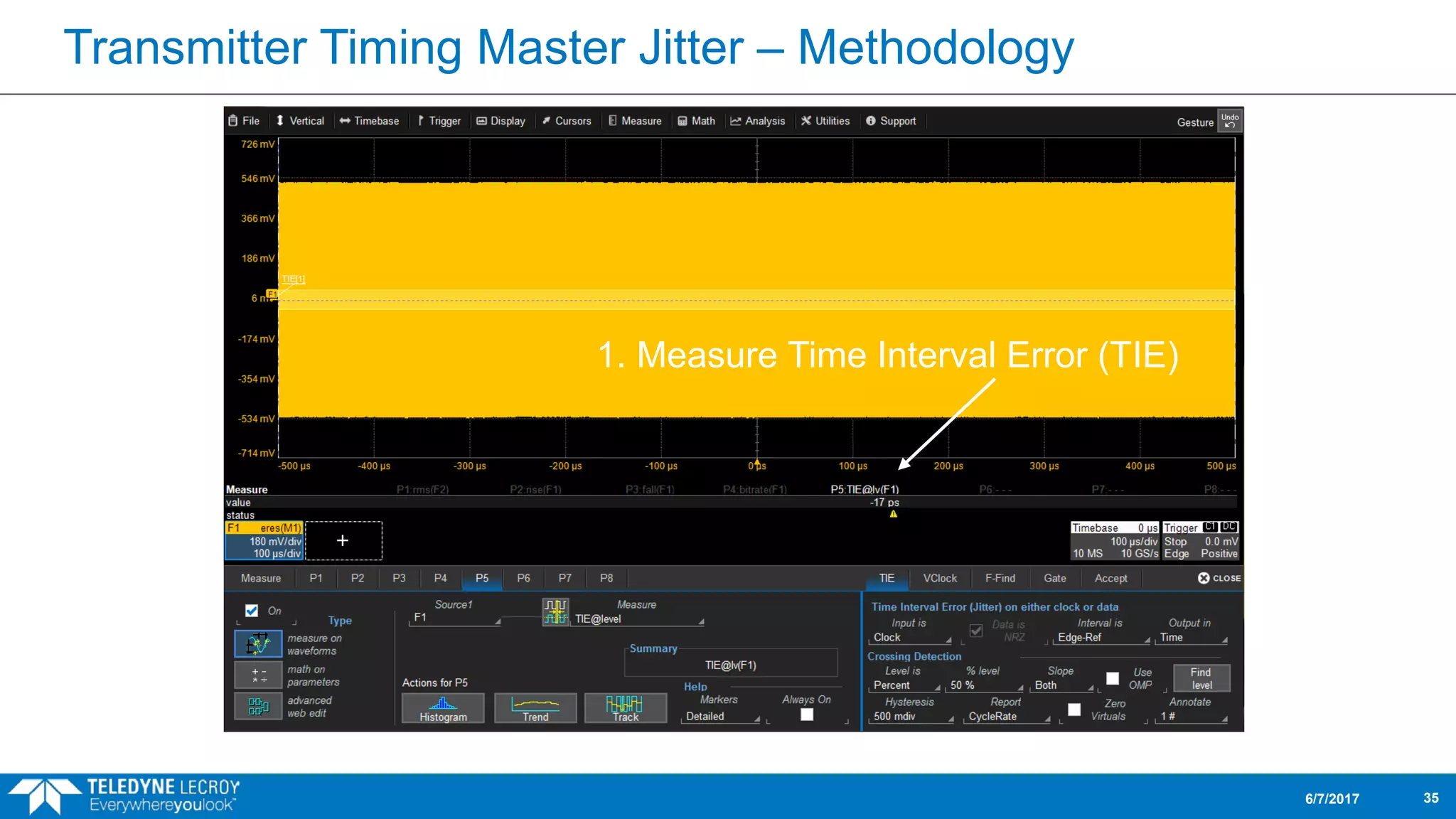

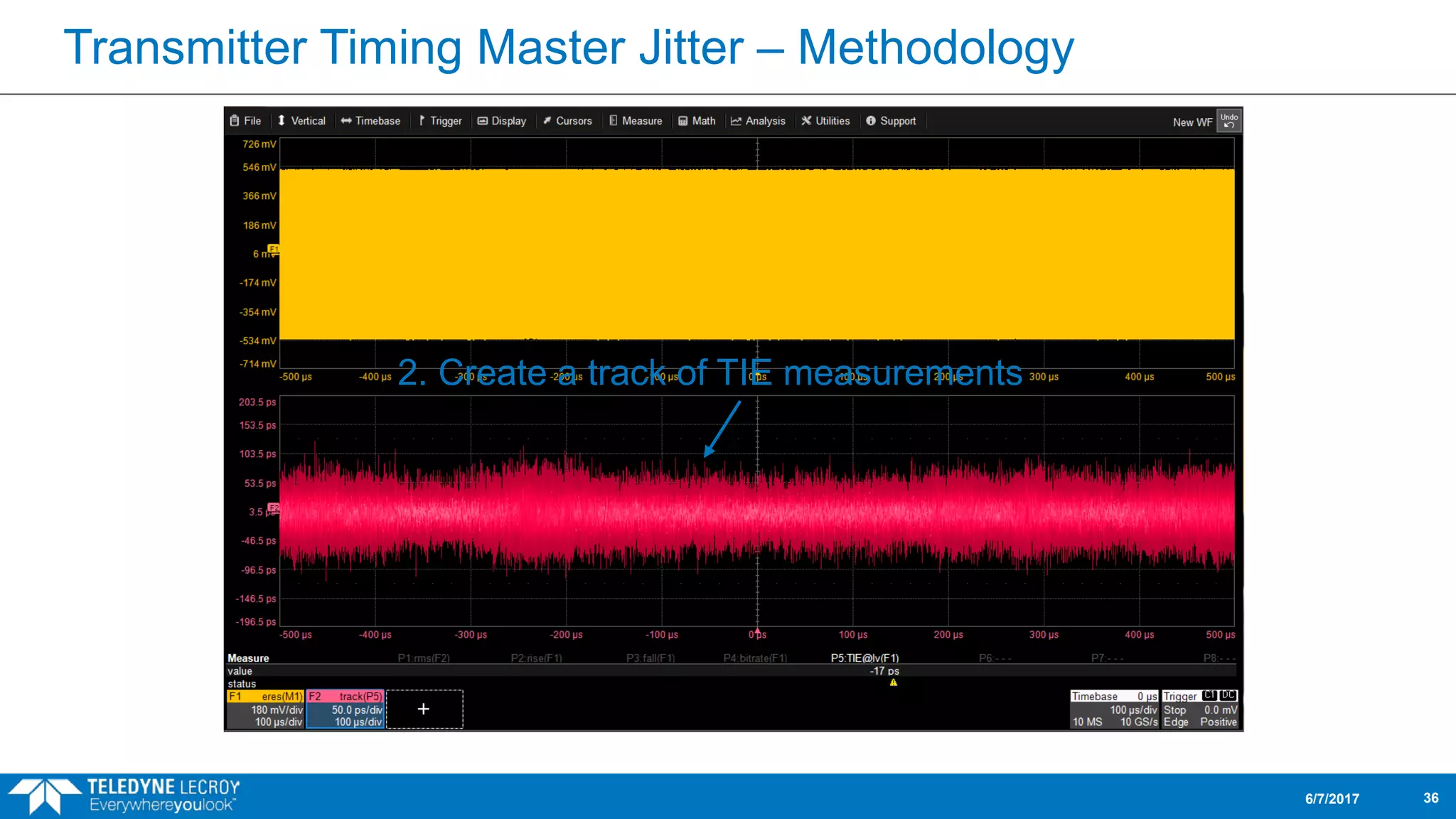

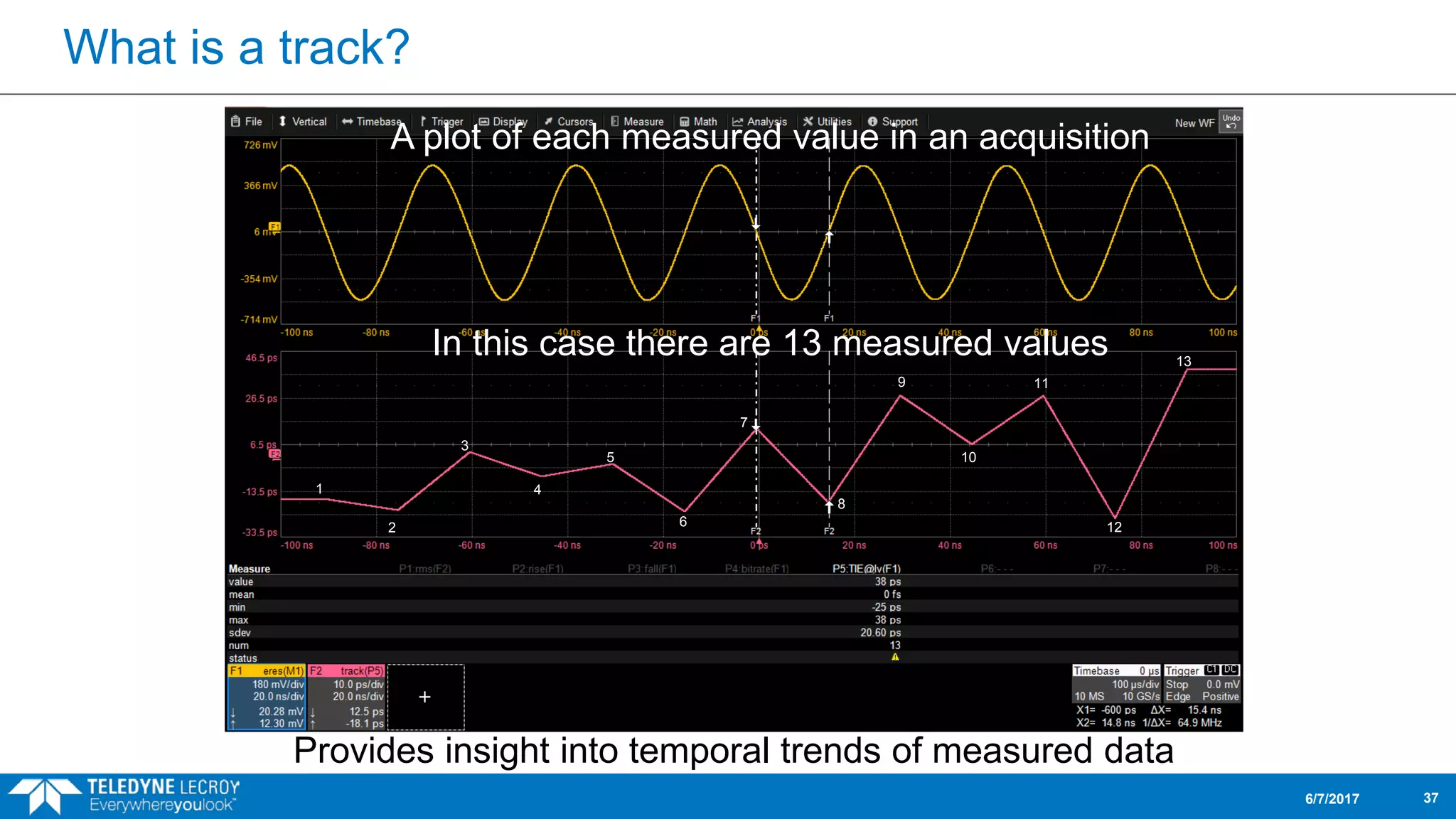

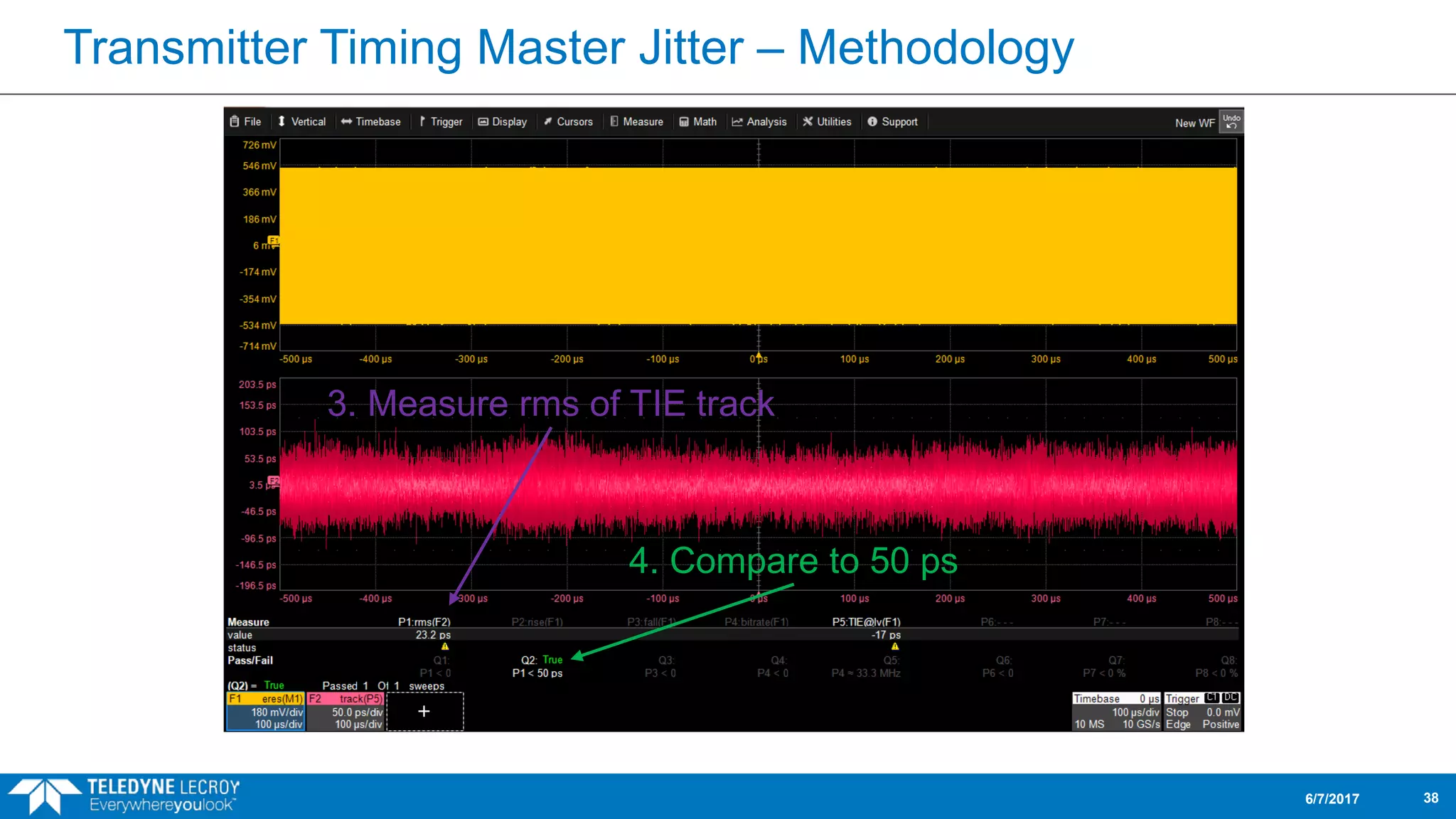

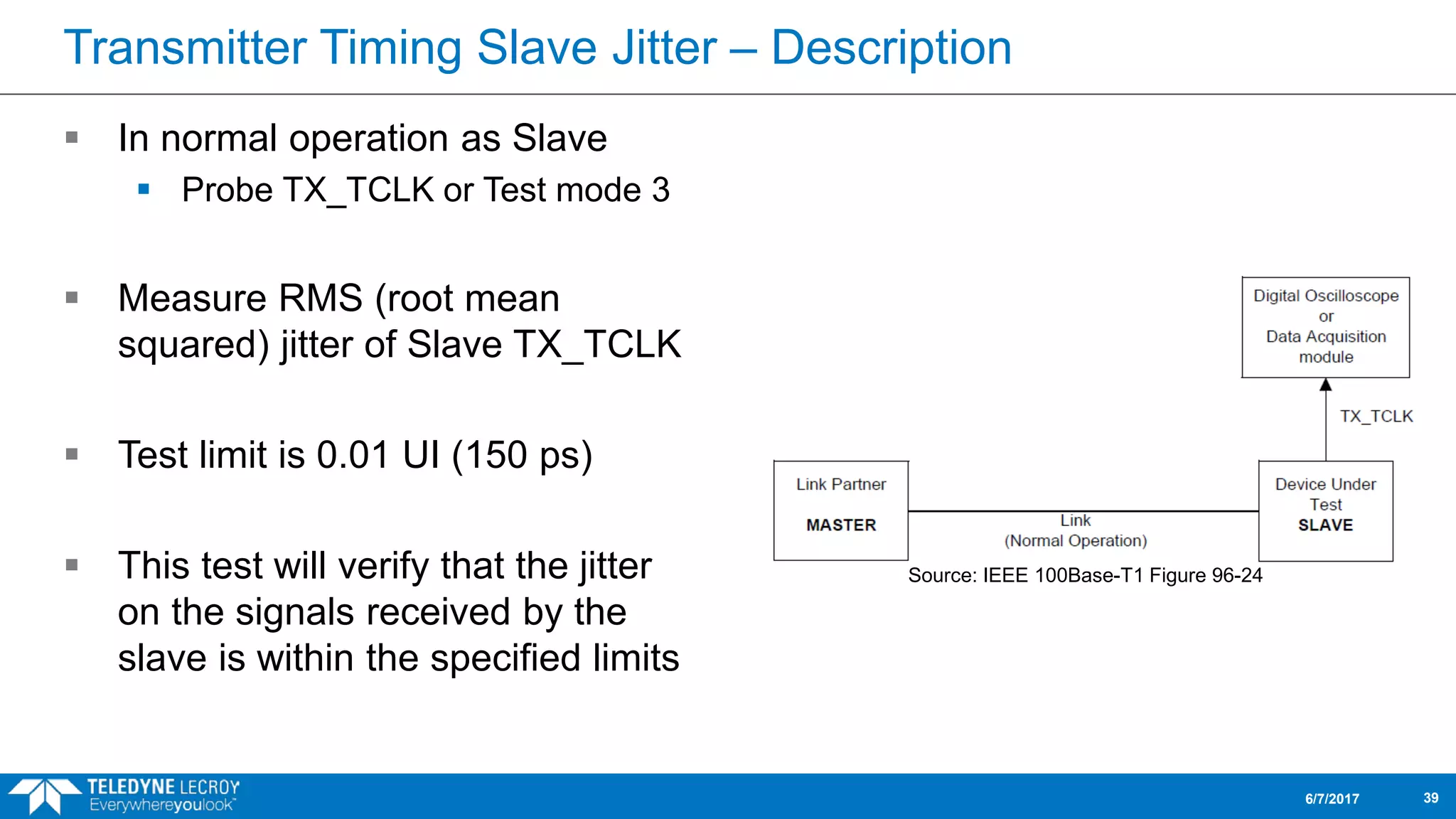

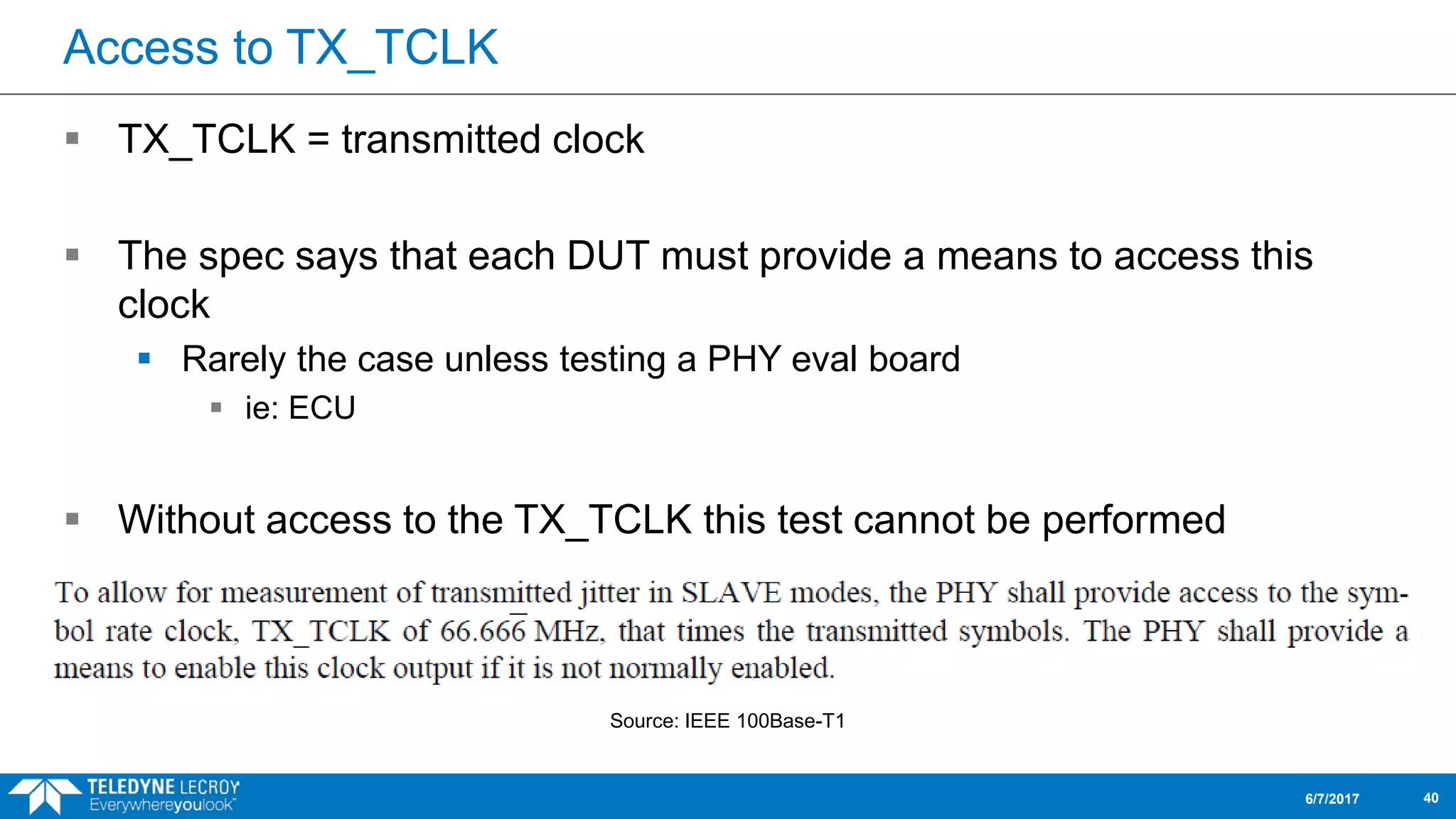

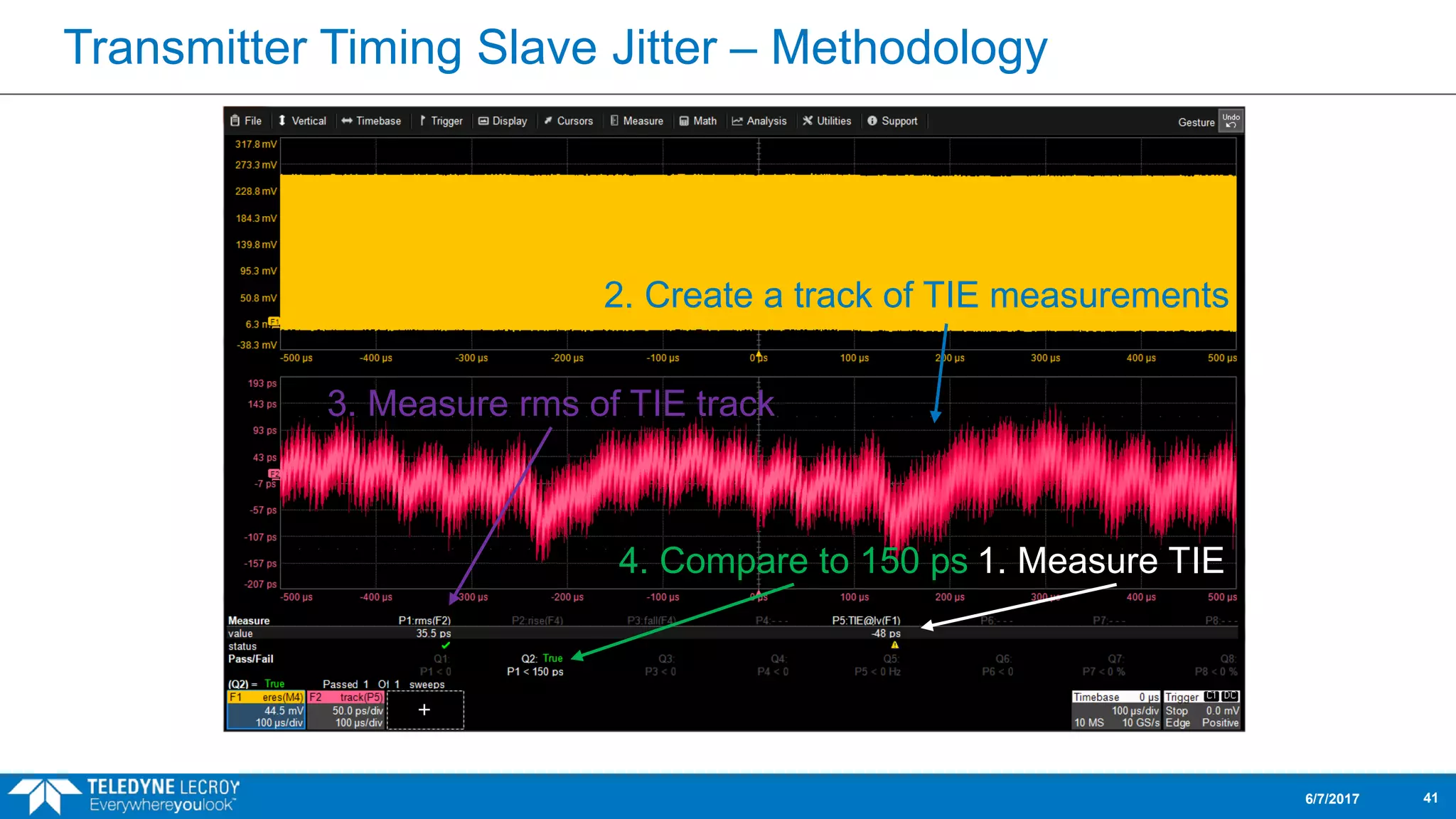

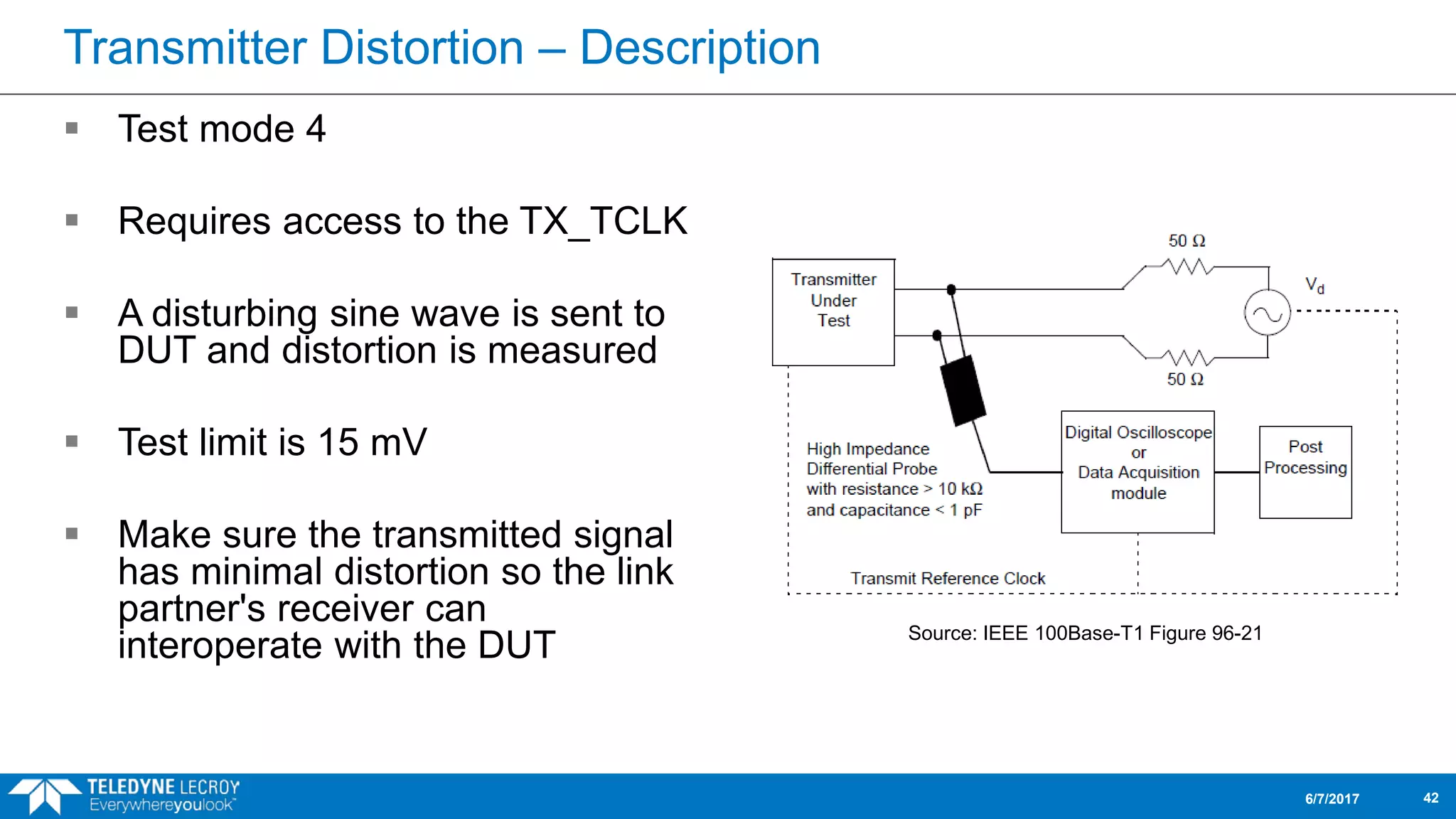

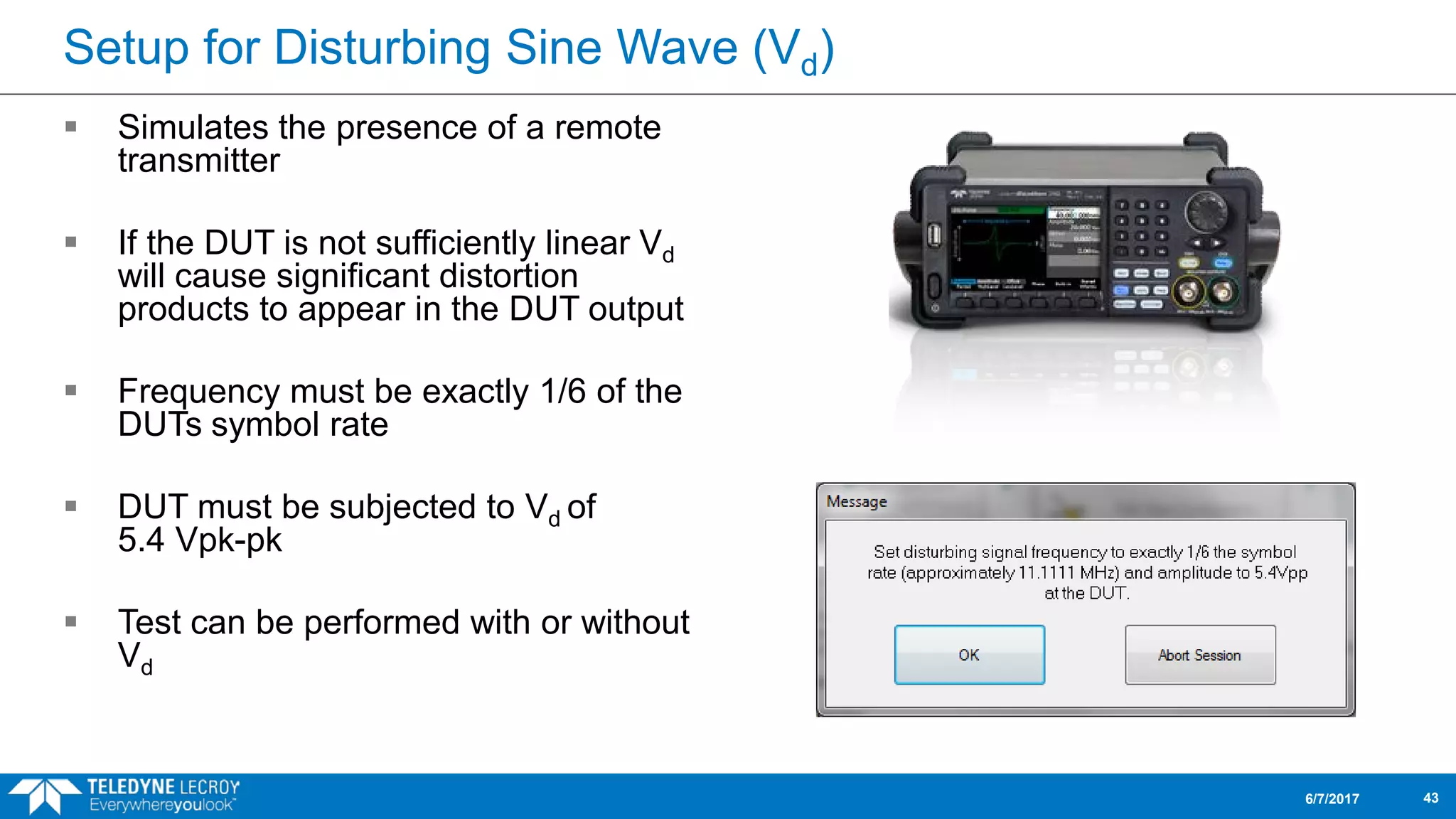

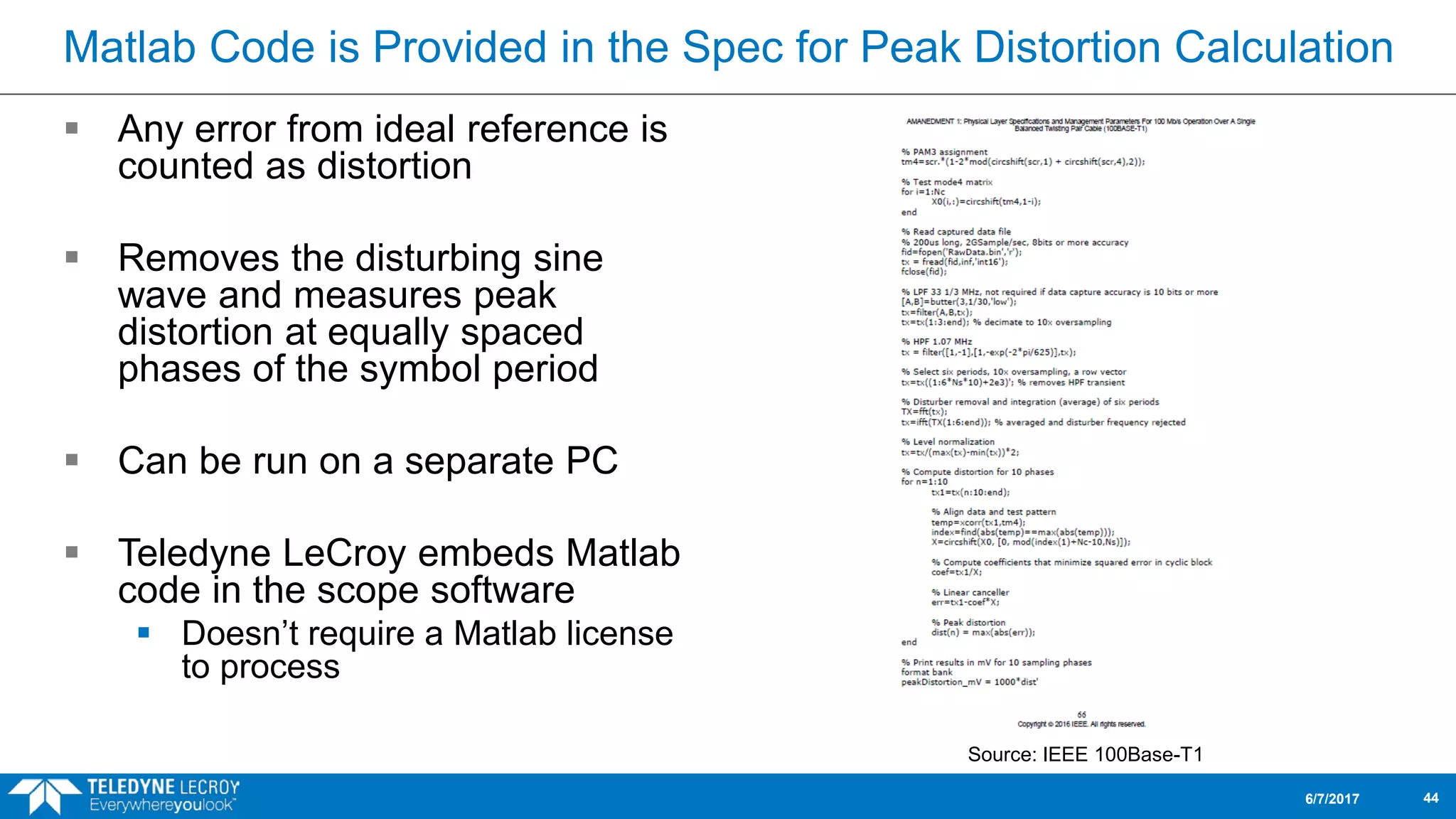

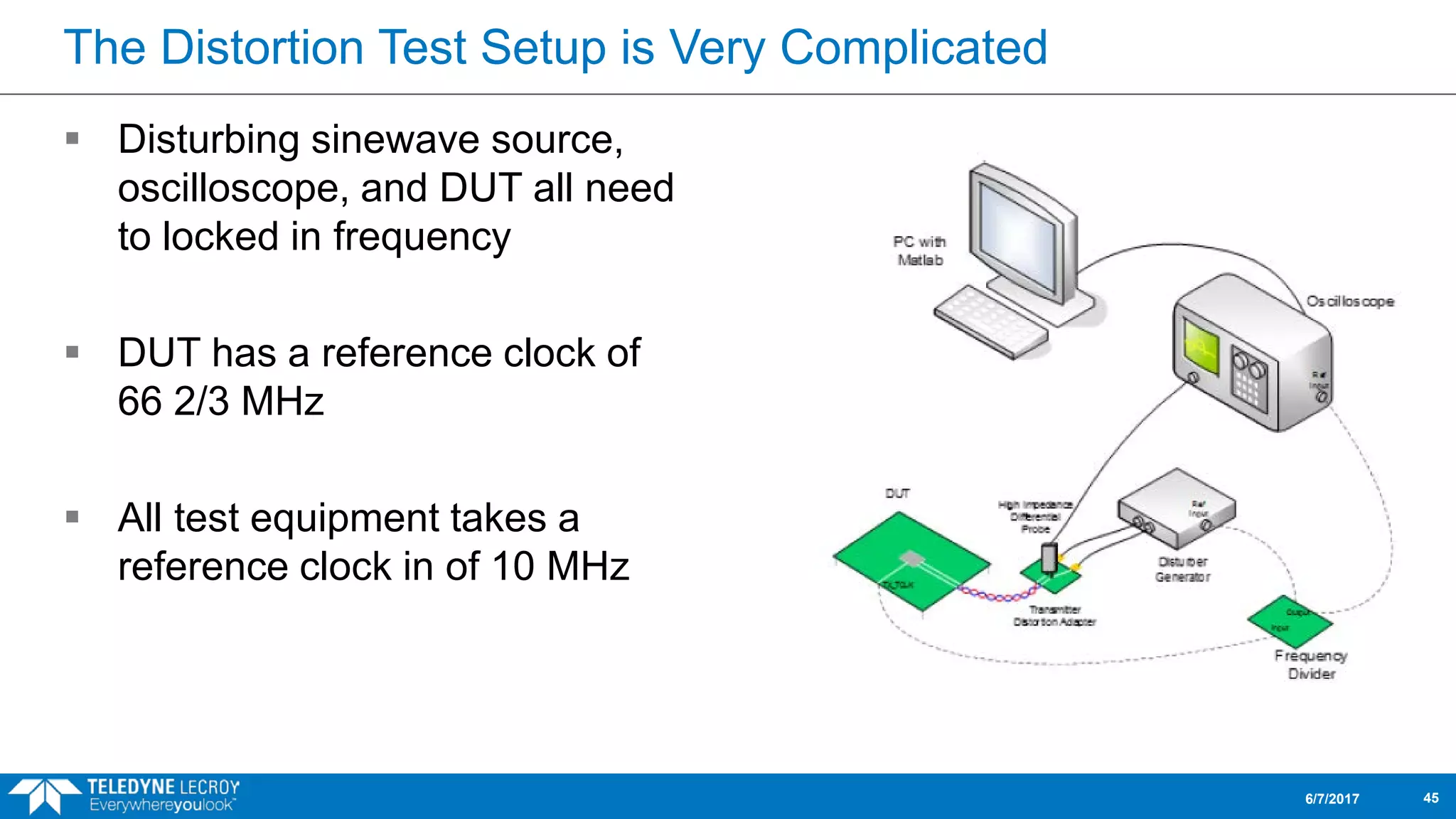

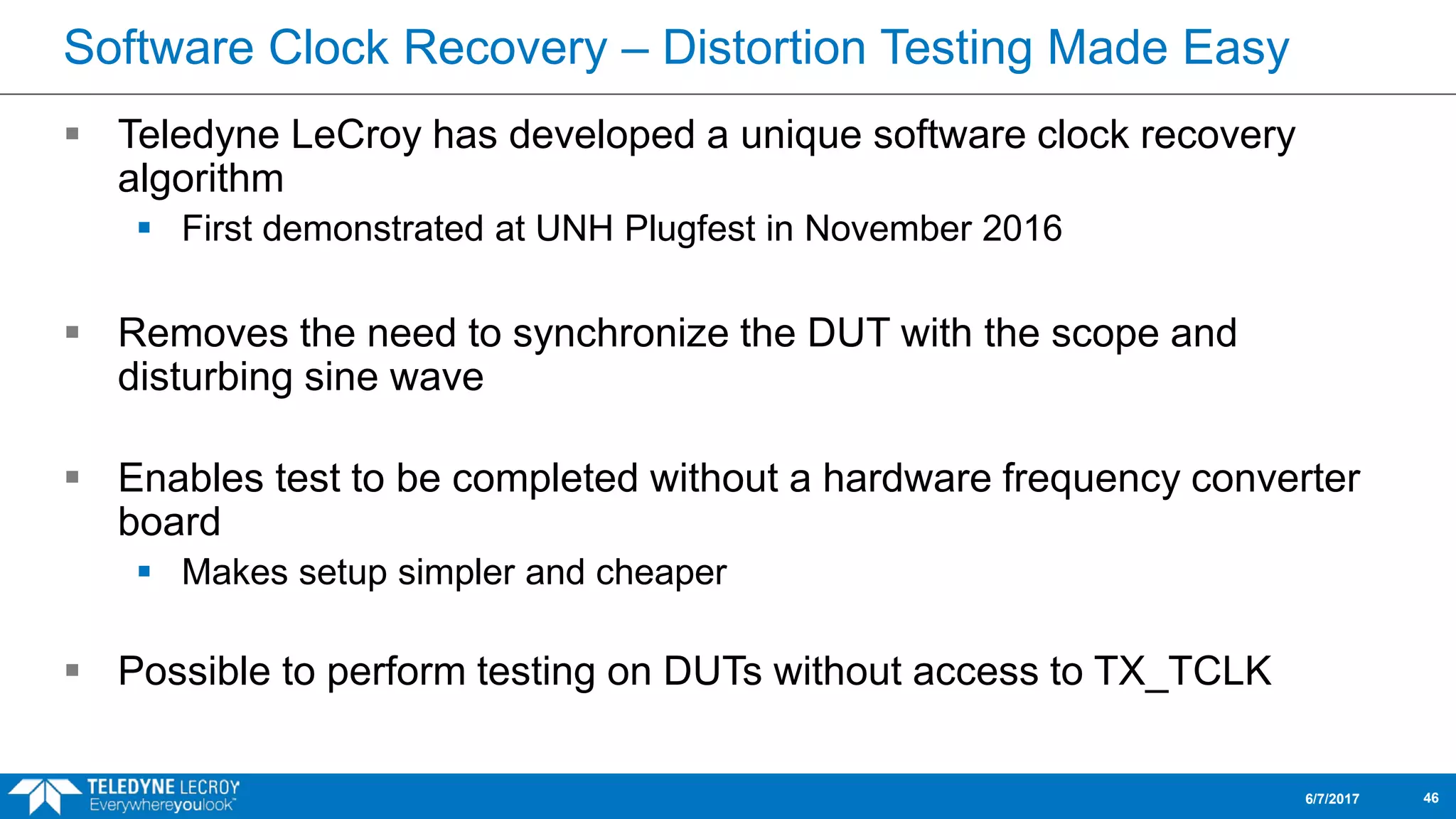

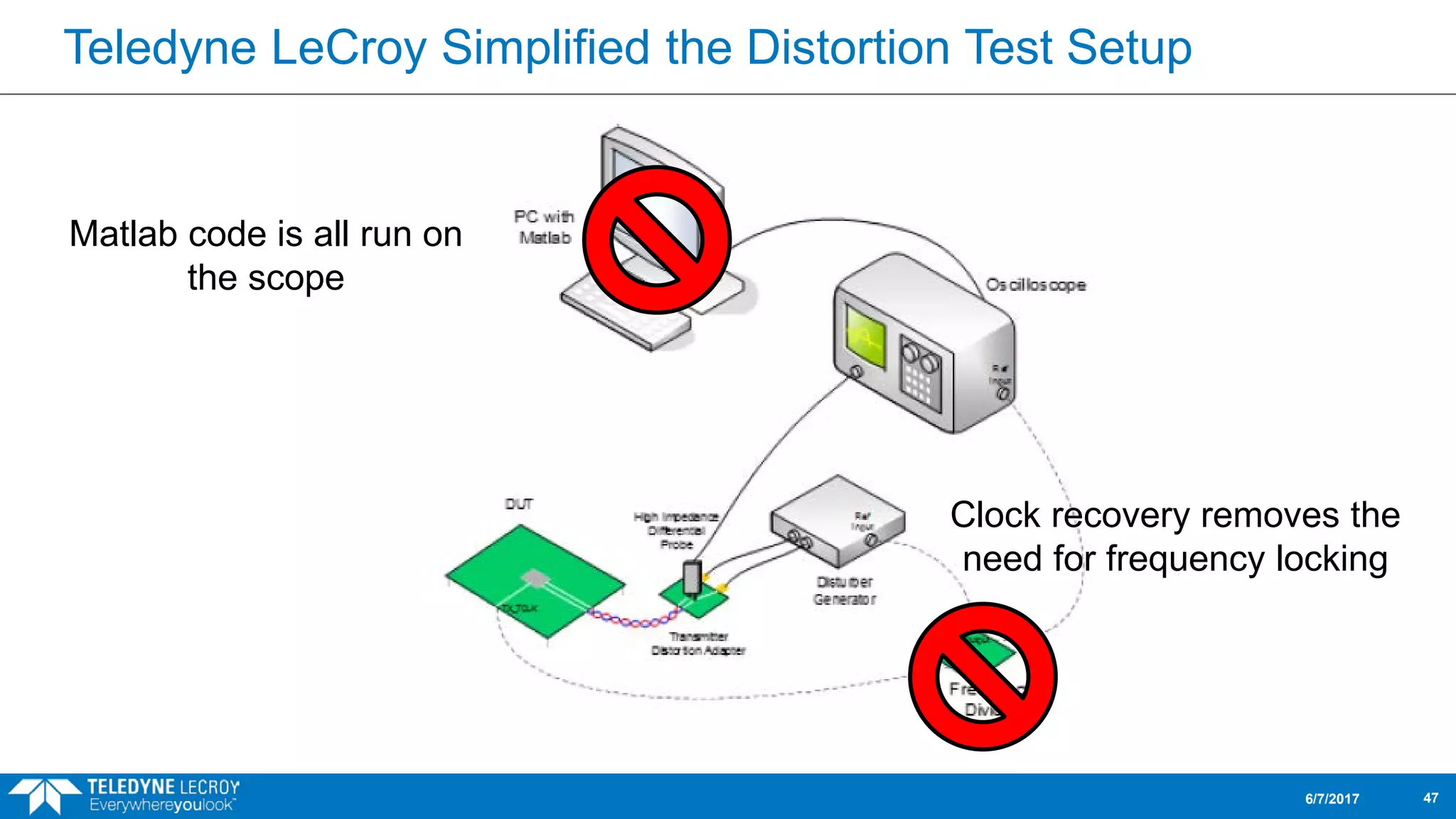

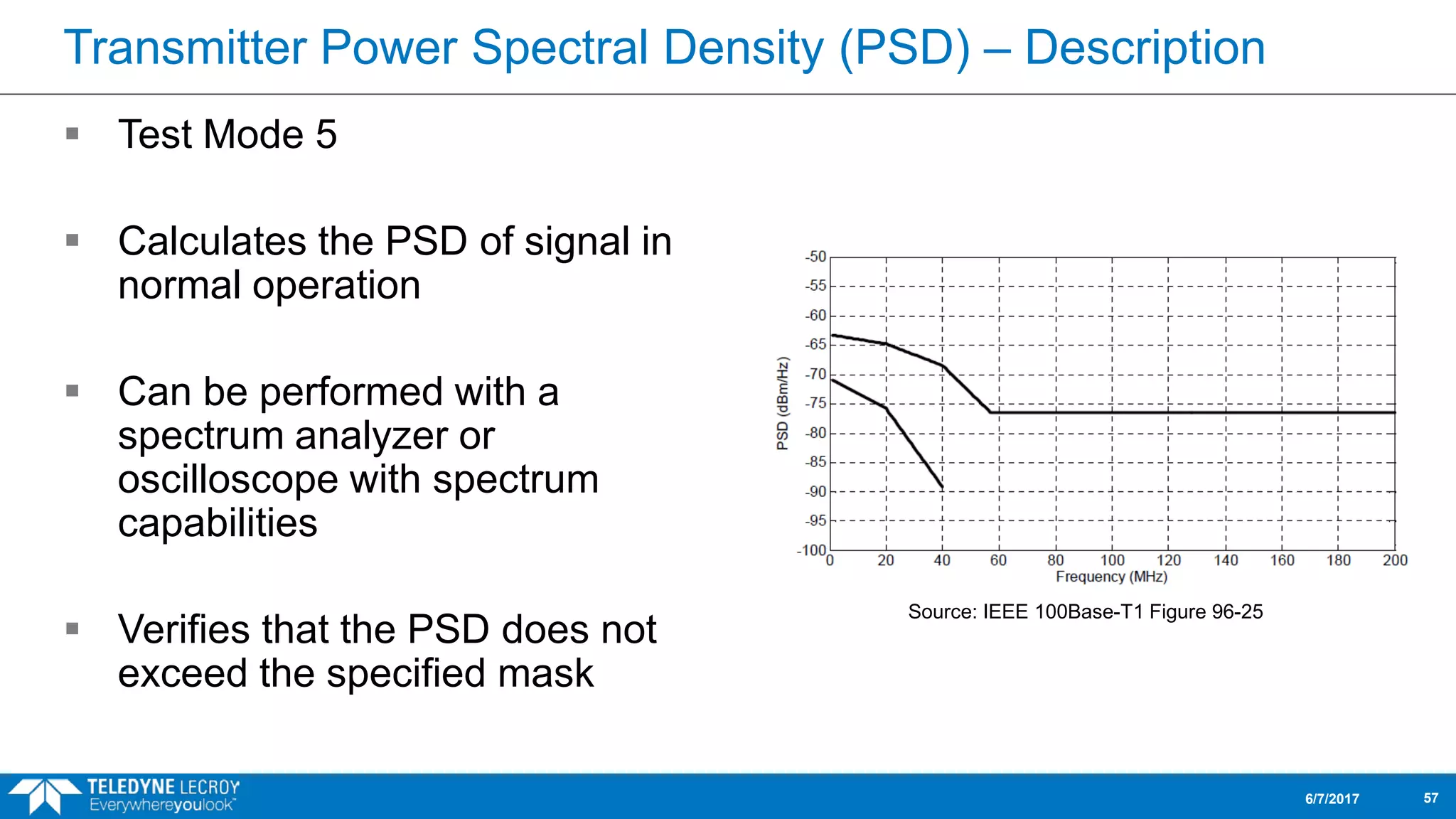

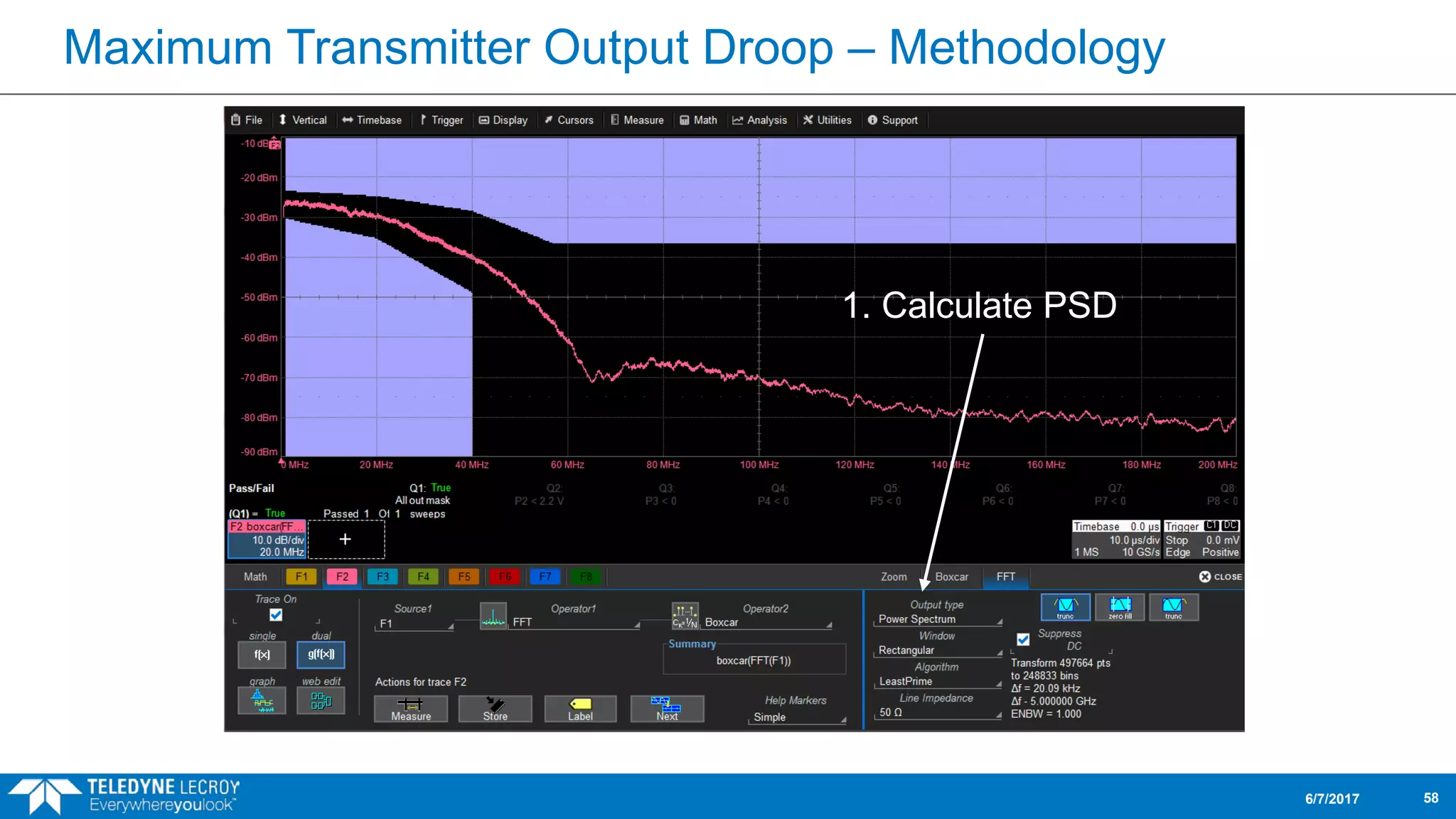

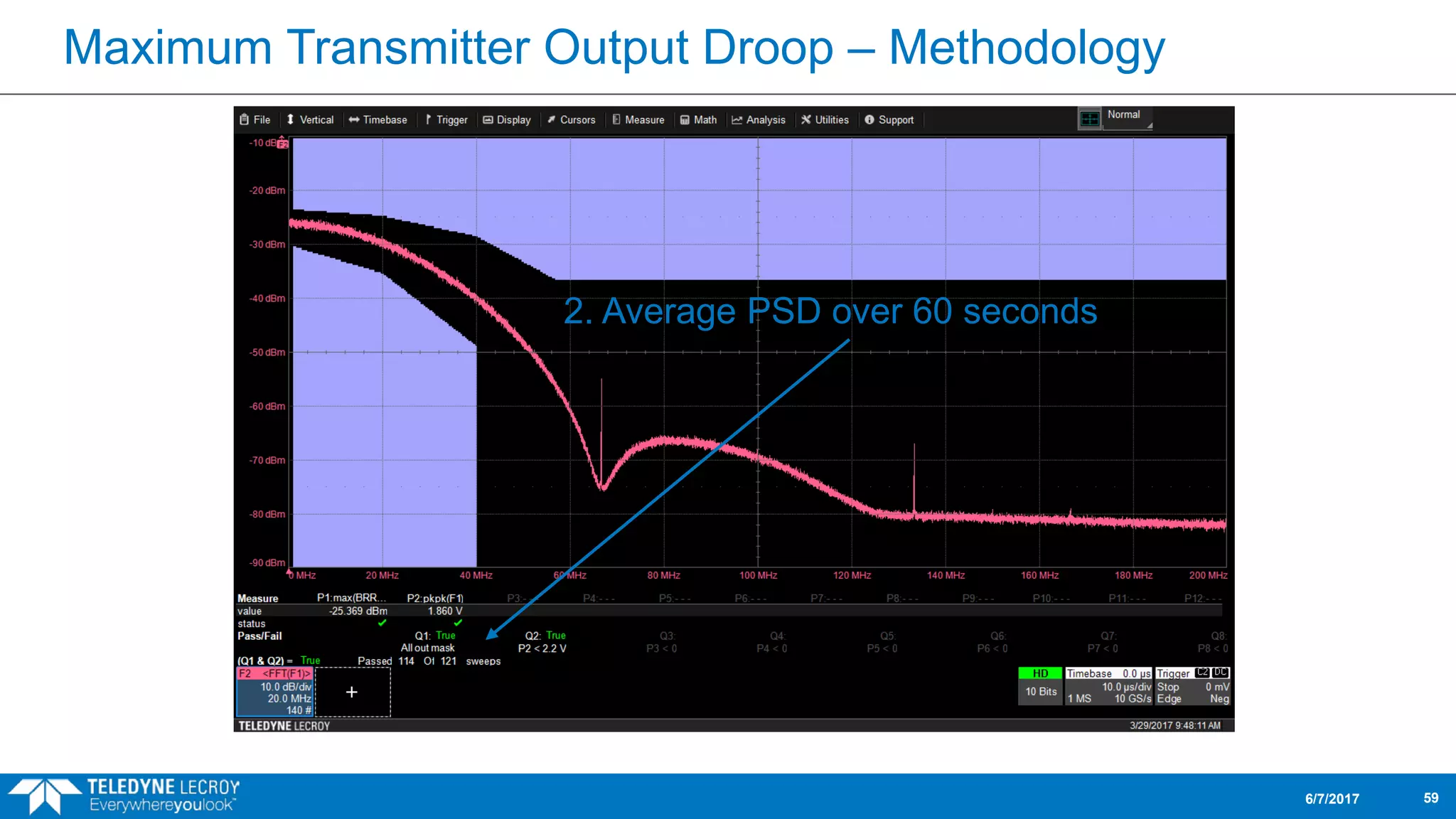

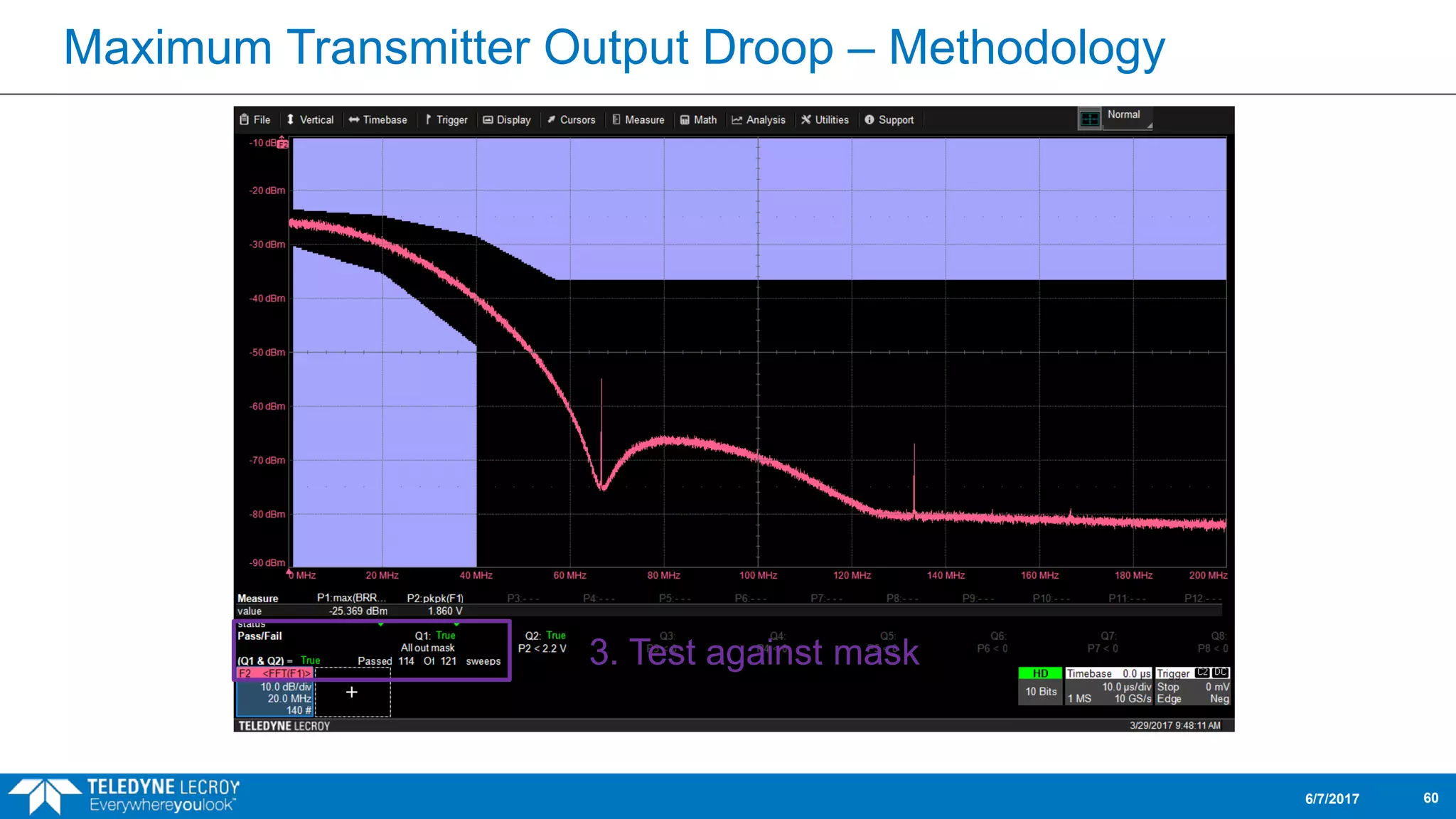

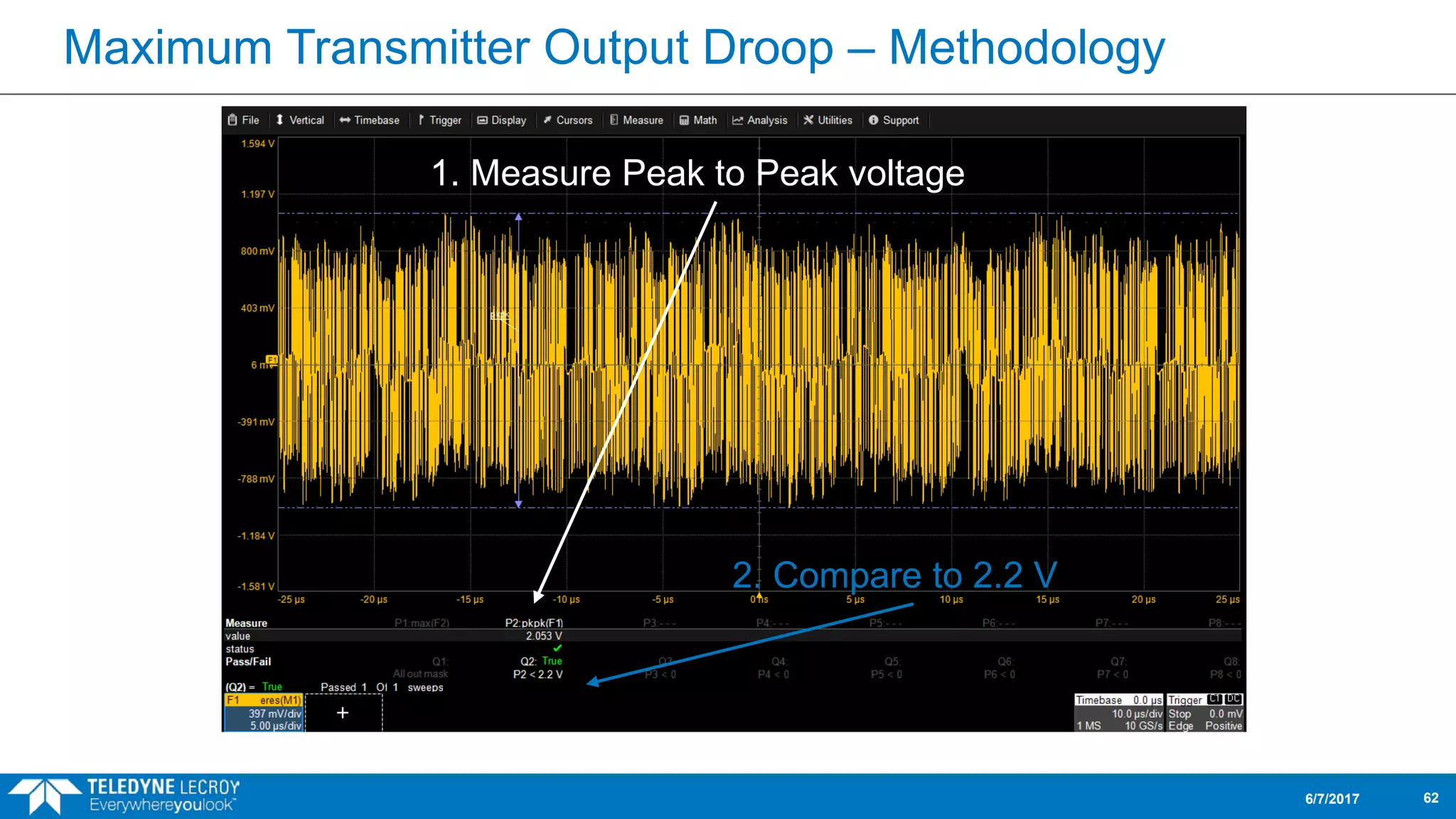

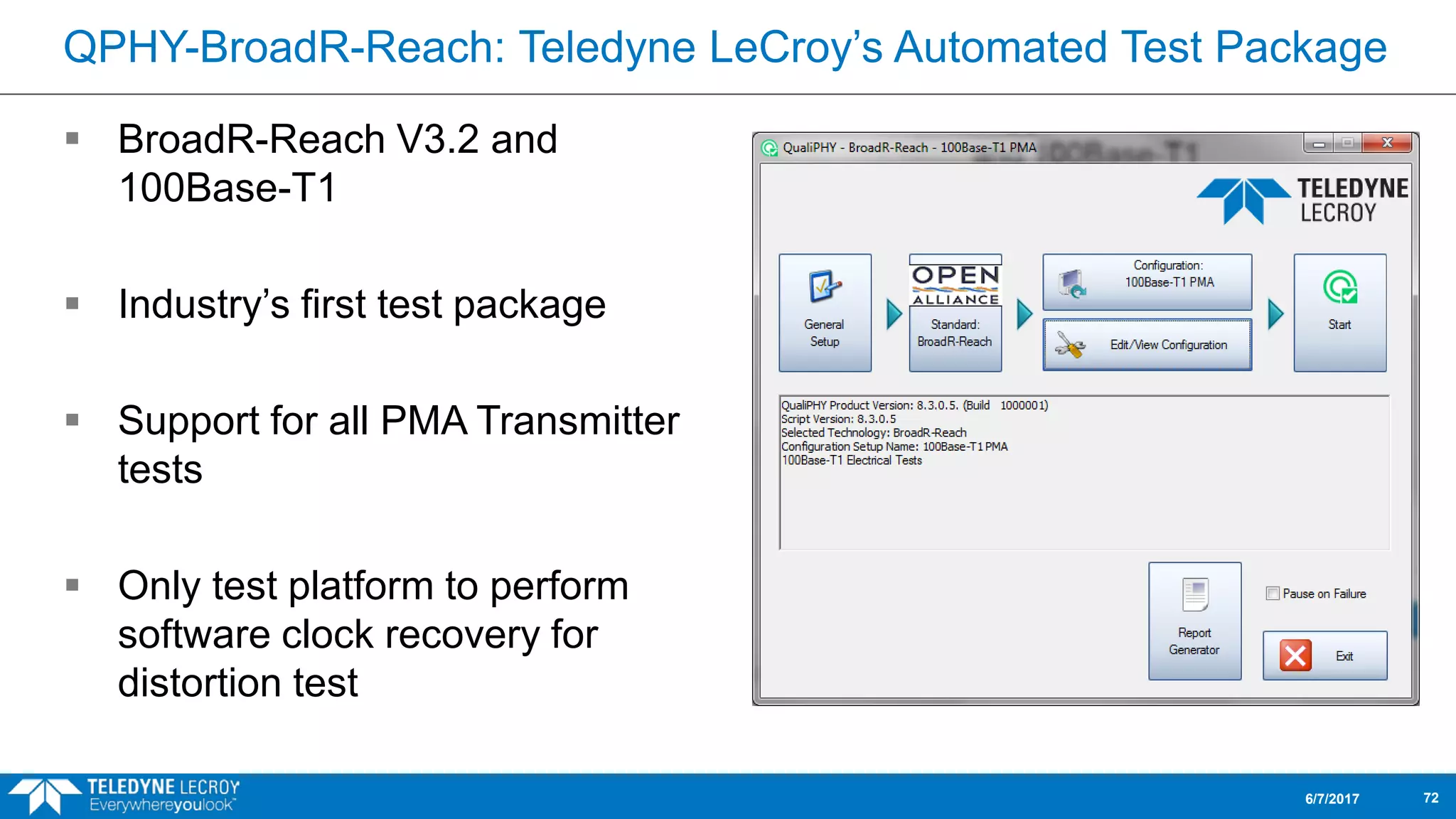

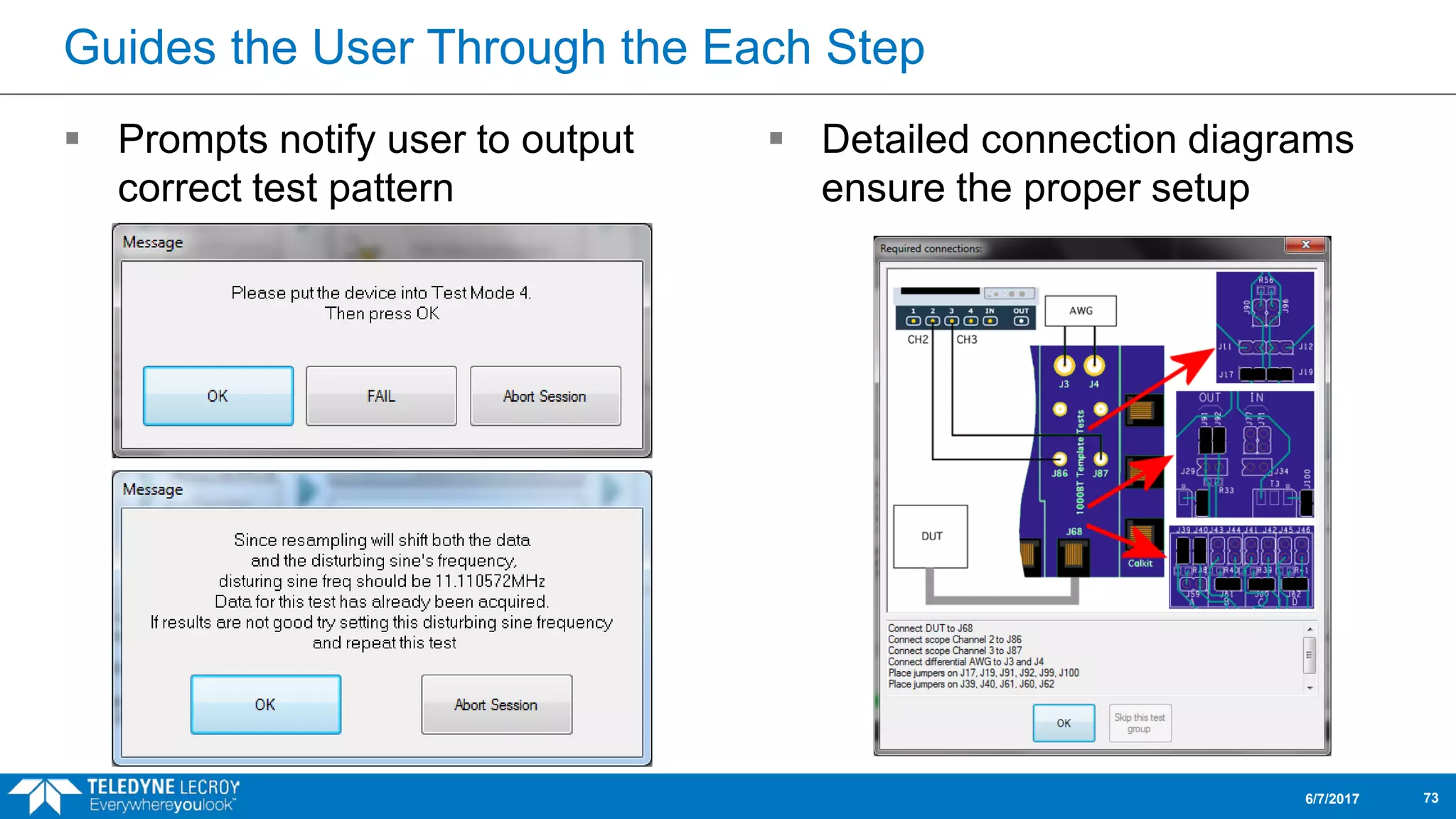

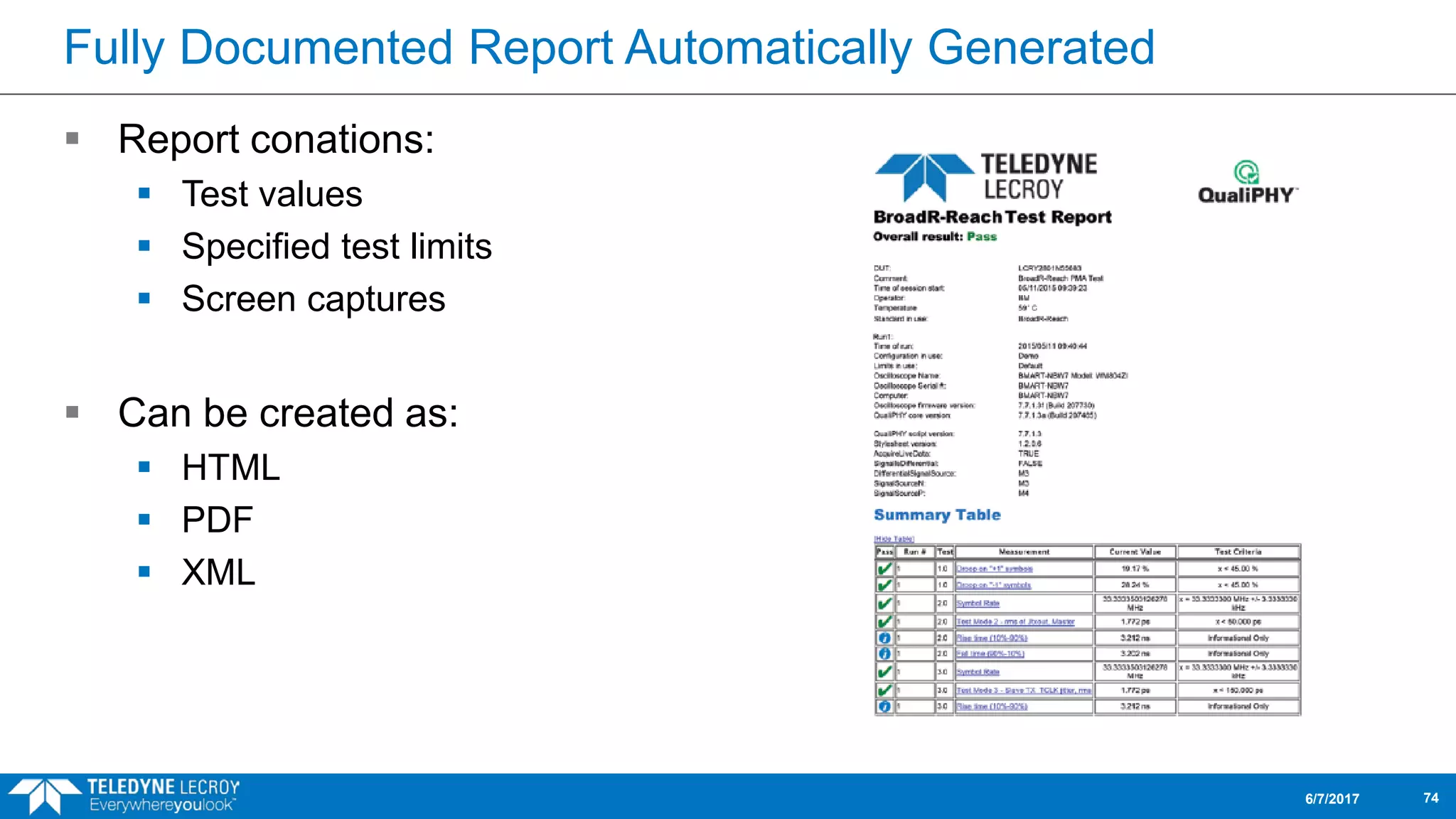

This document outlines the upcoming automotive Ethernet webinars and seminars, focusing on physical layer compliance testing for automotive Ethernet standards such as 100BASE-T1. It details compliance testing categories, the importance of PHY compliance, the defined test modes, methodologies for carrying out tests, and the required test equipment. Emphasis is placed on the functionality and interoperability of automotive networks, aiming to ensure that products meet the necessary specifications before deployment.