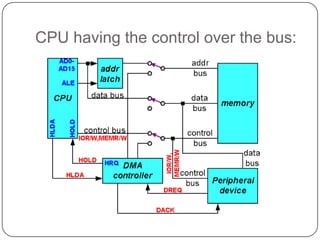

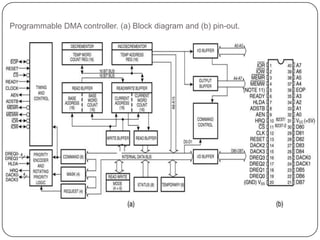

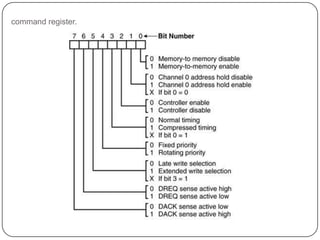

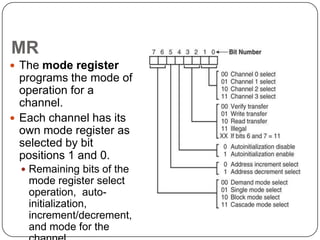

The 8237 DMA controller allows data transfer between I/O devices and memory without CPU intervention. It uses HOLD and HLDA signals to request and acknowledge DMA actions from the CPU. The 8237 contains registers like CAR, CWCR, CR, and SR to program DMA channel operations, addresses, counts, and status. It can perform DMA transfers at up to 1.6 MB/s across 4 channels. Modern systems integrate DMA controllers within chipsets rather than using discrete 8237 components.