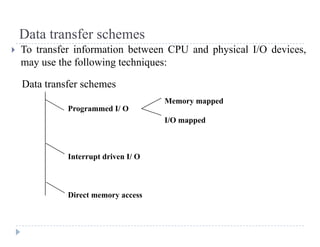

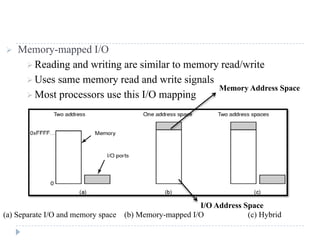

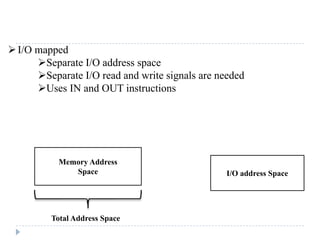

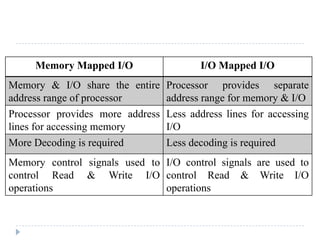

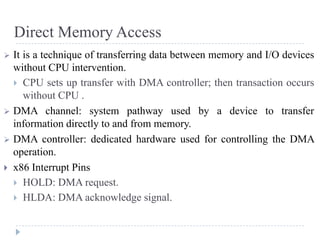

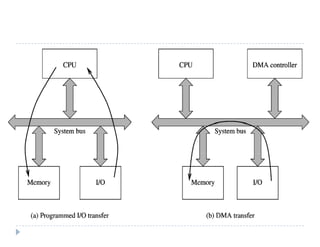

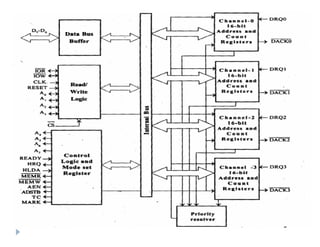

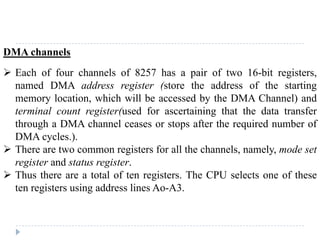

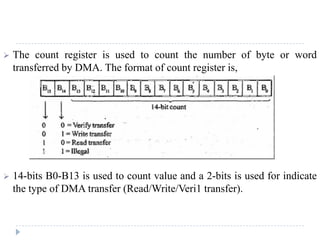

The document discusses various data transfer schemes between the CPU and I/O devices, focusing on programmed I/O, interrupt-driven I/O, and direct memory access (DMA). It explains the advantages and disadvantages of each technique, along with details on the DMA controller 8257 and programmable interval timer 8253, highlighting their features, operational modes, and functionalities. Additionally, it covers the programmable interrupt controller 8259, outlining its structure, register functionalities, and the management of interrupts in a system.