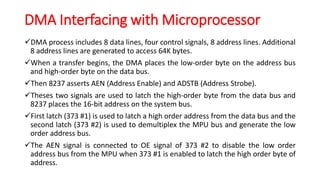

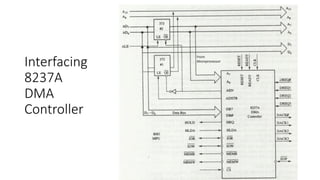

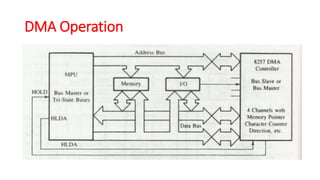

This document discusses the operation and features of the 8237A DMA controller. It explains that DMA allows high-speed data transfer between memory and peripherals by bypassing the CPU. The 8237A has 4 independent channels that can each transfer 64KB of data. It interfaces with the CPU and peripherals using control signals like HOLD, HLDA, DREQ, and DACK. The 8237A has internal registers to store the starting address and transfer count for each channel. It generates 16-bit addresses using the lower address bits from its ports and the higher bits latched from the data bus.

![DMA Operation [Cntd.]

• Direct Memory Access (DMA) is an I/O technique commonly

used for high-speed data transfer; for example , data transfer

between memory and a floppy disk.

• In DMA, MPU releases the control of the buses to a device

called a DMA controller. The controller manages data

transfer between memory and a peripheral under its control,

thus bypassing the MPU.

• Two new signals HOLD and HLDA (Hold acknowledge) are

needed to complete DMA task.](https://image.slidesharecdn.com/directmemoryaccess-220806183735-efb52a0f/85/Direct-Memory-Access-pdf-3-320.jpg)