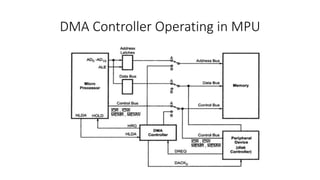

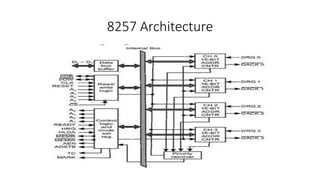

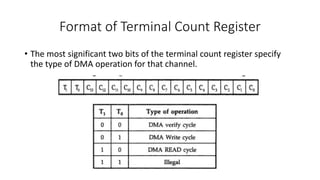

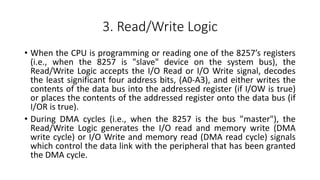

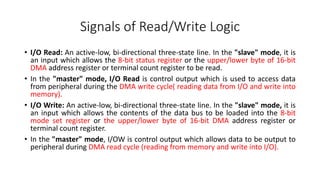

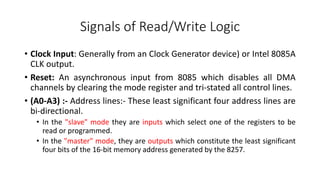

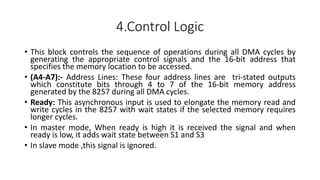

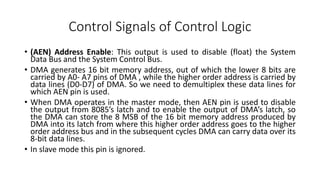

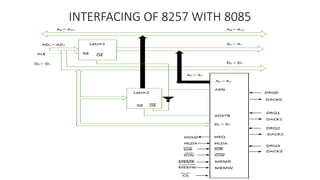

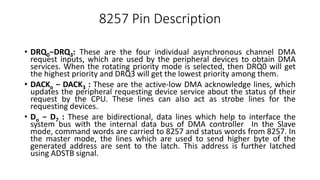

The DMA controller (8257) allows data transfer between I/O devices and memory without CPU involvement. It has 4 independent channels that can be programmed to transfer data via DMA read, write, or verify operations. The 8257 interfaces with the 8085 microprocessor by controlling address/data buses and generating control signals during DMA cycles when it acts as the bus master.