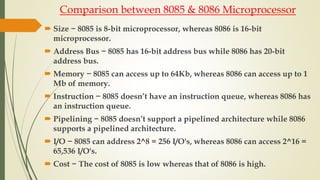

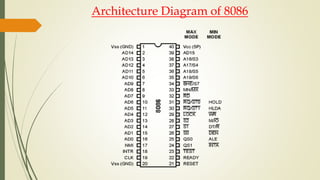

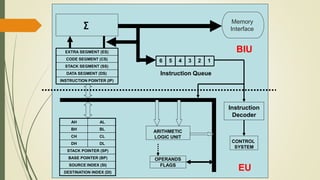

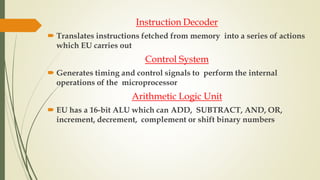

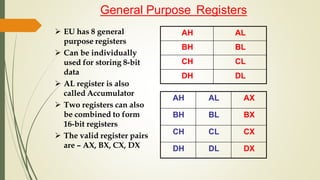

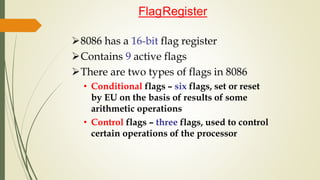

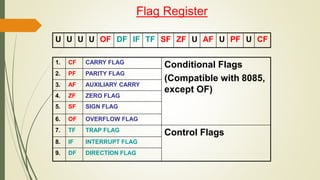

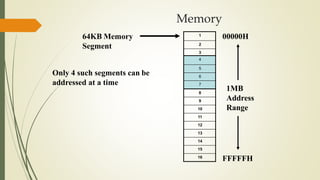

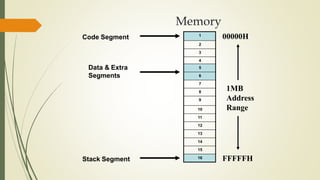

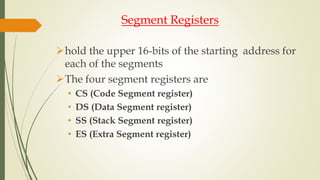

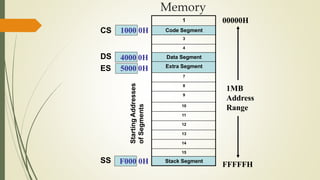

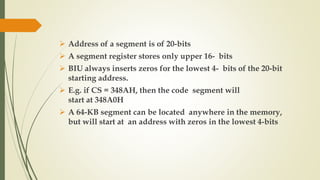

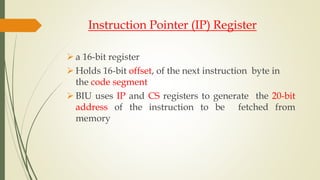

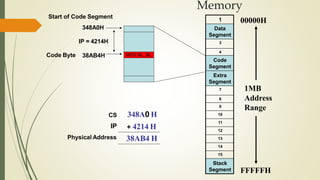

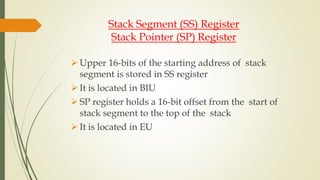

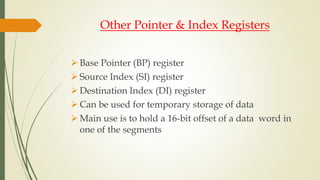

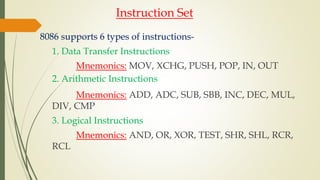

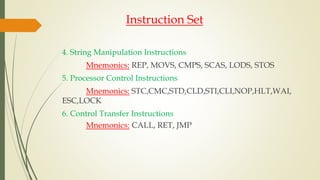

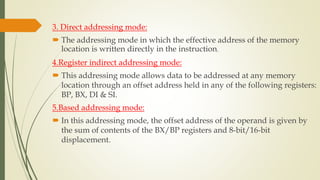

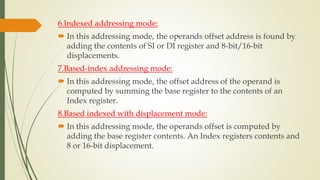

The document discusses the features and architecture of the Intel 8086 microprocessor, including its 16-bit architecture, 20-bit address bus, instruction queue, segmentation of memory into four 64KB segments, registers, flag register, arithmetic logic unit, and various addressing modes. It also provides a comparison of the 8086 to the 8085 microprocessor and describes some applications of the 8086.