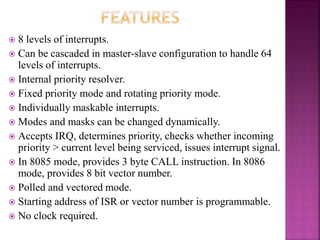

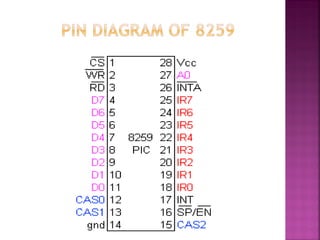

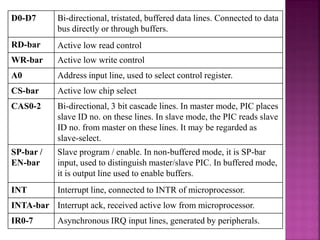

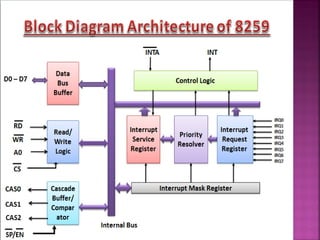

The document describes the functionality and features of a Programmable Interrupt Controller (PIC), emphasizing its role in managing interrupts from peripheral devices in a computer system. It outlines various configurations, including master-slave setups for increasing interrupt levels, the handling of priorities, and the specific registers like initialization command and operation command registers that support its operation. Additionally, it covers the structure of data interfaces, including input/output registers, control mechanisms, and how interrupts are processed within the system.