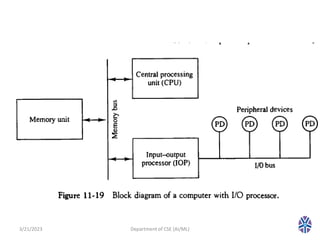

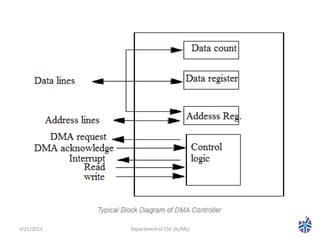

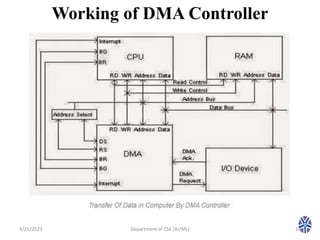

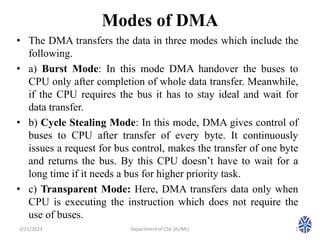

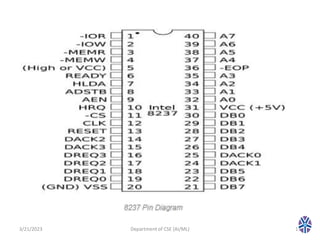

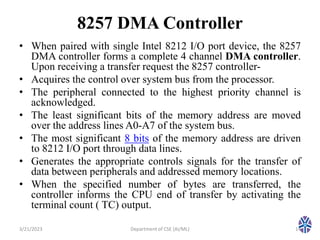

This document summarizes the topics covered in Session 28 of the CS304PC course on Computer Organization and Architecture. It discusses direct memory access (DMA), including how DMA controllers work, their components, and modes of DMA transfer. Examples of DMA controllers like the 8237 and 8257 are described. Advantages of DMA include bypassing CPU involvement to speed up memory operations, while disadvantages include potential cache coherence problems and increased system cost. The next session will cover memory organization topics.