10 multiplexers-de mux

•

0 likes•357 views

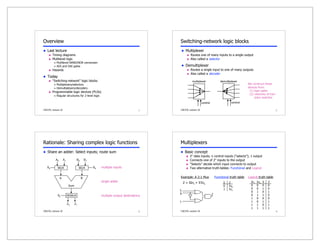

1. The lecture discusses multiplexers, demultiplexers, and programmable logic devices. Multiplexers route one of several inputs to a single output, while demultiplexers route a single input to one of several outputs. 2. Multiplexers and demultiplexers can implement any Boolean function and be used as general purpose logic blocks. They can be cascaded to form larger multiplexers and demultiplexers. 3. Programmable logic arrays and programmable array logic are arrays of uncommitted AND and OR gates that can implement any two-level logic function by programming the wire connections. Product terms can be shared across multiple outputs.

Report

Share

Report

Share

Download to read offline

Recommended

Digital electronics multiplexers demultiplexers

Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer does the reverse, taking a single input and distributing it to multiple outputs based on select lines. Multiplexers and demultiplexers can be combined in trees to increase the number of inputs and outputs. They are used to implement logic functions where a select line acts as the value of a variable in a Boolean expression.

Multiplexers & Demultiplexers

Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer has a single input, select lines to choose an output, and multiple outputs. Bigger multiplexers and demultiplexers can be built by cascading smaller ones. Multiplexers can implement logic functions by using the select lines as variables and routing the input lines to the output.

Multiplexers

A multiplexer is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. It has multiple data inputs, a single output, and select lines that determine which input is directed to the output. A demultiplexer performs the opposite function, taking a single input and distributing it to one of multiple outputs based on the select lines. Multiplexers and demultiplexers come in various configurations depending on the number of inputs and outputs, such as 2:1, 4:1, 16:1 or 32:1. They are basic building blocks used in digital systems and communication networks to efficiently route signals.

Encoder, decoder, multiplexers and demultiplexers

This document discusses multiplexers, demultiplexers, encoders, and decoders. It provides examples and exercises for designing logic circuits using these components. Specifically, it describes how to use multiplexers and decoders to realize logic functions by mapping the minterms of the function to the inputs/outputs of the components. Exercises are included for designing an 8-to-1 multiplexer from 4-to-1 and 2-to-1 multiplexers, and designing a 4-to-16 decoder from 2-to-4 decoders. Priority encoders and decoders with enables are also covered.

multiplexers and demultiplexers

This document discusses multiplexers and demultiplexers. It defines them as devices that allow digital information from several sources to be routed onto a single line (multiplexers) or distributed to multiple output lines (demultiplexers). The key properties of multiplexers and demultiplexers are described, including the relationship between the number of inputs, outputs, and selection lines. Examples of implementing multiplexers and demultiplexers using logic gates are provided.

Multiplexer demul

1) A multiplexer is a combinational circuit with m inputs, n control inputs, and 1 output that can select one of the m inputs to pass to the output based on the values of the n control inputs.

2) A 4-to-1 multiplexer has 4 inputs, 2 control inputs, and 1 output. The output will be one of the 4 inputs depending on the binary values of the 2 control inputs.

3) A demultiplexer is the opposite of a multiplexer, taking a single input and distributing it to one of multiple outputs based on the control inputs. It can also be used as a decoder to output a binary word based on the control input code.

multiplexer 4 input

A multiplexer is a digital circuit that has multiple inputs and a single output. It selects one of the multiple input lines and outputs it depending on the value of the select lines. A 4-to-1 multiplexer has 4 data inputs, 2 select lines, and 1 output. The value of the select lines determines which of the 4 inputs is output. Multiplexers are used when multiple data sources need to be transmitted over a single line or routed, such as in telecommunications, computers, and audio/video systems to select different input channels.

Multiplexers and demultiplexers 2

A multiplexer and demultiplexer allow multiple signals to share a single transmission line. A 2/1 multiplexer is described with a block diagram, truth table, and K-map implementation showing it selects one of two inputs based on a select line. A 4/1 multiplexer circuit is also shown. Multiplexers are used in data communications, radio channels, computer routing, and function generation by selecting an output from multiple inputs. An 8/1 multiplexer generates a function from a truth table. A 1 to 2 demultiplexer circuit separates a single input into two outputs based on a select line.

Recommended

Digital electronics multiplexers demultiplexers

Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer does the reverse, taking a single input and distributing it to multiple outputs based on select lines. Multiplexers and demultiplexers can be combined in trees to increase the number of inputs and outputs. They are used to implement logic functions where a select line acts as the value of a variable in a Boolean expression.

Multiplexers & Demultiplexers

Multiplexers and demultiplexers allow digital information from multiple sources to be routed through a single line. A multiplexer has multiple data inputs, select lines to choose an input, and a single output. A demultiplexer has a single input, select lines to choose an output, and multiple outputs. Bigger multiplexers and demultiplexers can be built by cascading smaller ones. Multiplexers can implement logic functions by using the select lines as variables and routing the input lines to the output.

Multiplexers

A multiplexer is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. It has multiple data inputs, a single output, and select lines that determine which input is directed to the output. A demultiplexer performs the opposite function, taking a single input and distributing it to one of multiple outputs based on the select lines. Multiplexers and demultiplexers come in various configurations depending on the number of inputs and outputs, such as 2:1, 4:1, 16:1 or 32:1. They are basic building blocks used in digital systems and communication networks to efficiently route signals.

Encoder, decoder, multiplexers and demultiplexers

This document discusses multiplexers, demultiplexers, encoders, and decoders. It provides examples and exercises for designing logic circuits using these components. Specifically, it describes how to use multiplexers and decoders to realize logic functions by mapping the minterms of the function to the inputs/outputs of the components. Exercises are included for designing an 8-to-1 multiplexer from 4-to-1 and 2-to-1 multiplexers, and designing a 4-to-16 decoder from 2-to-4 decoders. Priority encoders and decoders with enables are also covered.

multiplexers and demultiplexers

This document discusses multiplexers and demultiplexers. It defines them as devices that allow digital information from several sources to be routed onto a single line (multiplexers) or distributed to multiple output lines (demultiplexers). The key properties of multiplexers and demultiplexers are described, including the relationship between the number of inputs, outputs, and selection lines. Examples of implementing multiplexers and demultiplexers using logic gates are provided.

Multiplexer demul

1) A multiplexer is a combinational circuit with m inputs, n control inputs, and 1 output that can select one of the m inputs to pass to the output based on the values of the n control inputs.

2) A 4-to-1 multiplexer has 4 inputs, 2 control inputs, and 1 output. The output will be one of the 4 inputs depending on the binary values of the 2 control inputs.

3) A demultiplexer is the opposite of a multiplexer, taking a single input and distributing it to one of multiple outputs based on the control inputs. It can also be used as a decoder to output a binary word based on the control input code.

multiplexer 4 input

A multiplexer is a digital circuit that has multiple inputs and a single output. It selects one of the multiple input lines and outputs it depending on the value of the select lines. A 4-to-1 multiplexer has 4 data inputs, 2 select lines, and 1 output. The value of the select lines determines which of the 4 inputs is output. Multiplexers are used when multiple data sources need to be transmitted over a single line or routed, such as in telecommunications, computers, and audio/video systems to select different input channels.

Multiplexers and demultiplexers 2

A multiplexer and demultiplexer allow multiple signals to share a single transmission line. A 2/1 multiplexer is described with a block diagram, truth table, and K-map implementation showing it selects one of two inputs based on a select line. A 4/1 multiplexer circuit is also shown. Multiplexers are used in data communications, radio channels, computer routing, and function generation by selecting an output from multiple inputs. An 8/1 multiplexer generates a function from a truth table. A 1 to 2 demultiplexer circuit separates a single input into two outputs based on a select line.

Multiplexer & de multiplexer

This document discusses multiplexers and de-multiplexers. It defines a multiplexer as a circuit that accepts multiple input signals but provides a single output signal, selecting one input using control signals. A de-multiplexer is the opposite, accepting one input and providing multiple outputs. Examples of 4-to-1 multiplexers and 1-to-4 de-multiplexers are described. Applications include communication systems, computer memory, and transmitting satellite data. Multiplexers and de-multiplexers are commonly used together and are important combinational logic circuits.

Multiplexers

A multiplexer (MUX) is a digital switch that selects one of several input lines and outputs the selected input to a single output line. It uses select lines to determine which input is connected to the output. A typical application is connecting multiple audio/video sources like an MP3 player, laptop, satellite receiver, or cable TV to a single output destination like a home theater system. The document demonstrates a 4-to-1 MUX that uses two select lines A and B to choose one of four data inputs D0, D1, D2, or D3 and output it to line Y.

1 Multiplexer

This document discusses multiplexers and demultiplexers. It begins by defining a multiplexer as a digital switch that has multiple inputs and a single output, with select lines determining which input is connected to the output. It then defines a demultiplexer as having a single input and multiple outputs, with select lines determining the output. The document provides examples of 4-to-1 and 1-to-4 multiplexers and demultiplexers, and discusses their applications. It also describes how multiplexed displays can be used to display a message more efficiently than illuminating all segments at once.

Demultiplexer presentation

This document discusses demultiplexers and is authored by group members Md. Shamsuzzaman, Shaikat Saha, Shibli Sadik, and Atif Rizwan. It defines a demultiplexer as a digital switch that takes a single input and routes it to multiple outputs based on select lines. The document describes 1-to-2, 1-to-4, and 1-to-8 line demultiplexers and includes their truth table. Diagrams of demultiplexer functions are also provided.

multiplexer and d-multiplexer

The truth table is not complete because it is missing the encoding for when no inputs are active. A complete truth table would include a row for all zero inputs to specify the output in that case.

The output equations are:

A0 = D7

A1 = D6 + D5 + D4 + D3

A2 = D2 + D1 + D0

This encodes the highest priority input on the lowest two bits, with the next two highest priorities on the middle bit, and any active input setting the highest bit.

Multiplexer and DeMultiplexer

A multiplexer has multiple inputs and a single output line, using select lines to determine which input is connected to the output. It is used to increase the amount of data that can be sent over a network. A demultiplexer is the reverse, with one input and multiple output lines, using select lines to send a signal to one of the output lines. Both are used in communication systems, computer memory, and other applications to efficiently transmit data or connect parts of a system.

multiplexer

A multiplexer (or mux) is a device that selects one of several analog or digital input signals and forwards the selected input into a single line.

COMPUTER ORGANIZATION -Multiplexer,Demultiplexer, Encoder

This document discusses multiplexers, demultiplexers, and digital encoders. It provides the following information:

- Multiplexers are digital circuits that select one of several input signals and output the selected signal. Demultiplexers perform the reverse operation.

- Multiplexers and demultiplexers come in variations depending on the number of input/output channels such as 2:1, 4:1, 16:1, etc. Their operation is illustrated using logic gates.

- Digital encoders convert binary input lines into an equivalent binary code output. Priority encoders were developed to solve issues with standard encoders generating incorrect outputs when multiple inputs are high.

Combinational circuit

An integrated circuit is a small chip of silicon that contains multiple transistors. Decoders and encoders are types of combinational logic circuits. A decoder accepts an input and uses it to activate one of its outputs, while an encoder performs the inverse by activating its outputs based on active inputs. Decoders and multiplexers are similar in that they select an output from multiple inputs, but decoders have multiple outputs while multiplexers have a single output. Multiplexers can be cascaded to increase the number of inputs selected from.

CSL 202, Multiplexer and Demultiplexer

The attached narrated power point presentation explains the working of multiplexers and demultiplexers and familiarises oneself with popular multiplexer, demultiplexer and decoder ICs. The material will be useful for KTU second year B Tech students in Computer Science and Engineering who prepare for the subject CSL 202, Digital Laboratory.

DESIGN OF COMBINATIONAL LOGIC

Here are the steps:

Binary Number 1 0 1 0

Gray Code 1 1 1 1

The Gray code for 1010 binary is 1111.

Saur lecture 16

This document summarizes a lecture on multiplexers, decoders, and encoders. It begins with definitions and examples of basic 2-to-1 multiplexers and 2-to-4 decoders. It then discusses hierarchical implementations using smaller multiplexers and decoders as building blocks. Finally, it describes techniques for designing logic circuits using multiplexers and decoders to realize Boolean functions.

Ceng232 Decoder Multiplexer Adder

The document discusses decoders, multiplexers, and programmable logic. It begins by explaining what decoders and multiplexers are, providing examples of 2-to-4 and 3-to-8 decoders. It then discusses how decoders and multiplexers can be used to implement arbitrary logic functions. The document also covers variations of decoders, building decoders from smaller components, and using multiplexers to efficiently implement functions in a sum of minterms form.

Multiplexer and demultiplexer applications.ppsx 3

This document discusses multiplexers and demultiplexers. It defines a multiplexer as a device with multiple inputs and a single output that uses select lines to determine which input is connected to the output. Demultiplexers are defined as having a single input and multiple outputs, with the select lines determining which output receives the signal. The document discusses types of multiplexers and demultiplexers and their applications in communication systems, computer memory, telephone networks, and transmitting data from satellites and computers.

عرض تقديمي1

A demultiplexer (DEMUX) is a digital switch that takes a single input signal and routes it to one of multiple outputs based on select lines. It has one input and 2^N outputs where N is the number of select lines. Common types include 1-to-2, 1-to-4, and 1-to-8 DEMUX. The document discusses DEMUX applications, provides block diagrams and truth tables to explain how a single input is routed to the correct output based on the state of the select lines.

encoder and decoder in digital electronics

In digital electronics, a decoder can take the form of a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different e.g. n-to-2n , binary-coded decimal decoders. Decoding is necessary in applications such as data multiplexing, 7 segment display and memory address decoding.

An encoder is a device, circuit, transducer, software program, algorithm or person that converts information from one format or code to another. The purpose of encoder is standardization, speed, secrecy, security, or saving space by shrinking size. Encoders are combinational logic circuits and they are exactly opposite of decoders. They accept one or more inputs and generate a multibit output code.

3. multiplexer

This document discusses multiplexers, which take multiple input signals and steer one of the inputs to the output based on control signals. It provides examples of 4-to-1, 16-to-1, and 8-to-1 multiplexers and describes how their outputs are determined by the states of the control signals. It also describes the IC 74150 16-to-1 multiplexer chip and the nibble multiplexer, which selects between two 4-bit nibbles as its output.

Mux decod pld2_vs2

This document discusses complex integrated circuits used in logic design including multiplexers, decoders, and programmable logic devices. It provides details on 4 categories of integrated circuits based on the number of gates - SSI, MSI, LSI, and VLSI. Multiplexers are described as circuits that select one of several data inputs to connect to the output based on the control inputs. Decoders are the inverse, detecting a particular input and activating the corresponding output. Programmable logic devices can be programmed to provide different logic functions, allowing for changes without rewiring the system.

Decoders

This document discusses decoders, which are circuits that take a binary input and activate one of multiple outputs. It provides examples of 2-to-4 and 3-to-8 decoders and their truth tables. Decoders are constructed using AND gates, with the number of gates equal to the number of outputs. Larger decoders can be built in parallel, balanced, or tree configurations, with balanced decoders requiring the fewest components.

08 decoder

The document describes decoders and encoders. It begins by explaining what a decoder is, providing examples of 2-to-4 and 3-to-8 decoders. It then discusses how decoders can be used to implement general logic and combinational circuits using decoders and OR gates. The document proceeds to describe specific decoder chips like the 74x139 and 74x138 decoders. It also discusses using 3-state buffers with decoders and building decoders from smaller decoders. The document then shifts to discussing encoders, 7-segment decoders, truth tables, and K-maps in the design of decoders and encoders. It concludes by discussing priority encoders and the 74x148 priority encoder chip.

Multiplexing

The document discusses multiplexing techniques for transmitting multiple signals across a single data link. It describes frequency division multiplexing (FDM) which is an analog technique that separates channels by assigning different frequency bands. It also describes time division multiplexing (TDM) which is a digital technique that divides the transmission path into sequential time slots to allocate to different signals in a round-robin fashion. Both multiplexing and demultiplexing processes are discussed.

Pcm pulse codemodulation-2

The document contains 38 figures that describe various digital modulation techniques used in communication systems, including PAM, PCM, ASK, FSK, PSK, QAM. It explains how analog signals are converted to digital signals using techniques like quantization and encoding. It also illustrates key concepts like Nyquist theorem, signal constellations, and the relationships between bit rate, baud rate, and bandwidth for different modulation methods.

More Related Content

What's hot

Multiplexer & de multiplexer

This document discusses multiplexers and de-multiplexers. It defines a multiplexer as a circuit that accepts multiple input signals but provides a single output signal, selecting one input using control signals. A de-multiplexer is the opposite, accepting one input and providing multiple outputs. Examples of 4-to-1 multiplexers and 1-to-4 de-multiplexers are described. Applications include communication systems, computer memory, and transmitting satellite data. Multiplexers and de-multiplexers are commonly used together and are important combinational logic circuits.

Multiplexers

A multiplexer (MUX) is a digital switch that selects one of several input lines and outputs the selected input to a single output line. It uses select lines to determine which input is connected to the output. A typical application is connecting multiple audio/video sources like an MP3 player, laptop, satellite receiver, or cable TV to a single output destination like a home theater system. The document demonstrates a 4-to-1 MUX that uses two select lines A and B to choose one of four data inputs D0, D1, D2, or D3 and output it to line Y.

1 Multiplexer

This document discusses multiplexers and demultiplexers. It begins by defining a multiplexer as a digital switch that has multiple inputs and a single output, with select lines determining which input is connected to the output. It then defines a demultiplexer as having a single input and multiple outputs, with select lines determining the output. The document provides examples of 4-to-1 and 1-to-4 multiplexers and demultiplexers, and discusses their applications. It also describes how multiplexed displays can be used to display a message more efficiently than illuminating all segments at once.

Demultiplexer presentation

This document discusses demultiplexers and is authored by group members Md. Shamsuzzaman, Shaikat Saha, Shibli Sadik, and Atif Rizwan. It defines a demultiplexer as a digital switch that takes a single input and routes it to multiple outputs based on select lines. The document describes 1-to-2, 1-to-4, and 1-to-8 line demultiplexers and includes their truth table. Diagrams of demultiplexer functions are also provided.

multiplexer and d-multiplexer

The truth table is not complete because it is missing the encoding for when no inputs are active. A complete truth table would include a row for all zero inputs to specify the output in that case.

The output equations are:

A0 = D7

A1 = D6 + D5 + D4 + D3

A2 = D2 + D1 + D0

This encodes the highest priority input on the lowest two bits, with the next two highest priorities on the middle bit, and any active input setting the highest bit.

Multiplexer and DeMultiplexer

A multiplexer has multiple inputs and a single output line, using select lines to determine which input is connected to the output. It is used to increase the amount of data that can be sent over a network. A demultiplexer is the reverse, with one input and multiple output lines, using select lines to send a signal to one of the output lines. Both are used in communication systems, computer memory, and other applications to efficiently transmit data or connect parts of a system.

multiplexer

A multiplexer (or mux) is a device that selects one of several analog or digital input signals and forwards the selected input into a single line.

COMPUTER ORGANIZATION -Multiplexer,Demultiplexer, Encoder

This document discusses multiplexers, demultiplexers, and digital encoders. It provides the following information:

- Multiplexers are digital circuits that select one of several input signals and output the selected signal. Demultiplexers perform the reverse operation.

- Multiplexers and demultiplexers come in variations depending on the number of input/output channels such as 2:1, 4:1, 16:1, etc. Their operation is illustrated using logic gates.

- Digital encoders convert binary input lines into an equivalent binary code output. Priority encoders were developed to solve issues with standard encoders generating incorrect outputs when multiple inputs are high.

Combinational circuit

An integrated circuit is a small chip of silicon that contains multiple transistors. Decoders and encoders are types of combinational logic circuits. A decoder accepts an input and uses it to activate one of its outputs, while an encoder performs the inverse by activating its outputs based on active inputs. Decoders and multiplexers are similar in that they select an output from multiple inputs, but decoders have multiple outputs while multiplexers have a single output. Multiplexers can be cascaded to increase the number of inputs selected from.

CSL 202, Multiplexer and Demultiplexer

The attached narrated power point presentation explains the working of multiplexers and demultiplexers and familiarises oneself with popular multiplexer, demultiplexer and decoder ICs. The material will be useful for KTU second year B Tech students in Computer Science and Engineering who prepare for the subject CSL 202, Digital Laboratory.

DESIGN OF COMBINATIONAL LOGIC

Here are the steps:

Binary Number 1 0 1 0

Gray Code 1 1 1 1

The Gray code for 1010 binary is 1111.

Saur lecture 16

This document summarizes a lecture on multiplexers, decoders, and encoders. It begins with definitions and examples of basic 2-to-1 multiplexers and 2-to-4 decoders. It then discusses hierarchical implementations using smaller multiplexers and decoders as building blocks. Finally, it describes techniques for designing logic circuits using multiplexers and decoders to realize Boolean functions.

Ceng232 Decoder Multiplexer Adder

The document discusses decoders, multiplexers, and programmable logic. It begins by explaining what decoders and multiplexers are, providing examples of 2-to-4 and 3-to-8 decoders. It then discusses how decoders and multiplexers can be used to implement arbitrary logic functions. The document also covers variations of decoders, building decoders from smaller components, and using multiplexers to efficiently implement functions in a sum of minterms form.

Multiplexer and demultiplexer applications.ppsx 3

This document discusses multiplexers and demultiplexers. It defines a multiplexer as a device with multiple inputs and a single output that uses select lines to determine which input is connected to the output. Demultiplexers are defined as having a single input and multiple outputs, with the select lines determining which output receives the signal. The document discusses types of multiplexers and demultiplexers and their applications in communication systems, computer memory, telephone networks, and transmitting data from satellites and computers.

عرض تقديمي1

A demultiplexer (DEMUX) is a digital switch that takes a single input signal and routes it to one of multiple outputs based on select lines. It has one input and 2^N outputs where N is the number of select lines. Common types include 1-to-2, 1-to-4, and 1-to-8 DEMUX. The document discusses DEMUX applications, provides block diagrams and truth tables to explain how a single input is routed to the correct output based on the state of the select lines.

encoder and decoder in digital electronics

In digital electronics, a decoder can take the form of a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different e.g. n-to-2n , binary-coded decimal decoders. Decoding is necessary in applications such as data multiplexing, 7 segment display and memory address decoding.

An encoder is a device, circuit, transducer, software program, algorithm or person that converts information from one format or code to another. The purpose of encoder is standardization, speed, secrecy, security, or saving space by shrinking size. Encoders are combinational logic circuits and they are exactly opposite of decoders. They accept one or more inputs and generate a multibit output code.

3. multiplexer

This document discusses multiplexers, which take multiple input signals and steer one of the inputs to the output based on control signals. It provides examples of 4-to-1, 16-to-1, and 8-to-1 multiplexers and describes how their outputs are determined by the states of the control signals. It also describes the IC 74150 16-to-1 multiplexer chip and the nibble multiplexer, which selects between two 4-bit nibbles as its output.

Mux decod pld2_vs2

This document discusses complex integrated circuits used in logic design including multiplexers, decoders, and programmable logic devices. It provides details on 4 categories of integrated circuits based on the number of gates - SSI, MSI, LSI, and VLSI. Multiplexers are described as circuits that select one of several data inputs to connect to the output based on the control inputs. Decoders are the inverse, detecting a particular input and activating the corresponding output. Programmable logic devices can be programmed to provide different logic functions, allowing for changes without rewiring the system.

Decoders

This document discusses decoders, which are circuits that take a binary input and activate one of multiple outputs. It provides examples of 2-to-4 and 3-to-8 decoders and their truth tables. Decoders are constructed using AND gates, with the number of gates equal to the number of outputs. Larger decoders can be built in parallel, balanced, or tree configurations, with balanced decoders requiring the fewest components.

08 decoder

The document describes decoders and encoders. It begins by explaining what a decoder is, providing examples of 2-to-4 and 3-to-8 decoders. It then discusses how decoders can be used to implement general logic and combinational circuits using decoders and OR gates. The document proceeds to describe specific decoder chips like the 74x139 and 74x138 decoders. It also discusses using 3-state buffers with decoders and building decoders from smaller decoders. The document then shifts to discussing encoders, 7-segment decoders, truth tables, and K-maps in the design of decoders and encoders. It concludes by discussing priority encoders and the 74x148 priority encoder chip.

What's hot (20)

COMPUTER ORGANIZATION -Multiplexer,Demultiplexer, Encoder

COMPUTER ORGANIZATION -Multiplexer,Demultiplexer, Encoder

Viewers also liked

Multiplexing

The document discusses multiplexing techniques for transmitting multiple signals across a single data link. It describes frequency division multiplexing (FDM) which is an analog technique that separates channels by assigning different frequency bands. It also describes time division multiplexing (TDM) which is a digital technique that divides the transmission path into sequential time slots to allocate to different signals in a round-robin fashion. Both multiplexing and demultiplexing processes are discussed.

Pcm pulse codemodulation-2

The document contains 38 figures that describe various digital modulation techniques used in communication systems, including PAM, PCM, ASK, FSK, PSK, QAM. It explains how analog signals are converted to digital signals using techniques like quantization and encoding. It also illustrates key concepts like Nyquist theorem, signal constellations, and the relationships between bit rate, baud rate, and bandwidth for different modulation methods.

3 multiplexing-wdm

Frequency division multiplexing (FDM) and time division multiplexing (TDM) are the most common forms of multiplexing, which is a technique that enables two or more transmission sources to share a common circuit. FDM involves modulating each signal to a different carrier frequency, with guard bands between frequencies to prevent overlap. TDM involves interleaving multiple digital signals in time by assigning time slots, which may be allocated even if no data is being sent. Synchronous optical network (SONET) is a fiber optic standard that provides a common signaling standard and multiplexing scheme to allow different carriers to interconnect and support operations and maintenance functions.

Sdh alarm presentation

1. A defect is an alarm such as loss of signals or frames, while a failure is a defect that persists beyond an allocated time threshold and can trigger automatic protection switching.

2. Common defects include loss of signal (LOS), out of frame (OOF), and loss of frame (LOF), which can be caused by issues like cable cuts, signal attenuation, or equipment faults.

3. Network protection schemes like linear and ring architectures with bidirectional and unidirectional options can provide redundancy to reroute traffic if a failure occurs on the primary path.

Multiplexing changes(2)

Multiplexing allows the simultaneous transmission of multiple signals across a single data link using techniques like frequency division multiplexing (FDM), wavelength division multiplexing (WDM), and time division multiplexing (TDM). FDM combines signals by allocating each a different frequency band. WDM is similar but uses light signals transmitted through fiber optic channels. TDM is a digital process that combines data by allocating time slots, with synchronous TDM assigning fixed slots and asynchronous TDM allowing flexible slot allocation.

Dwdm

Dense Wavelength Division Multiplexing (DWDM) is a fiber optic transmission technique that uses different wavelengths of light to carry multiple signals on the same fiber. It allows for a significant increase in network capacity by utilizing the dark fibers already in place. DWDM works by transmitting parallel signals on distinct wavelengths through the same fiber. This overcomes limitations of previous solutions like WDM and TDM by efficiently using the full bandwidth of optical fibers.

Telephone system & multiplexing

This document discusses telephone systems and multiplexing. It describes how telephone networks use circuit switching and have evolved from analog to digital systems. The basic telephone network consists of local loops connecting subscribers to switching offices, trunks connecting the offices, and switches establishing connections. Multiplexing allows transmitting multiple signals over one channel by combining them. Types of multiplexing include FDM, WDM, and TDM. FDM uses separate carrier frequencies. WDM uses different wavelengths of light. TDM transmits signals in sequential time slots. Multiplexing increases channel capacity.

Multiplexing

This document discusses different types of multiplexing techniques. It describes that multiplexing allows simultaneous transmission of multiple signals across a single data link using a multiplexer device. At the receiving end, a demultiplexer separates the combined signals. The key types of multiplexing covered are frequency division multiplexing (FDM), time division multiplexing (TDM), and wave division multiplexing (WDM). FDM uses different frequencies, TDM divides time into slots, and WDM uses different light wavelengths. Synchronous and asynchronous TDM are also explained, with synchronous TDM assigning fixed time slots and asynchronous using flexible slots.

optical time division multiplexing

This document discusses optical time division multiplexing (OTDM) systems. It outlines some of the key challenges with OTDM, including nonlinearity in fibers causing signal-to-noise ratio degradation as the number of channels increases. It also discusses the components needed for an OTDM system, including ultra-short optical pulse generation and modulation at the transmitter, and optical clock extraction and demultiplexing at the receiver. Several approaches for OTDM demultiplexing are described, such as using cascaded modulators, nonlinear optical loop mirrors, or four wave mixing in a nonlinear medium.

Introduction to dwdm technology

This document provides an introduction to Dense Wavelength Division Multiplexing (DWDM) technology. It discusses the economic drivers pushing for increased bandwidth in networks, and describes DWDM as an option for increasing carrier bandwidth by allowing multiple wavelengths of light to be transmitted simultaneously along the same fiber. The document outlines some key components of DWDM systems, such as optical fibers, light sources and detectors, optical amplifiers, and multiplexers/demultiplexers. It also notes some benefits of using DWDM with SONET, such as enhanced performance, reliability, and network management capabilities.

DWDM

The document discusses Dense Wave Division Multiplexing (DWDM) and All Optical Networking (AON). It addresses the challenges of increasing bandwidth demand and the need for network capacity expansion. DWDM allows multiple optical signals to be multiplexed onto a single fiber with no signal conversion, increasing network capacity. AON would enable fully transparent optical networks using optical cross-connects and add/drop multiplexers without optical-electrical-optical conversion. Research is ongoing to develop the technologies needed to realize AON.

Ch 06

This document discusses multiplexing techniques including frequency division multiplexing (FDM), wavelength division multiplexing (WDM), and time division multiplexing (TDM). FDM combines signals by allocating different frequency bands to different channels. WDM combines optical signals using different wavelengths of light. TDM combines data by dividing the transmission time into intervals and allocating each time slot to a different data channel in sequence. The document provides examples of applying these multiplexing techniques and calculating data rates and time intervals.

10 Slides to Sonet

SONET (Synchronous Optical Network) is a set of standards for high-speed fiber optic transmission. It defines a hierarchical structure of transmission rates and formats. SONET is predominantly used in North America, while SDH (Synchronous Digital Hierarchy) is used internationally. SONET frames carry overhead information and payload. Lower rate signals can be mapped into virtual tributaries within SONET frames. SONET networks use rings and point-to-point configurations to provide redundancy and transport services.

Aml cft training programme

This document provides an overview of money laundering and combating the financing of terrorism. It discusses what money laundering is, the stages of money laundering (placement, layering, integration), and how it works. It also discusses terrorist financing. International efforts to combat money laundering and terrorist financing through organizations like the UN, FATF, and Egmont Group are overviewed. The roles and functions of India's Financial Intelligence Unit (FIU-IND) are described. The document also outlines India's Prevention of Money Laundering Act (PMLA) and its provisions, including scheduled offenses, punishments, and authorities for enforcement. Obligations of banks and financial institutions under PMLA around client identification,

Optical Networking & DWDM

Bandwidth is Becoming Commodity

:

Price per bit went down by 99% in the last 5 years on the optical side

This is one of the problems of the current telecom market

Optical Metro – cheap high bandwidth access

$1000 a month for 100FX (in major cities)

This is less than the cost of T1 several years ago

Optical Long-Haul and Metro access - change of the price point

Reasonable price drive more users (non residential)

Sdh total final

This document provides an overview of Synchronous Digital Hierarchy (SDH) including its introduction, components, frame structure, and applications. SDH was developed to provide a standardized digital transmission network with vendor independence. It uses optical fiber to enable end-to-end monitoring and self-healing ring architectures for survivability. The SDH frame structure consists of sections for transport overhead (TOH), path overhead (POH), and payloads. SDH supports multiplexing of various signals like E1, DS1, and STM streams. It allows dynamic bandwidth allocation and is a platform for future services.

Sonet Sdh Dwdm

SONET/SDH are digital fiber optic transmission standards developed independently in the US and Europe to transmit data at high speeds over fiber optic cables. SONET defines a hierarchy of electrical signaling levels called STS and uses synchronous TDM multiplexing. It can transmit data from 155 Mbps to 2.5 Gbps and supports ring topologies. SONET defines layers for signal transmission including path, line, section and physical layers. SDH is the international version of SONET and uses similar framing and network elements like multiplexers, regenerators and cross-connects to transmit digital signals over fiber optic networks. DWDM further increases fiber capacity by transmitting multiple wavelengths/channels over the same fiber using wavelength division

dwdm

The document provides an overview of optical DWDM fundamentals, including terminology, fiber characteristics, and transmission effects. It discusses key topics such as optical propagation in fibers, attenuation and compensation using optical amplifiers, dispersion types and limitations, and wavelength grids. Diagrams and examples are used to illustrate optical power measurements, budgets, safety classifications, and the impacts of attenuation and dispersion on transmission performance.

DWDM Presentation

This document provides an overview of Dense Wavelength Division Multiplexing (DWDM) technology. It discusses key topics such as optical transmission, DWDM components like multiplexers/demultiplexers and amplifiers, DWDM networks and topologies, and transmission quality parameters. The presentation contains 32 slides and is intended to briefly explain DWDM as a means of achieving effective fiber-optic transmission and increasing bandwidth.

Fundamentals of sdh

The document discusses key concepts in digital telecommunication networks including Pulse Code Modulation (PCM), Plesiochronous Digital Hierarchy (PDH), Synchronous Digital Hierarchy (SDH), and their frame structures and bit rates. It describes how lower bit rate signals such as E1 (2Mbps) are mapped into higher bit rate structures like STM-1 (155.52Mbps) through multiplexing techniques involving containers, virtual containers, tributary units, and administrative units. The document also outlines the section overhead bytes used in SDH for functions like frame alignment, error monitoring, and automatic protection switching.

Viewers also liked (20)

Similar to 10 multiplexers-de mux

Logic Design - Chapter 5: Part1 Combinattional Logic

The document discusses common digital logic circuits including decoders, encoders, demultiplexers and multiplexers. It provides an overview of how these circuits work at a block level and then goes into more detail on decoders, describing their functionality, truth tables, and implementations including how to build larger decoders from smaller ones. Standard MSI decoder chips are also presented.

unit-6_combinational_jbiunkjnjbkjbjjcircuit-2.ppt

This document discusses combinational logic circuits such as multiplexers, demultiplexers, decoders, and encoders. It provides examples of truth tables and circuit implementations for 1-to-4 demultiplexers and decoders. Larger decoders can be constructed by combining smaller decoders. Decoders can be used to implement logic functions such as a full adder. Encoders are the opposite of decoders, with multiple inputs and fewer outputs, such as an octal-to-binary encoder that converts 8 input lines to 3 output lines.

ANALYSIS & DESIGN OF COMBINATIONAL LOGIC

The document provides instructions for a unit assignment involving simplification of logic expressions using the Variable Elimination Method (VEM) technique. It lists 3 steps - 1) simplify an expression using VEM, 2) obtain the minimal product, 3) simplify another expression using VEM. It then provides 4 logic expressions that need simplification.

ENG 202 – Digital Electronics 1 - Chapter 4 (1).pptx

The document discusses combinational logic circuits including decoders, encoders, multiplexers and demultiplexers. It explains that decoders convert coded inputs to coded outputs, with only one output active at a time. Examples of 2-to-4 and 3-to-8 decoders are provided along with their truth tables and logic diagrams. Encoders perform the reverse function of decoders. Multiplexers allow selecting one of several data inputs to output, while demultiplexers distribute a single input to multiple outputs. Applications in designing logic functions using decoders and multiplexers are also covered.

Chapter 06 Combinational Logic Functions

This document discusses various combinational logic circuits including decoders, encoders, multiplexers, and demultiplexers. It provides examples of their functionality and truth tables. It also shows how these circuits can be modeled in VHDL using constructs like concurrent signal assignment statements, select signal assignment statements, and case statements. Processes and sensitivity lists are discussed for modeling sequential logic. Applications like address decoding and time division multiplexing are also mentioned.

Unit 4 dica

The document discusses combinational logic circuits. It describes combinational logic design procedures including specification, formulation, optimization, technology mapping, and verification. It also discusses analysis procedures for logic diagrams, including labeling gate outputs and determining Boolean functions. Additional topics covered include half adders, full adders, binary adders, decoders, encoders, multiplexers, priority encoders, and binary-coded decimal to seven-segment displays. Diagrams and truth tables are provided for various logic gates and circuits.

Lcdf4 chap 03_p2

This document discusses combinational logic design, specifically combinational logic functions and their implementation using decoders and multiplexers. It provides an overview of combinational logic and covers topics like rudimentary logic functions, decoding using decoders, encoding using encoders, and selecting using multiplexers. Examples are given for implementing combinational logic functions with decoders and multiplexers. Procedures for expanding decoders and multiplexers to handle more inputs and outputs are also described.

microprocessors

The document provides an overview of microprocessors and microcontrollers. It discusses the history and evolution of microprocessors from early minicomputers in the 1960s to modern microcontrollers that integrate CPU, memory and I/O onto a single chip. The document outlines common microprocessor components like registers, ALU, buses and control units. It also covers digital logic gates, memory systems, number representations and instruction sets.

Coa presentation2

This document provides information about various digital circuits including half adder, full adder, encoder, decoder, multiplexer, demultiplexer, seven segment display circuit, clock, flip flop, integrated circuit and more. It defines combinational and sequential circuits. It describes half adder, full adder, encoder, decoder, multiplexer, demultiplexer and seven segment display circuits. It also explains clock, flip flops including SR, D, JK flip flops, integrated circuits and definitions.

Clock Sources on ZedBoard.pdf

This document discusses clock sources and peripheral modules on the ZedBoard. It describes the different clock sources available, including a 100 MHz on-board oscillator. It also shows how to generate clocks of different frequencies using clock division. As an example, it demonstrates connecting and driving a seven segment display Pmod peripheral module to display digits using time multiplexing at a rate of 50 Hz or faster.

VLSI Design Final Project - 32 bit ALU

An Arithmetic Logic Unit (ALU) is a functional block of any

processor. It is used to perform arithmetical and logical

operations. ALU’s are designed to perform integer based

operations. In this module, we have designed an ALU which

performs certain specific operations on 32 bit numbers.

The arithmetic operations performed are: Addition, subtraction

and multiplication. The logical operations performed are: AND,

OR, XNOR, left shift and right shift.

The behavioral Verilog code and testbench were simulated using

MODELSIM to verify the functionality.

The individual gates (INVERTER, NAND2, NOR2, XOR2, OAI3222,

AOI22, MUX2:1) which constituted to the cell library were laid out

in CADENCE. The DRC and LVS run were successfully completed

to ensure usage. These individual layouts were combined and the

combined DRC was run without any errors.

The D flip flop (DFF) was laid out and the static timing analysis

were done using Waveform viewer and it’s functionality was

verified and the D flip flop times were calculated.

By putting together these cells which were designed, the ALU was

developed and the outputs were obtained.

Bidirect visitor counter

This document describes an energy saving visitor counter project that uses a microcontroller and infrared sensors. The objective is to design a circuit that can count the number of people entering and exiting a room and control the room light accordingly. It uses an IR transmitter and receiver to detect movement and increments or decrements the counter value, which is displayed on seven-segment displays. The microcontroller controls the counting and display functionality while receiving input from the IR sensors. Proteus and Keil software are used to simulate and program the microcontroller respectively.

Logic gate tester for IC's ( Digital Electronics and Logic deisgn EE3114 )

Name of the project: Logic Gate Tester for DELD EE3114

1.1Abstract:

Performing various types of logic operation we need to use logic gates and in integrated circuit there are more than one gates fabricated in a single IC. Before using gates for various purposes we need to check logic gates including all logic

combination considering in Binary (Logic 1 & 0) needs to implement. It is a time consuming task to check all the input combinations, thus the sole purpose of this project to make it automatic to check all the logic .

Lecture 1

This document provides an introduction to medium scale integrated (MSI) circuits. It defines MSI circuits as containing between 12-99 logic gates. Examples of MSI circuits discussed include multiplexers, demultiplexers, decoders, encoders, and adders. Common integrated circuit chip families for implementing MSI circuits are presented, such as the 74x151 for multiplexers. The document also discusses implementing various logic functions using MSI building blocks like multiplexers, decoders, and priority encoders.

Laboratory exercise 5

This document describes a laboratory exercise involving the use of timers and real-time clocks implemented on an Altera DE0 board. It involves designing and implementing four circuits: 1) a modulo-k counter, 2) a 3-digit BCD counter, 3) a real-time clock displaying minutes and seconds, and 4) a circuit displaying Morse code representations of letters using LEDs. VHDL is used to describe the circuits, which are then compiled, simulated, and downloaded to the DE0 board for testing. Preparation includes writing and simulating VHDL code for parts I-III.

Analog to Digital Converter

This document describes experiments with analog to digital converters (ADCs) using an 8-bit and 10-bit converter to read voltage input and display the results on a 7-segment LED display. It provides algorithms and code for initializing the ADC, taking samples, and performing conversions to extract the digital values for display. Procedures are outlined for 8-bit and 10-bit conversions using interrupts or polling and arithmetic operations to handle the 10-bit values.

Digital Logic circuit

This document provides an overview of digital logic circuits and sequential circuits. It discusses various logic gates like OR, AND, NOT, NAND, NOR and XOR gates. It explains their truth tables and symbols. It also covers Boolean algebra, map simplification using K-maps, combinational circuits like multiplexers, demultiplexers, encoders and decoders. Finally, it describes different types of flip-flops like SR, D, JK and T flip-flops which are used to build sequential circuits that have memory and can store past states.

Ecad &vlsi lab 18

This document contains the laboratory manual for the ECAD & VLSI Design course for the 4th semester ECE students of Malla Reddy College of Engineering and Technology. It includes 15 experiments on digital circuit design using Verilog HDL. The experiments cover designing basic digital components like full adder, ripple carry adder, carry save adder, carry select adder, BCD adder, multiplexer, array multiplier, counters, ring counter, PRBS generator, accumulator. It also includes designing basic CMOS logic gates like inverter, NAND, NOR, XOR gates and a 1-bit CMOS full adder. The last two experiments are on CMOS common source amplifier and differential amplifier.

4,encoder & decoder MUX and DEMUX EEng - Copy.pdf

This document discusses various combinational logic functions including decoding, encoding, multiplexing, and decoding. It provides details on decoder and encoder circuits. Decoders accept a binary input and activate only one output corresponding to that input. Encoders have multiple inputs but activate only one at a time, producing a binary output code. Examples of 3-line to 8-line decoders and 8-line to 3-line encoders are shown with their truth tables.

Fpga creating counter with internal clock

This document describes a design for a counter seven segment display using an FPGA. The author implemented a counter component and a decoder component, then wired them together in a top-level systemSeg entity using port mapping. The counter counts from 0 to 9 and outputs a 4-bit binary coded decimal value. The decoder converts the 4-bit input to a 7-segment display output based on a case statement. The author notes that port mapping is useful for wiring components together in HDL and that designs need to be synchronous with a clock.

Similar to 10 multiplexers-de mux (20)

Logic Design - Chapter 5: Part1 Combinattional Logic

Logic Design - Chapter 5: Part1 Combinattional Logic

ENG 202 – Digital Electronics 1 - Chapter 4 (1).pptx

ENG 202 – Digital Electronics 1 - Chapter 4 (1).pptx

Logic gate tester for IC's ( Digital Electronics and Logic deisgn EE3114 )

Logic gate tester for IC's ( Digital Electronics and Logic deisgn EE3114 )

Recently uploaded

A SYSTEMATIC RISK ASSESSMENT APPROACH FOR SECURING THE SMART IRRIGATION SYSTEMS

The smart irrigation system represents an innovative approach to optimize water usage in agricultural and landscaping practices. The integration of cutting-edge technologies, including sensors, actuators, and data analysis, empowers this system to provide accurate monitoring and control of irrigation processes by leveraging real-time environmental conditions. The main objective of a smart irrigation system is to optimize water efficiency, minimize expenses, and foster the adoption of sustainable water management methods. This paper conducts a systematic risk assessment by exploring the key components/assets and their functionalities in the smart irrigation system. The crucial role of sensors in gathering data on soil moisture, weather patterns, and plant well-being is emphasized in this system. These sensors enable intelligent decision-making in irrigation scheduling and water distribution, leading to enhanced water efficiency and sustainable water management practices. Actuators enable automated control of irrigation devices, ensuring precise and targeted water delivery to plants. Additionally, the paper addresses the potential threat and vulnerabilities associated with smart irrigation systems. It discusses limitations of the system, such as power constraints and computational capabilities, and calculates the potential security risks. The paper suggests possible risk treatment methods for effective secure system operation. In conclusion, the paper emphasizes the significant benefits of implementing smart irrigation systems, including improved water conservation, increased crop yield, and reduced environmental impact. Additionally, based on the security analysis conducted, the paper recommends the implementation of countermeasures and security approaches to address vulnerabilities and ensure the integrity and reliability of the system. By incorporating these measures, smart irrigation technology can revolutionize water management practices in agriculture, promoting sustainability, resource efficiency, and safeguarding against potential security threats.

Literature Review Basics and Understanding Reference Management.pptx

Three-day training on academic research focuses on analytical tools at United Technical College, supported by the University Grant Commission, Nepal. 24-26 May 2024

The Python for beginners. This is an advance computer language.

Python language is very important language at this time. we can easily understand this language by these notes.

Harnessing WebAssembly for Real-time Stateless Streaming Pipelines

Traditionally, dealing with real-time data pipelines has involved significant overhead, even for straightforward tasks like data transformation or masking. However, in this talk, we’ll venture into the dynamic realm of WebAssembly (WASM) and discover how it can revolutionize the creation of stateless streaming pipelines within a Kafka (Redpanda) broker. These pipelines are adept at managing low-latency, high-data-volume scenarios.

Electric vehicle and photovoltaic advanced roles in enhancing the financial p...

Climate change's impact on the planet forced the United Nations and governments to promote green energies and electric transportation. The deployments of photovoltaic (PV) and electric vehicle (EV) systems gained stronger momentum due to their numerous advantages over fossil fuel types. The advantages go beyond sustainability to reach financial support and stability. The work in this paper introduces the hybrid system between PV and EV to support industrial and commercial plants. This paper covers the theoretical framework of the proposed hybrid system including the required equation to complete the cost analysis when PV and EV are present. In addition, the proposed design diagram which sets the priorities and requirements of the system is presented. The proposed approach allows setup to advance their power stability, especially during power outages. The presented information supports researchers and plant owners to complete the necessary analysis while promoting the deployment of clean energy. The result of a case study that represents a dairy milk farmer supports the theoretical works and highlights its advanced benefits to existing plants. The short return on investment of the proposed approach supports the paper's novelty approach for the sustainable electrical system. In addition, the proposed system allows for an isolated power setup without the need for a transmission line which enhances the safety of the electrical network

Optimizing Gradle Builds - Gradle DPE Tour Berlin 2024

Sinan from the Delivery Hero mobile infrastructure engineering team shares a deep dive into performance acceleration with Gradle build cache optimizations. Sinan shares their journey into solving complex build-cache problems that affect Gradle builds. By understanding the challenges and solutions found in our journey, we aim to demonstrate the possibilities for faster builds. The case study reveals how overlapping outputs and cache misconfigurations led to significant increases in build times, especially as the project scaled up with numerous modules using Paparazzi tests. The journey from diagnosing to defeating cache issues offers invaluable lessons on maintaining cache integrity without sacrificing functionality.

A review on techniques and modelling methodologies used for checking electrom...

The proper function of the integrated circuit (IC) in an inhibiting electromagnetic environment has always been a serious concern throughout the decades of revolution in the world of electronics, from disjunct devices to today’s integrated circuit technology, where billions of transistors are combined on a single chip. The automotive industry and smart vehicles in particular, are confronting design issues such as being prone to electromagnetic interference (EMI). Electronic control devices calculate incorrect outputs because of EMI and sensors give misleading values which can prove fatal in case of automotives. In this paper, the authors have non exhaustively tried to review research work concerned with the investigation of EMI in ICs and prediction of this EMI using various modelling methodologies and measurement setups.

哪里办理(csu毕业证书)查尔斯特大学毕业证硕士学历原版一模一样

原版一模一样【微信:741003700 】【(csu毕业证书)查尔斯特大学毕业证硕士学历】【微信:741003700 】学位证,留信认证(真实可查,永久存档)offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原海外各大学 Bachelor Diploma degree, Master Degree Diploma

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微741003700

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

Eric Nizeyimana's document 2006 from gicumbi to ttc nyamata handball play

this notes have been created

by Eric36 at nyamata ttc

after readings

pe book for y2sme .

DEEP LEARNING FOR SMART GRID INTRUSION DETECTION: A HYBRID CNN-LSTM-BASED MODEL

As digital technology becomes more deeply embedded in power systems, protecting the communication

networks of Smart Grids (SG) has emerged as a critical concern. Distributed Network Protocol 3 (DNP3)

represents a multi-tiered application layer protocol extensively utilized in Supervisory Control and Data

Acquisition (SCADA)-based smart grids to facilitate real-time data gathering and control functionalities.

Robust Intrusion Detection Systems (IDS) are necessary for early threat detection and mitigation because

of the interconnection of these networks, which makes them vulnerable to a variety of cyberattacks. To

solve this issue, this paper develops a hybrid Deep Learning (DL) model specifically designed for intrusion

detection in smart grids. The proposed approach is a combination of the Convolutional Neural Network

(CNN) and the Long-Short-Term Memory algorithms (LSTM). We employed a recent intrusion detection

dataset (DNP3), which focuses on unauthorized commands and Denial of Service (DoS) cyberattacks, to

train and test our model. The results of our experiments show that our CNN-LSTM method is much better

at finding smart grid intrusions than other deep learning algorithms used for classification. In addition,

our proposed approach improves accuracy, precision, recall, and F1 score, achieving a high detection

accuracy rate of 99.50%.

ACEP Magazine edition 4th launched on 05.06.2024

This document provides information about the third edition of the magazine "Sthapatya" published by the Association of Civil Engineers (Practicing) Aurangabad. It includes messages from current and past presidents of ACEP, memories and photos from past ACEP events, information on life time achievement awards given by ACEP, and a technical article on concrete maintenance, repairs and strengthening. The document highlights activities of ACEP and provides a technical educational article for members.

Recycled Concrete Aggregate in Construction Part II

Using recycled concrete aggregates (RCA) for pavements is crucial to achieving sustainability. Implementing RCA for new pavement can minimize carbon footprint, conserve natural resources, reduce harmful emissions, and lower life cycle costs. Compared to natural aggregate (NA), RCA pavement has fewer comprehensive studies and sustainability assessments.

Modelagem de um CSTR com reação endotermica.pdf

Modelagem em função de transferencia. CSTR não-linear.

Advanced control scheme of doubly fed induction generator for wind turbine us...

This paper describes a speed control device for generating electrical energy on an electricity network based on the doubly fed induction generator (DFIG) used for wind power conversion systems. At first, a double-fed induction generator model was constructed. A control law is formulated to govern the flow of energy between the stator of a DFIG and the energy network using three types of controllers: proportional integral (PI), sliding mode controller (SMC) and second order sliding mode controller (SOSMC). Their different results in terms of power reference tracking, reaction to unexpected speed fluctuations, sensitivity to perturbations, and resilience against machine parameter alterations are compared. MATLAB/Simulink was used to conduct the simulations for the preceding study. Multiple simulations have shown very satisfying results, and the investigations demonstrate the efficacy and power-enhancing capabilities of the suggested control system.

2008 BUILDING CONSTRUCTION Illustrated - Ching Chapter 02 The Building.pdf

2008 BUILDING CONSTRUCTION Illustrated - Ching Chapter 02 The Building

Recently uploaded (20)

A SYSTEMATIC RISK ASSESSMENT APPROACH FOR SECURING THE SMART IRRIGATION SYSTEMS

A SYSTEMATIC RISK ASSESSMENT APPROACH FOR SECURING THE SMART IRRIGATION SYSTEMS

Literature Review Basics and Understanding Reference Management.pptx

Literature Review Basics and Understanding Reference Management.pptx

The Python for beginners. This is an advance computer language.

The Python for beginners. This is an advance computer language.

Harnessing WebAssembly for Real-time Stateless Streaming Pipelines

Harnessing WebAssembly for Real-time Stateless Streaming Pipelines

Electric vehicle and photovoltaic advanced roles in enhancing the financial p...

Electric vehicle and photovoltaic advanced roles in enhancing the financial p...

Generative AI leverages algorithms to create various forms of content

Generative AI leverages algorithms to create various forms of content

ML Based Model for NIDS MSc Updated Presentation.v2.pptx

ML Based Model for NIDS MSc Updated Presentation.v2.pptx

Optimizing Gradle Builds - Gradle DPE Tour Berlin 2024

Optimizing Gradle Builds - Gradle DPE Tour Berlin 2024

A review on techniques and modelling methodologies used for checking electrom...

A review on techniques and modelling methodologies used for checking electrom...

Eric Nizeyimana's document 2006 from gicumbi to ttc nyamata handball play

Eric Nizeyimana's document 2006 from gicumbi to ttc nyamata handball play

BPV-GUI-01-Guide-for-ASME-Review-Teams-(General)-10-10-2023.pdf

BPV-GUI-01-Guide-for-ASME-Review-Teams-(General)-10-10-2023.pdf

DEEP LEARNING FOR SMART GRID INTRUSION DETECTION: A HYBRID CNN-LSTM-BASED MODEL

DEEP LEARNING FOR SMART GRID INTRUSION DETECTION: A HYBRID CNN-LSTM-BASED MODEL

Recycled Concrete Aggregate in Construction Part II

Recycled Concrete Aggregate in Construction Part II

Advanced control scheme of doubly fed induction generator for wind turbine us...

Advanced control scheme of doubly fed induction generator for wind turbine us...

2008 BUILDING CONSTRUCTION Illustrated - Ching Chapter 02 The Building.pdf

2008 BUILDING CONSTRUCTION Illustrated - Ching Chapter 02 The Building.pdf

10 multiplexers-de mux

- 1. 1 CSE370, Lecture 10 Overview Last lecture Timing diagrams Multilevel logic Multilevel NAND/NOR conversion AOI and OAI gates Hazards Today "Switching-network" logic blocks Multiplexers/selectors Demultiplexers/decoders Programmable logic devices (PLDs) Regular structures for 2-level logic 2 CSE370, Lecture 10 Switching-network logic blocks Multiplexer Routes one of many inputs to a single output Also called a selector Demultiplexer Routes a single input to one of many outputs Also called a decoder multiplexer demultiplexer control control We construct these devices from: (1) logic gates (2) networks of tran- sistor switches 3 CSE370, Lecture 10 Rationale: Sharing complex logic functions Share an adder: Select inputs; route sum multiple inputs multiple output destinations MUX A B Sum A0 A1 Sa Ss Sb B0 B1 MUX DEMUX Z0 Z1 single adder 4 CSE370, Lecture 10 Multiplexers Basic concept 2n data inputs; n control inputs ("selects"); 1 output Connects one of 2n inputs to the output “Selects” decide which input connects to output Two alternative truth-tables: Functional and Logical Example: A 2:1 Mux Z = SIn1 + S'Ino Functional truth table S Z 0 In0 1 In1 In1 In0 S Z 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 0 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 Logical truth table I0 S I1 Z

- 2. 5 CSE370, Lecture 10 Logic-gate implementation of multiplexers 2:1 mux 4:1 mux I0 I1 I2 I3 S0 S1 I0 S I1 I0 S I1 Z Z Z 6 CSE370, Lecture 10 Multiplexers (con't) 2:1 mux: Z = S'In0 + SIn1 4:1 mux: Z = S0'S1'In0 + S0'S1In1 + S0S1'In2 + S0S1In3 8:1 mux: Z = S0'S1'S2'In0 + S0'S1S2In1 + ... I0 I1 I2 I3 I4 I5 I6 I7 S0 S1 S2 8:1 mux Z I0 I1 I2 I3 S0 S1 4:1 mux Z I0 I1 S0 2:1 mux Z 7 CSE370, Lecture 10 Cascading multiplexers Can form large multiplexers from smaller ones Many implementation options Z 4:1 mux S2 2:1 mux I4 I5 I6 I7 S0 S1 4:1 mux S0 Z S1 S2 4:1 mux 2:1 mux 2:1 mux 2:1 mux 2:1 mux I4 I5 I2 I3 I0 I1 I6 I7 8:1 mux 8:1 mux I0 I1 I2 I3 8 CSE370, Lecture 10 Multiplexers as general-purpose logic A 2n:1 mux can implement any function of n variables A lookup table A 2n – 1 :1 mux also can implement any function of n variables Example: F(A,B,C) = m0 + m2 + m6 + m7 = A'B'C' + A'BC' + ABC' + ABC = A'B'(C') + A'B(C') + AB(0) + AB(1) A B C F 0 0 0 1 0 0 1 0 0 1 0 1 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 1 1 1 1 1 C' C' 0 1 S1 S0 F 0 1 2 3 4:1 MUX C' C' 0 1 0 1 2 3 4 5 6 7 1 0 1 0 0 0 1 1 S2 8:1 MUX S1 S0 F A B C A B

- 3. 9 CSE370, Lecture 10 Multiplexers as general-purpose logic Implementing a 2n:1 mux as a function of n–1 variables (n-1) mux control variables S0 – Sn–1 One data variable Sn Four possible values for each data input: 0, 1, Sn, Sn' Example: F(A,B,C,D) implemented using an 8:1 mux Choose A,B,C as control variables Choose D as a data variable 0 1 2 3 4 5 6 7 1 D 0 1 D' D D' D' A 8:1 MUX B C F D 1 0 1 1 1 0 0 0 1 1 0 1 0 1 1 0 AB CD A 00 01 11 10 00 01 11 10 C B S2 S1 S0 F=A’B’C’(1)+A’B’C(D)+A’BC’(0)+A’BC(1) +AB’C’(D’)+AB’C(D)+ABC’(D’)+ABC(D’) F = A’B’C’+A’CD+B’CD+AC’D’+BCD’ 10 CSE370, Lecture 10 Demultiplexers Basic concept Single data input; n control inputs (“selects”); 2n outputs Single input connects to one of 2n outputs “Selects” decide which output is connected to the input When used as a decoder, the input is called an “enable” (G) 1:2 Decoder: Out0 = G • S' Out1 = G • S 2:4 Decoder: Out0 = G • S1' • S0' Out1 = G • S1' • S0 Out2 = G • S1 • S0' Out3 = G • S1 • S0 3:8 Decoder: Out0 = G • S2' • S1' • S0' Out1 = G • S2' • S1' • S0 Out2 = G • S2' • S1 • S0' Out3 = G • S2' • S1 • S0 Out4 = G • S2 • S1' • S0' Out5 = G • S2 • S1' • S0 Out6 = G • S2 • S1 • S0' Out7 = G • S2 • S1 • S0 11 CSE370, Lecture 10 Logic-gate implementation of demultiplexers 1:2 demux Out0 G S Out1 S1 Out2 Out3 Out0 G Out1 S0 2:4 demux 12 CSE370, Lecture 10 Demultiplexers as general-purpose logic A n:2n demux can implement any function of n variables Use variables as select inputs Tie enable input to logic 1 Sum the appropriate minterms (extra OR gate) demultiplexer “decodes” appropriate minterms from the control signals C A B 0 A'B'C' 1 A'B'C 2 A'BC' 3 A'BC 4 AB'C' 5 AB'C 6 ABC' 7 ABC S2 3:8 Demux S1 S0 1

- 4. 13 CSE370, Lecture 10 Demultiplexers as general-purpose logic Example F1 = A'BC'D + A'B'CD + ABCD F2 = ABC'D' + ABC F3 = (A'+B'+C'+D') A B 0 A'B'C'D' 1 A'B'C'D 2 A'B'CD' 3 A'B'CD 4 A'BC'D' 5 A'BC'D 6 A'BCD' 7 A'BCD 8 AB'C'D' 9 AB'C'D 10 AB'CD' 11 AB'CD 12 ABC'D' 13 ABC'D 14 ABCD' 15 ABCD 4:16 Demux Enable = 1 C D F1 F2 F3 14 CSE370, Lecture 10 Cascading demultiplexers 5:32 demux 0 A'B'C'D'E' 1 2 3 4 5 6 7 S2 3:8 Demux S1 S0 A B 0 1 2 3 S1 2:4 Demux S0 F E C D 0 1 2 3 4 5 6 7 ABCDE S2 S1 S0 0 1 2 A'BC'DE' 3 4 5 6 7 S2 S1 S0 E C D 0 AB'C'D'E' 1 2 3 4 5 6 7 AB'CDE S2 S1 S0 3:8 Demux 3:8 Demux 3:8 Demux 15 CSE370, Lecture 10 • • • • • • inputs outputs product terms AND array OR array Programmable logic (PLAs & PALs ) Concept: Large array of uncommitted AND/OR gates Actually NAND/NOR gates You program the array by making or breaking connections Programmable block for sum-of-products logic 16 CSE370, Lecture 10 All two-level logic functions are available You "program" the wire connections A 3-input, 5-term, 4-function PLA

- 5. 17 CSE370, Lecture 10 Sharing product terms Example: F0 = A + B'C' F1 = AC' + AB F2 = B'C' + AB F3 = B'C + A Personality matrix: 1 = asserted in term 0 = negated in term – = does not participate inputs 1 = term connected to output 0 = no connection to output outputs product inputs outputs term A B C F0 F1 F2 F3 AB 1 1 – 0 1 1 0 B'C – 0 1 0 0 0 1 AC' 1 – 0 0 1 0 0 B'C' – 0 0 1 0 1 0 A 1 – – 1 0 0 1 Reuse terms 18 CSE370, Lecture 10 Programming the wire connections Fuse: Comes connected; break unwanted connections Anti-fuse: Comes disconnected; make wanted connections A B C F1 F2 F3 F0 AB B'C AC' B'C' A F0 = A + B'C' F1 = AC' + AB F2 = B'C' + AB F3 = B'C + A