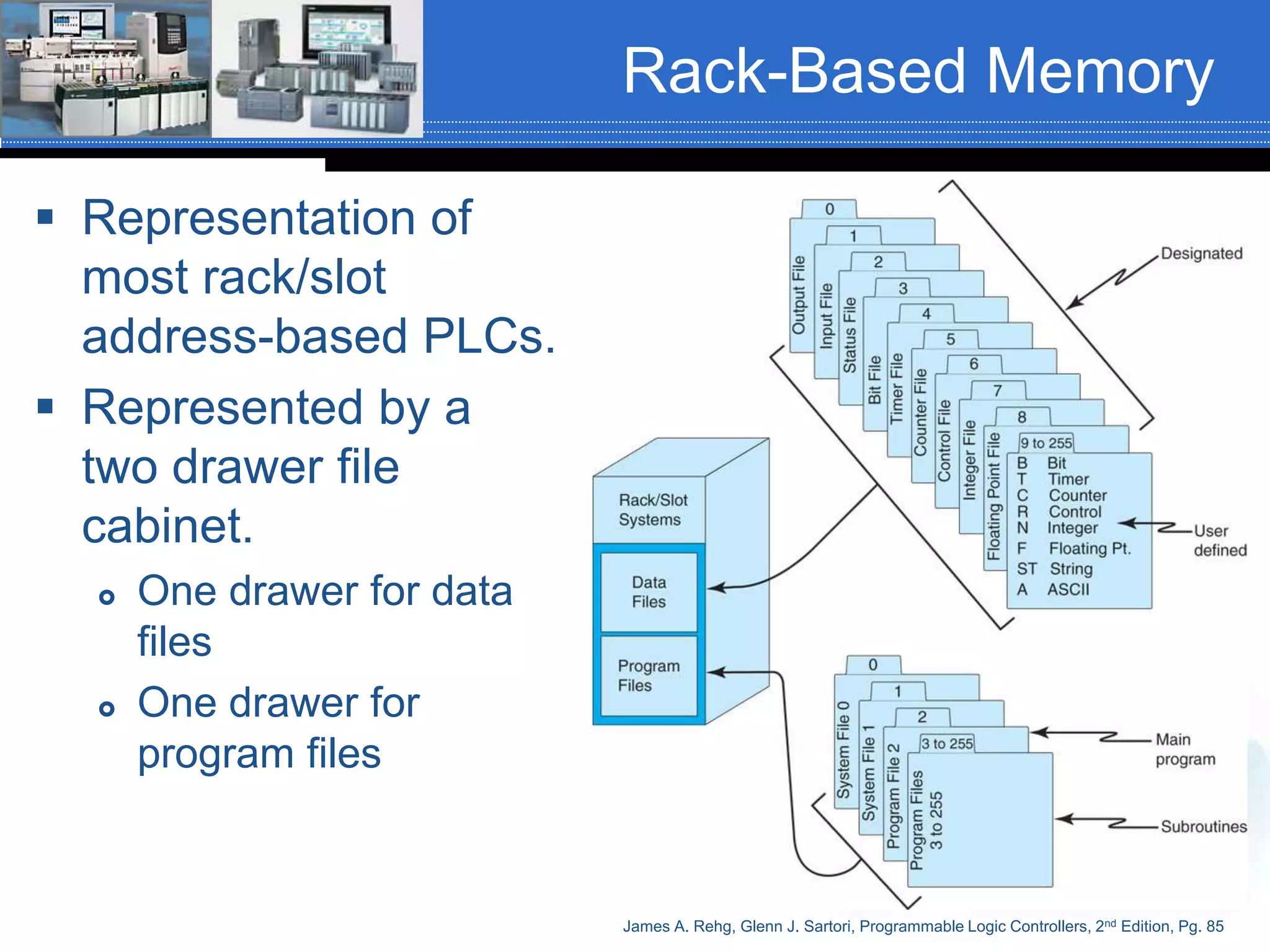

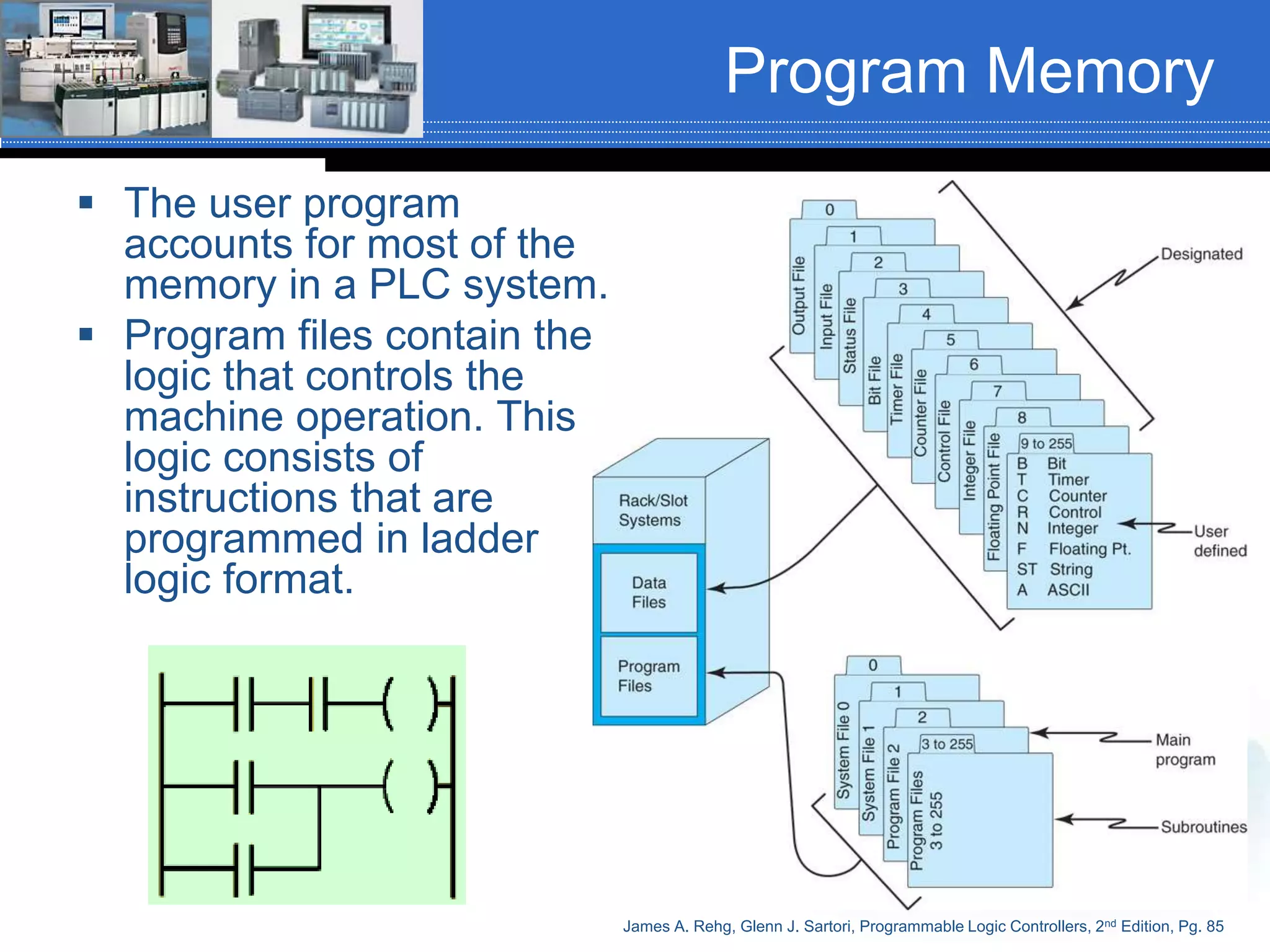

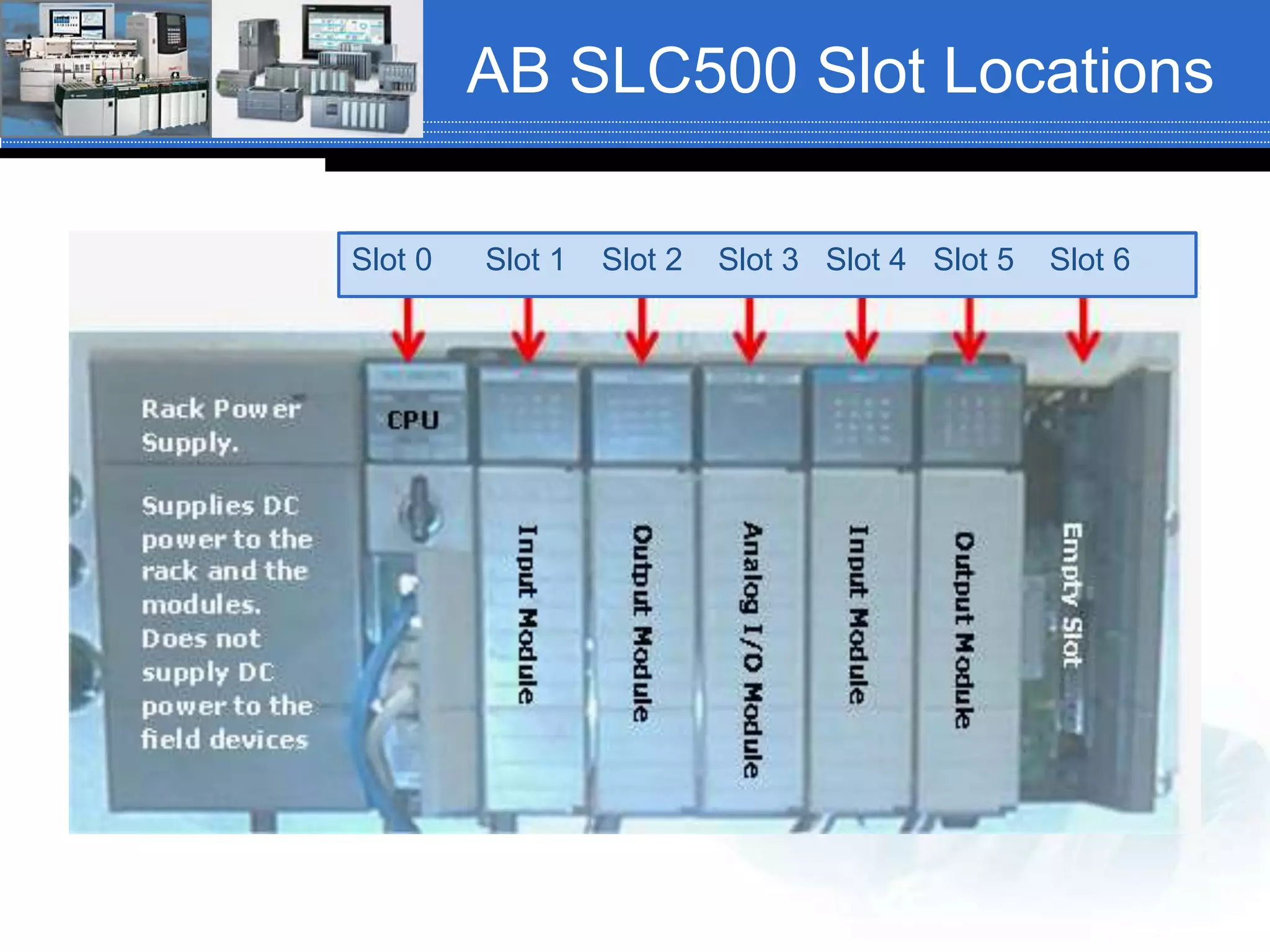

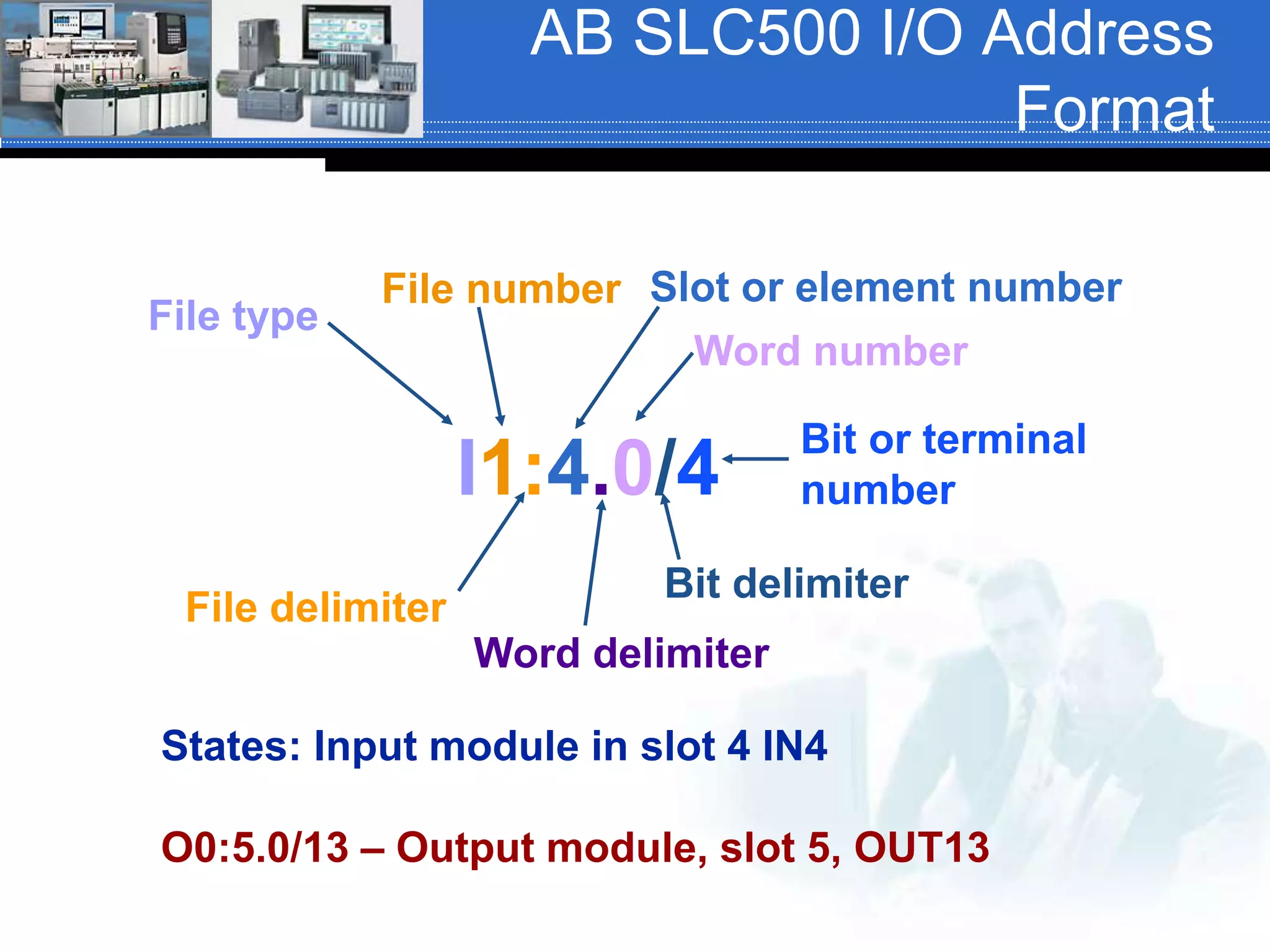

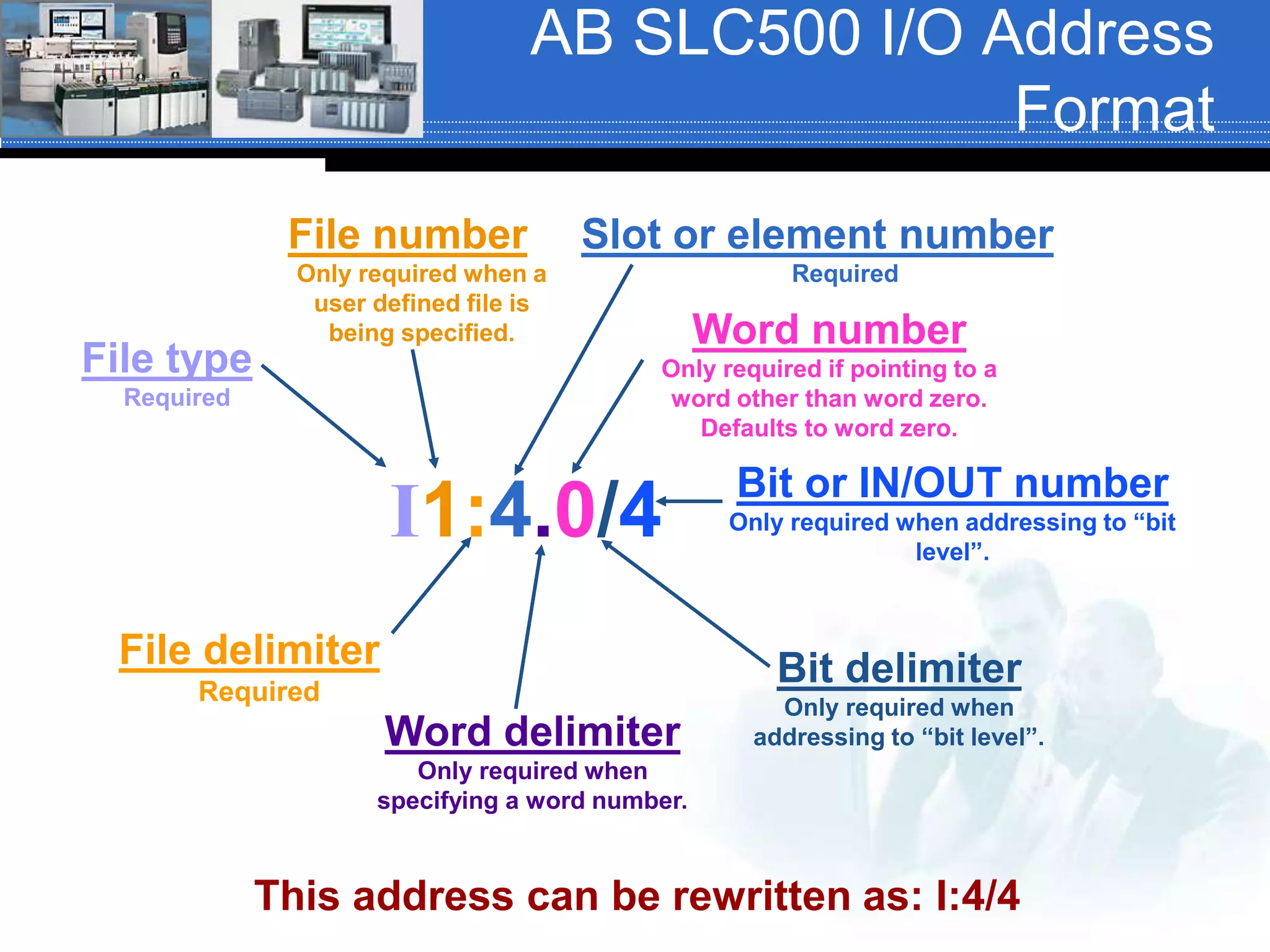

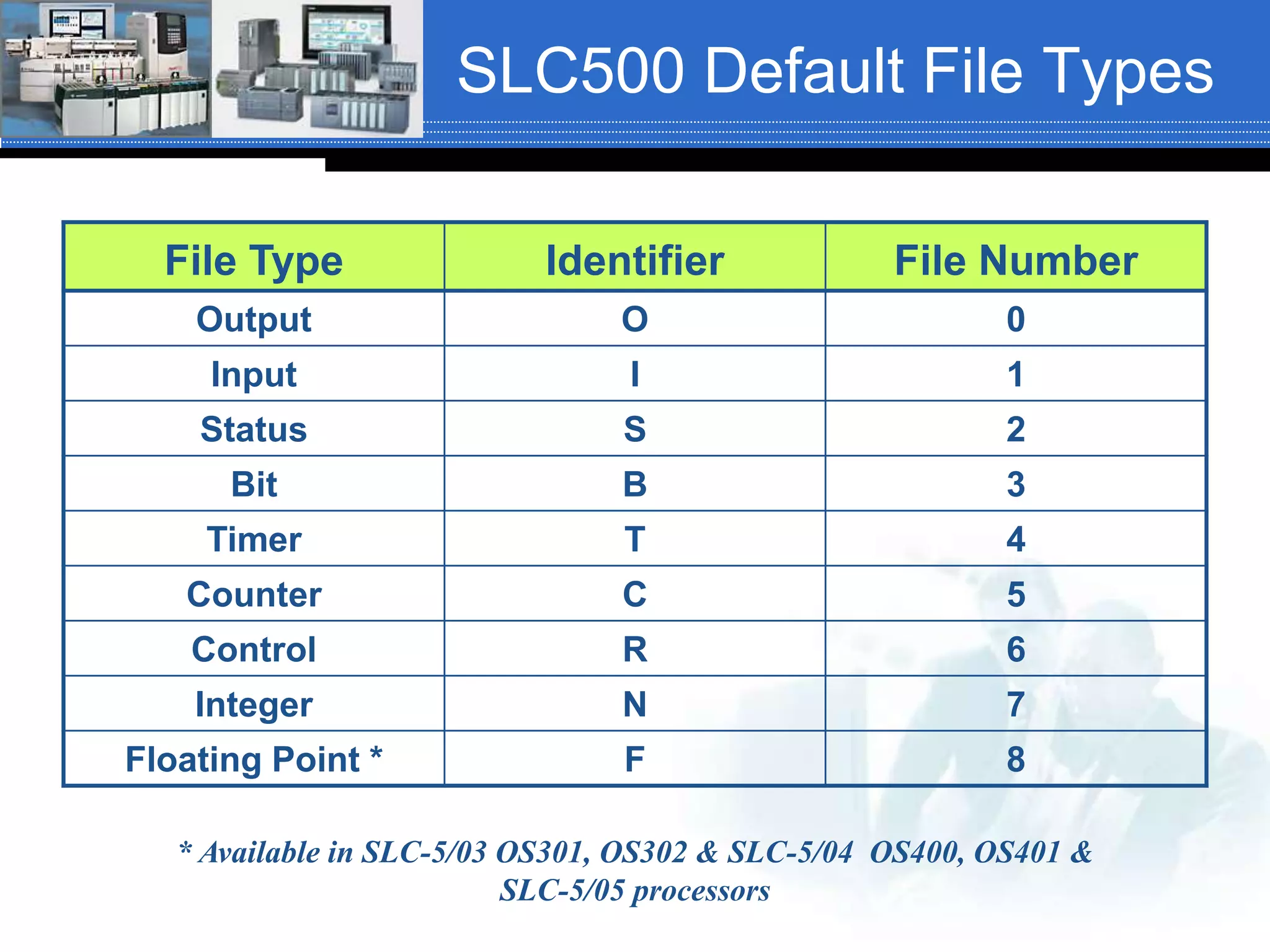

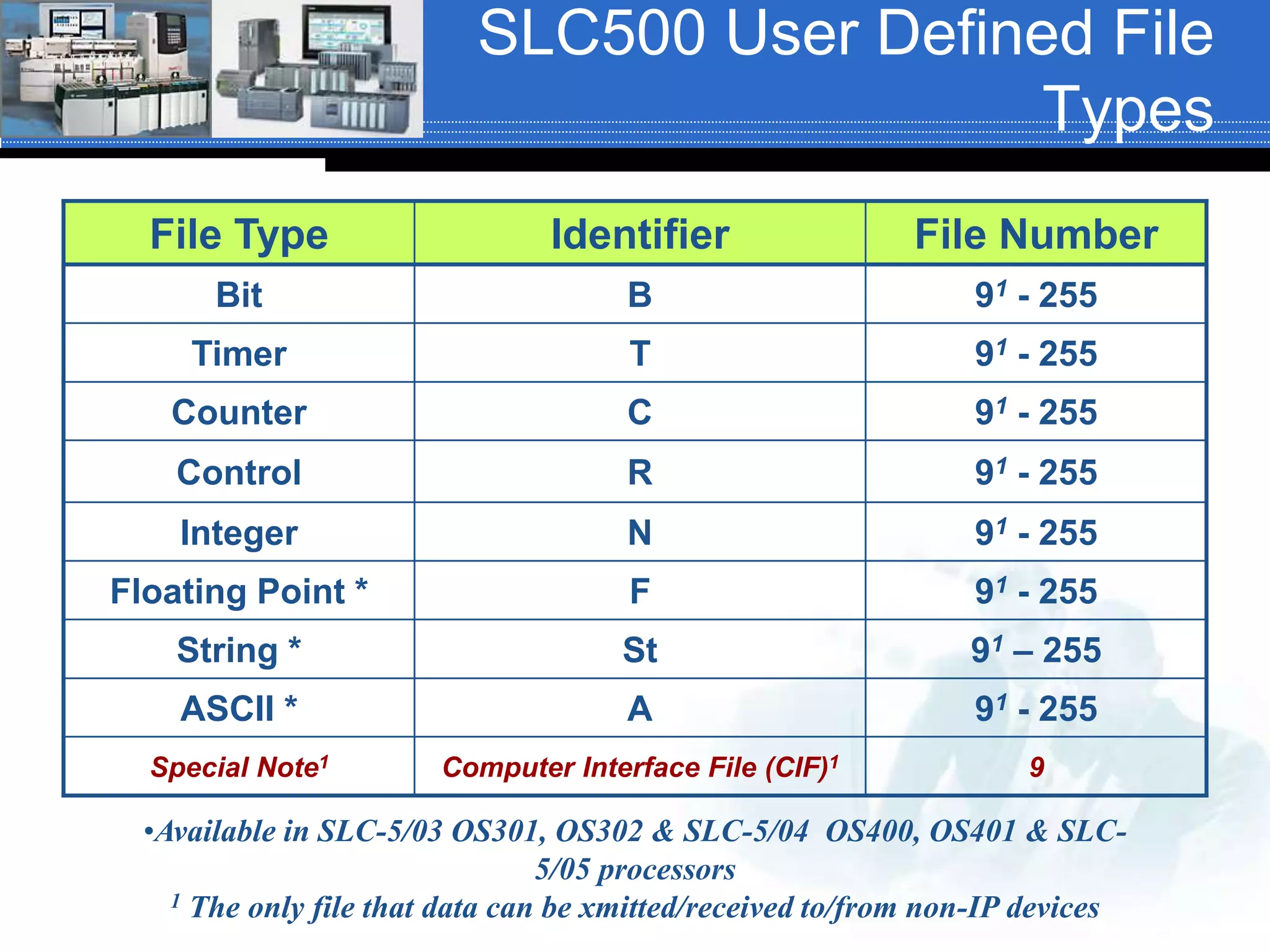

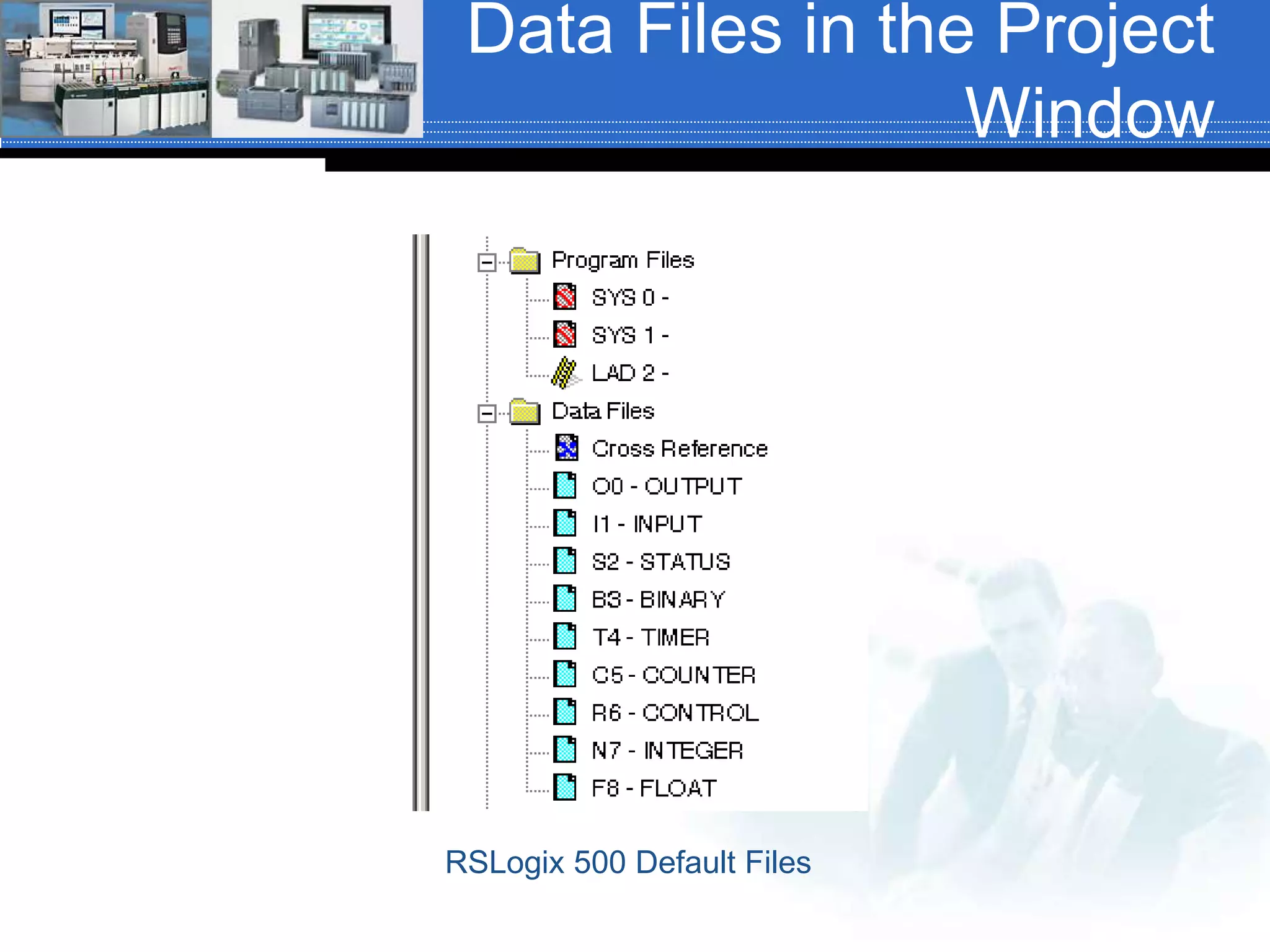

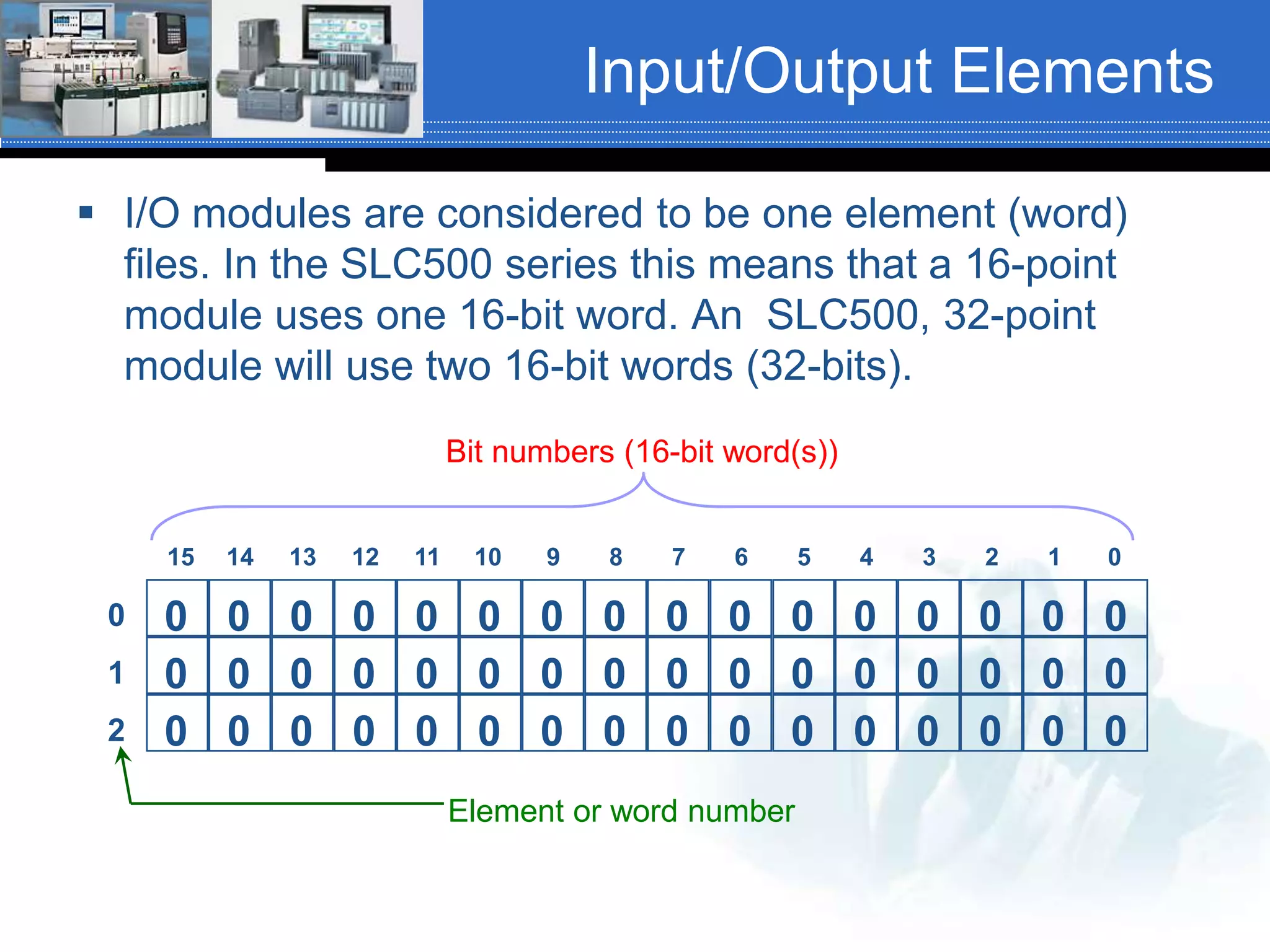

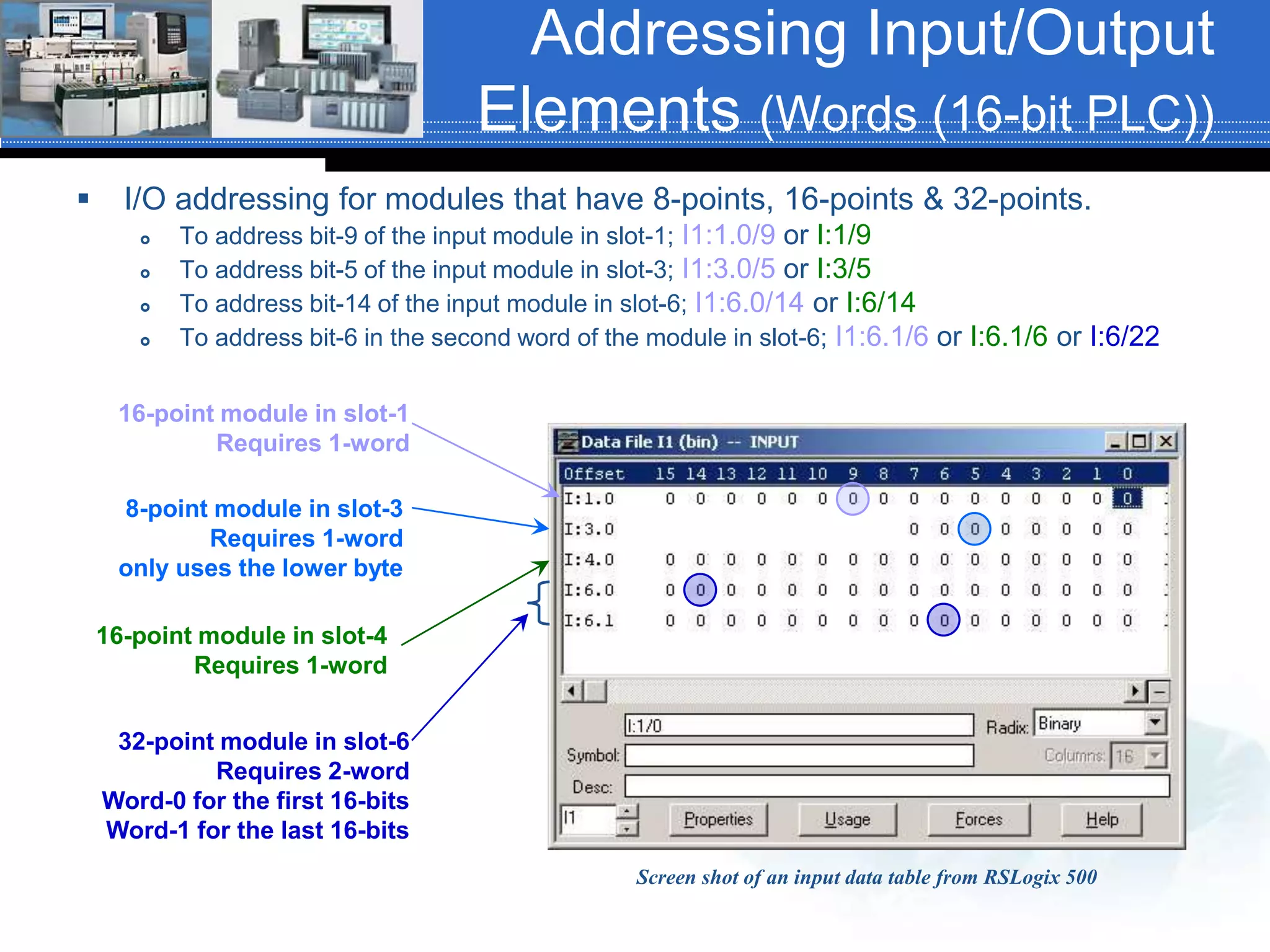

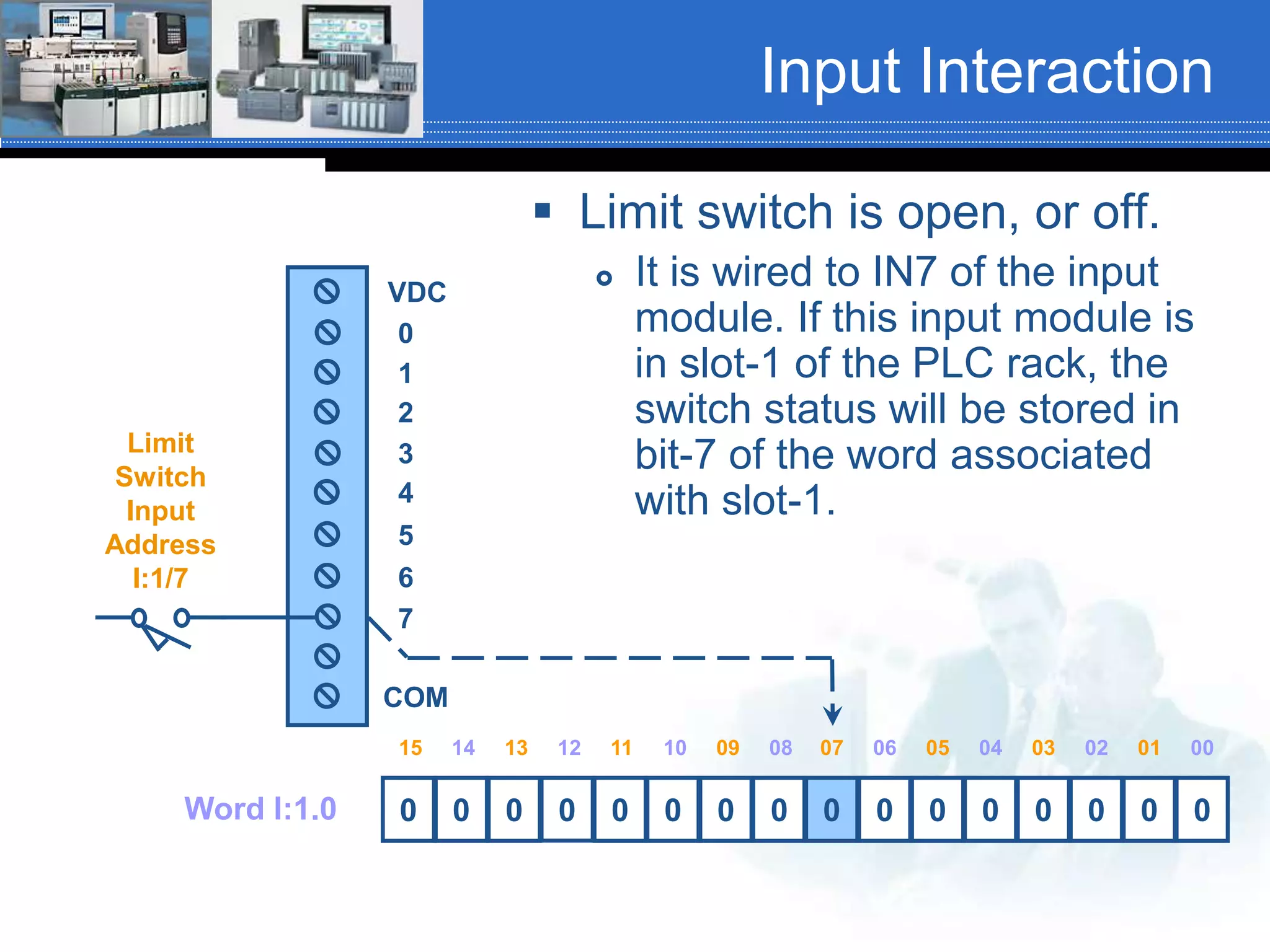

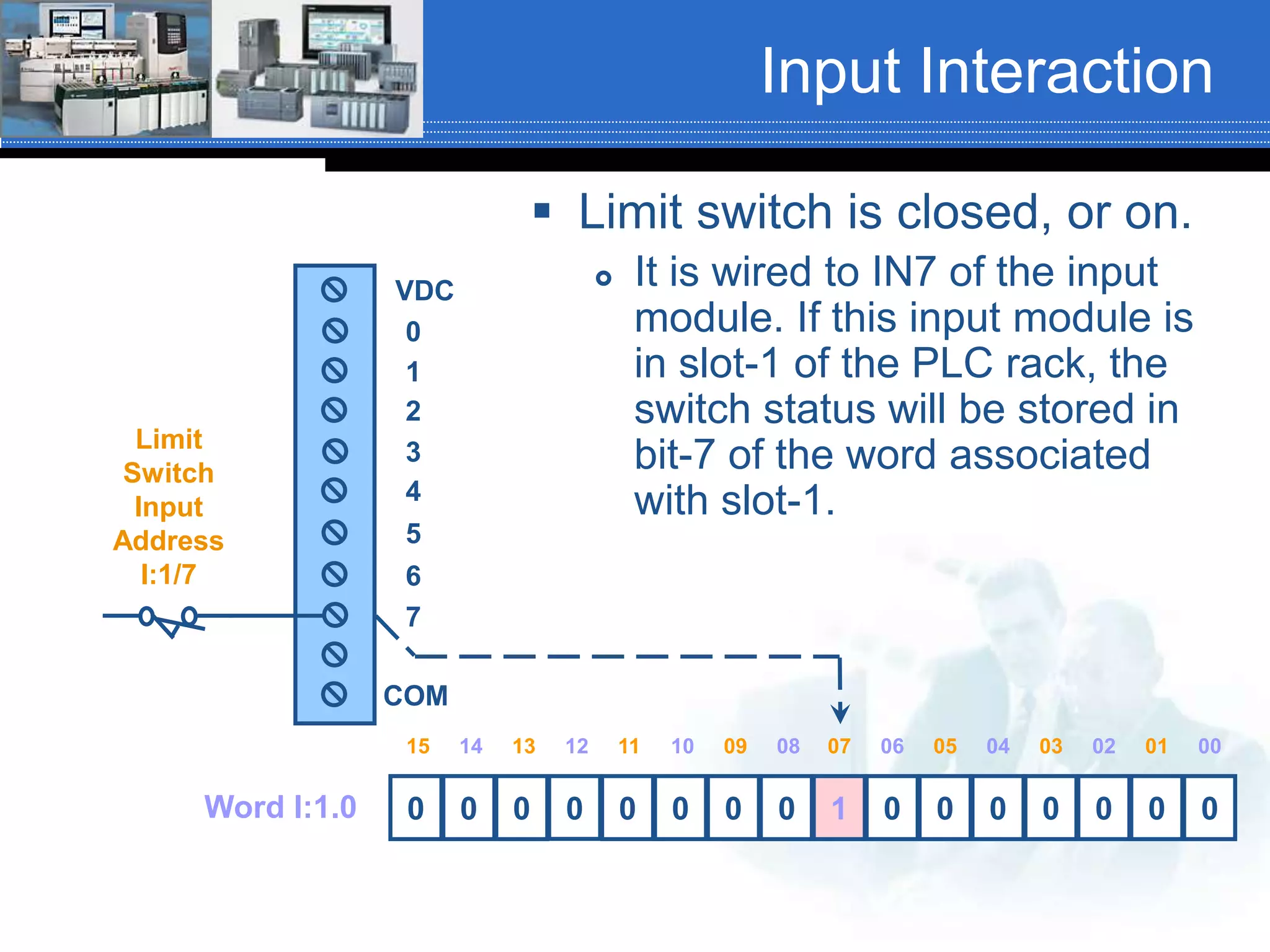

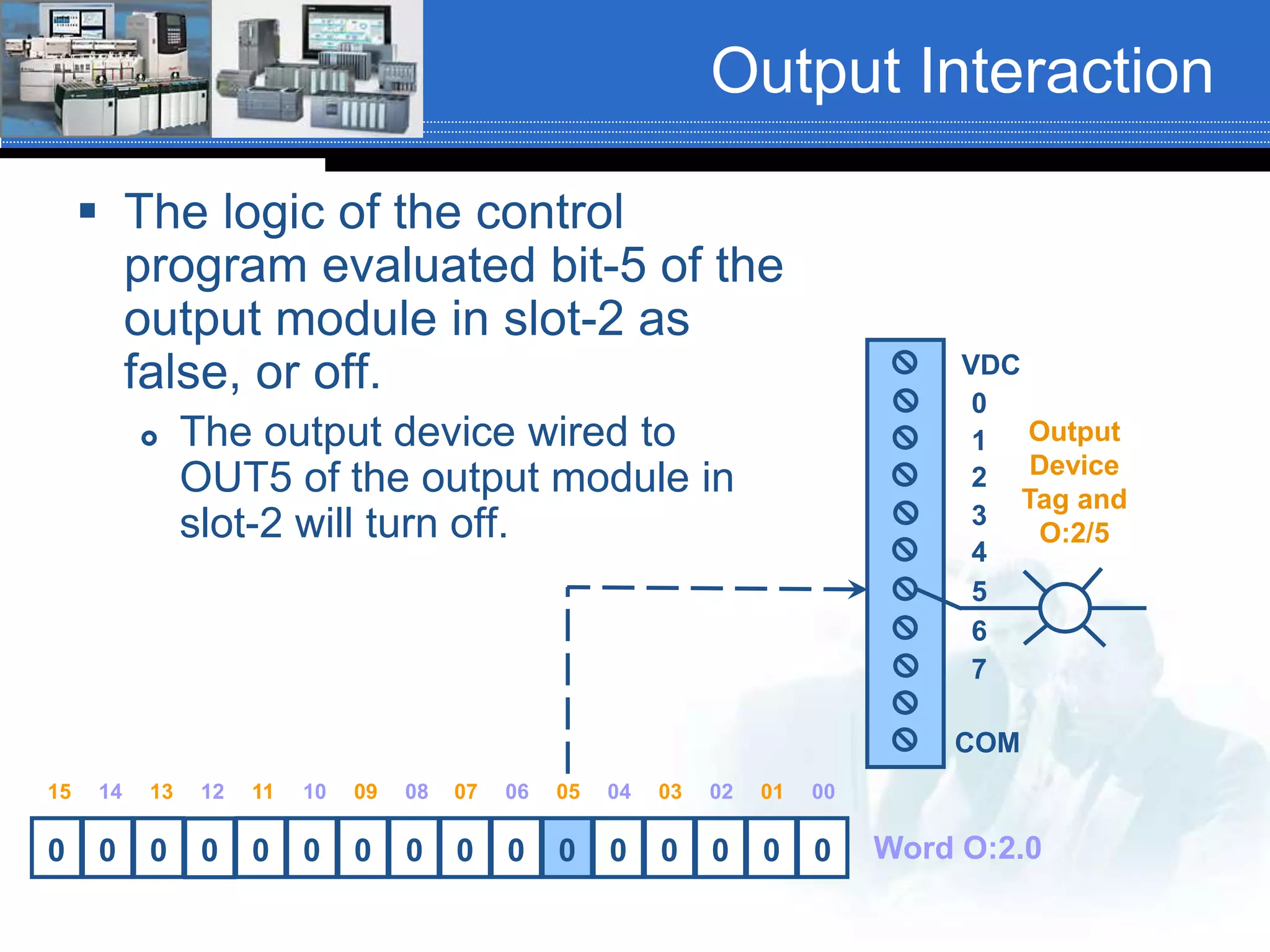

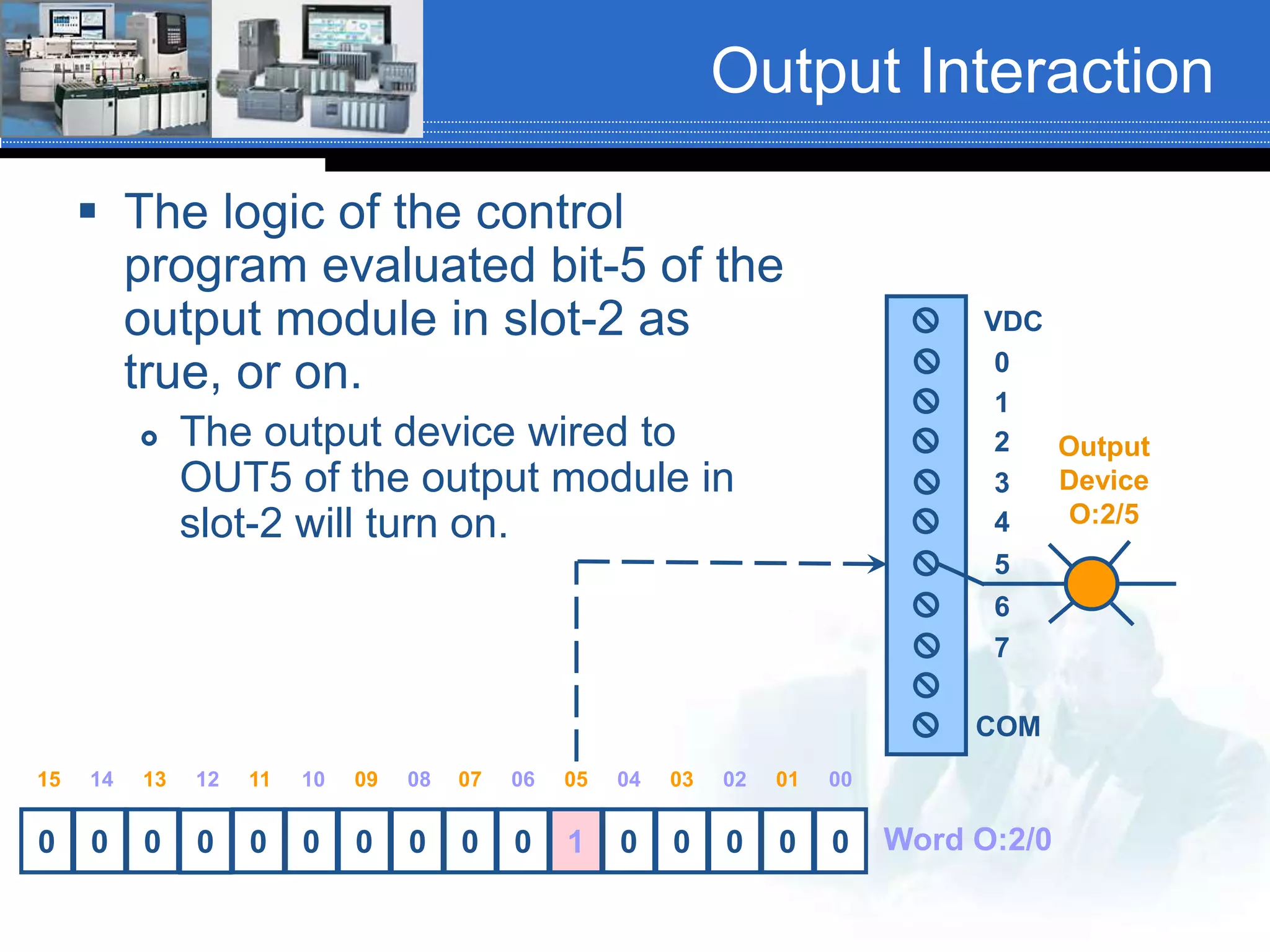

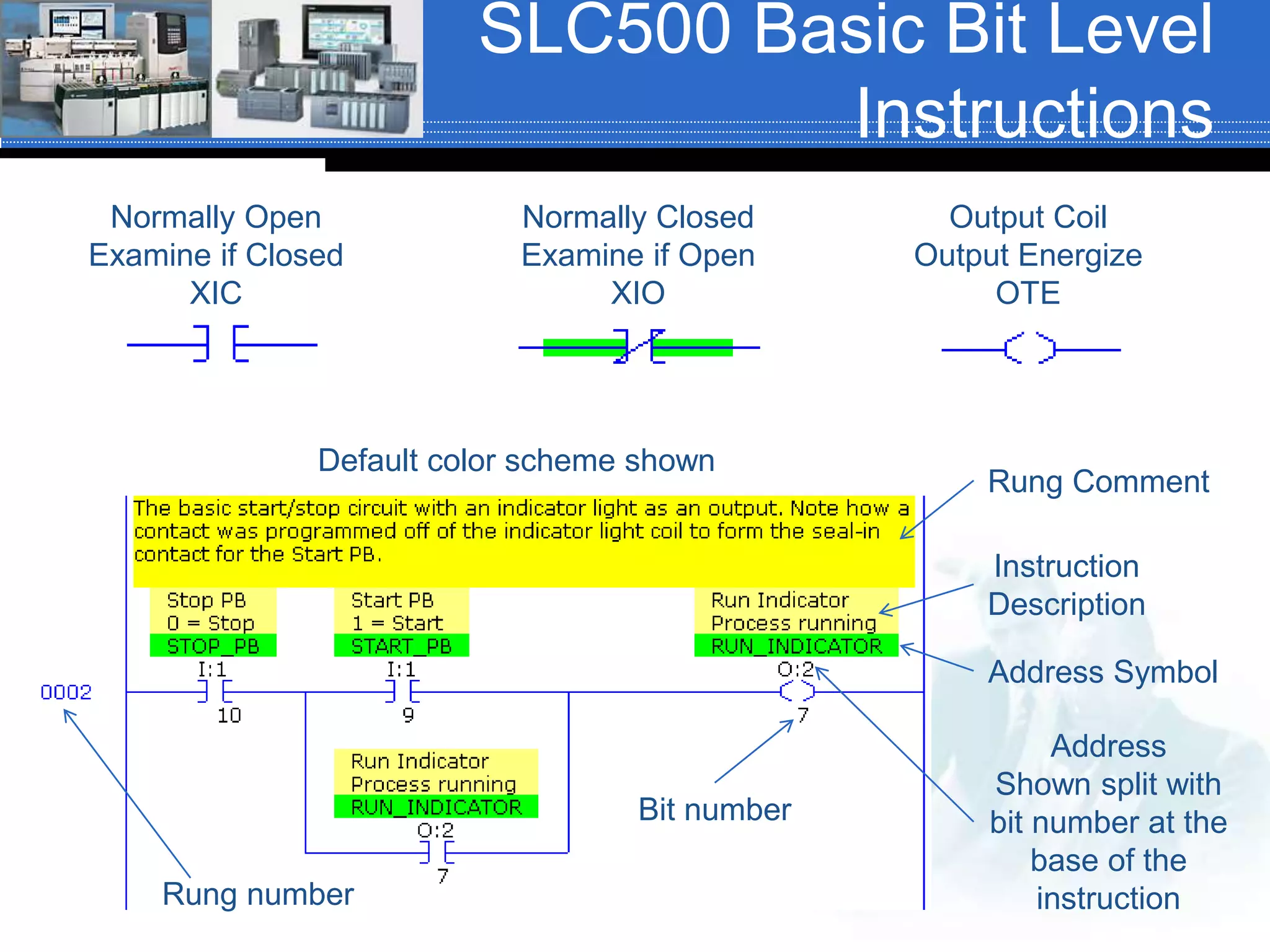

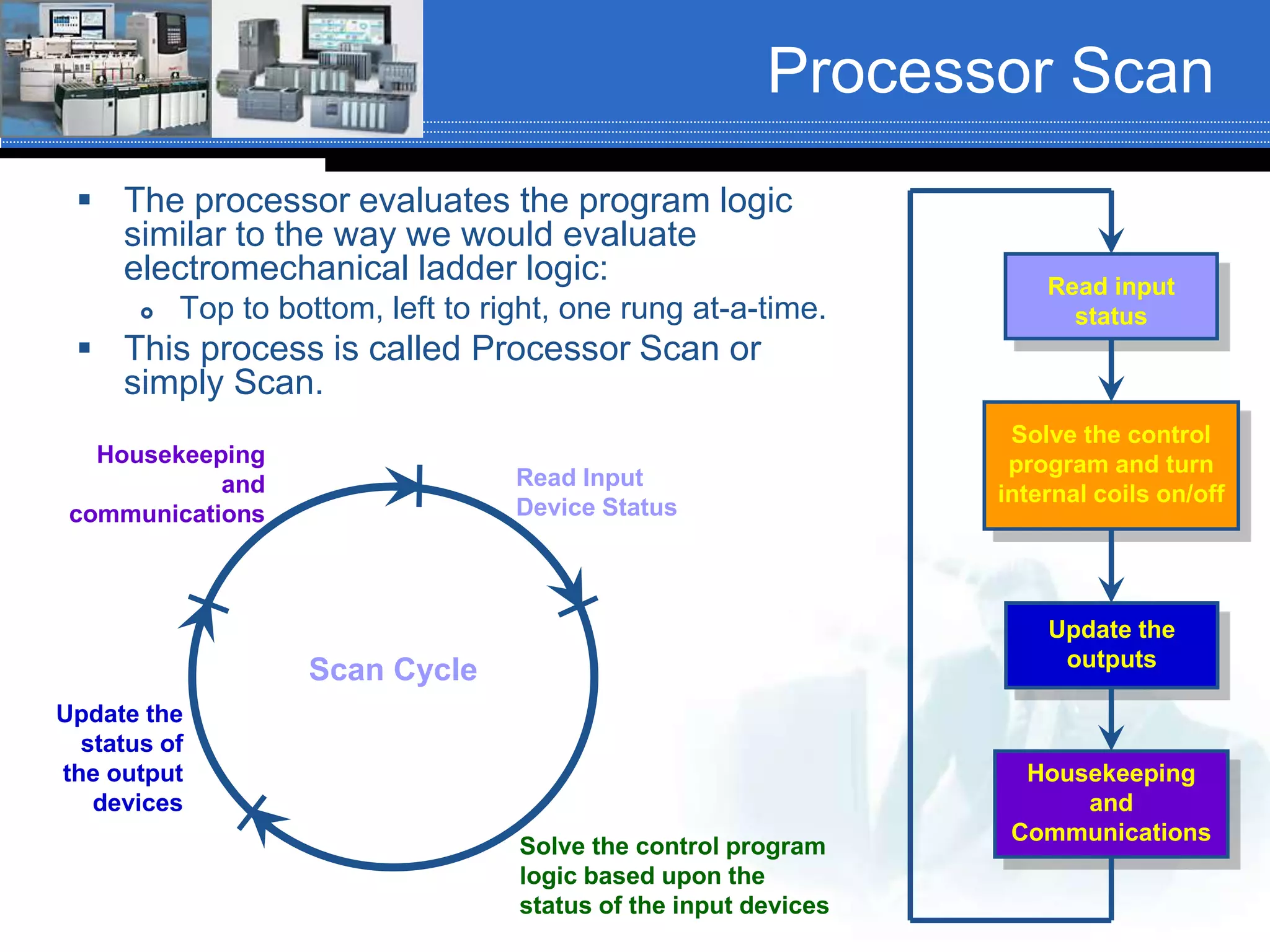

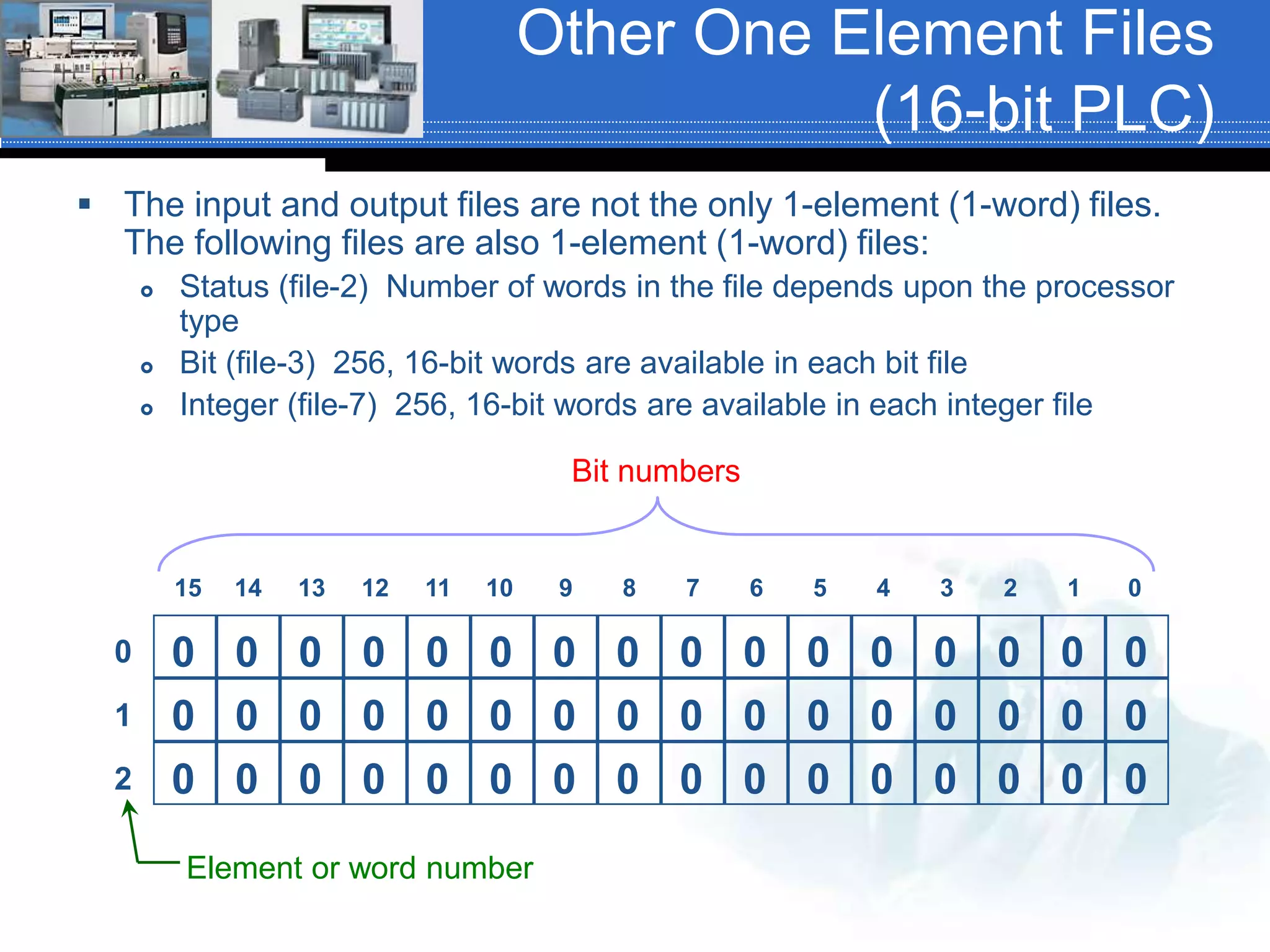

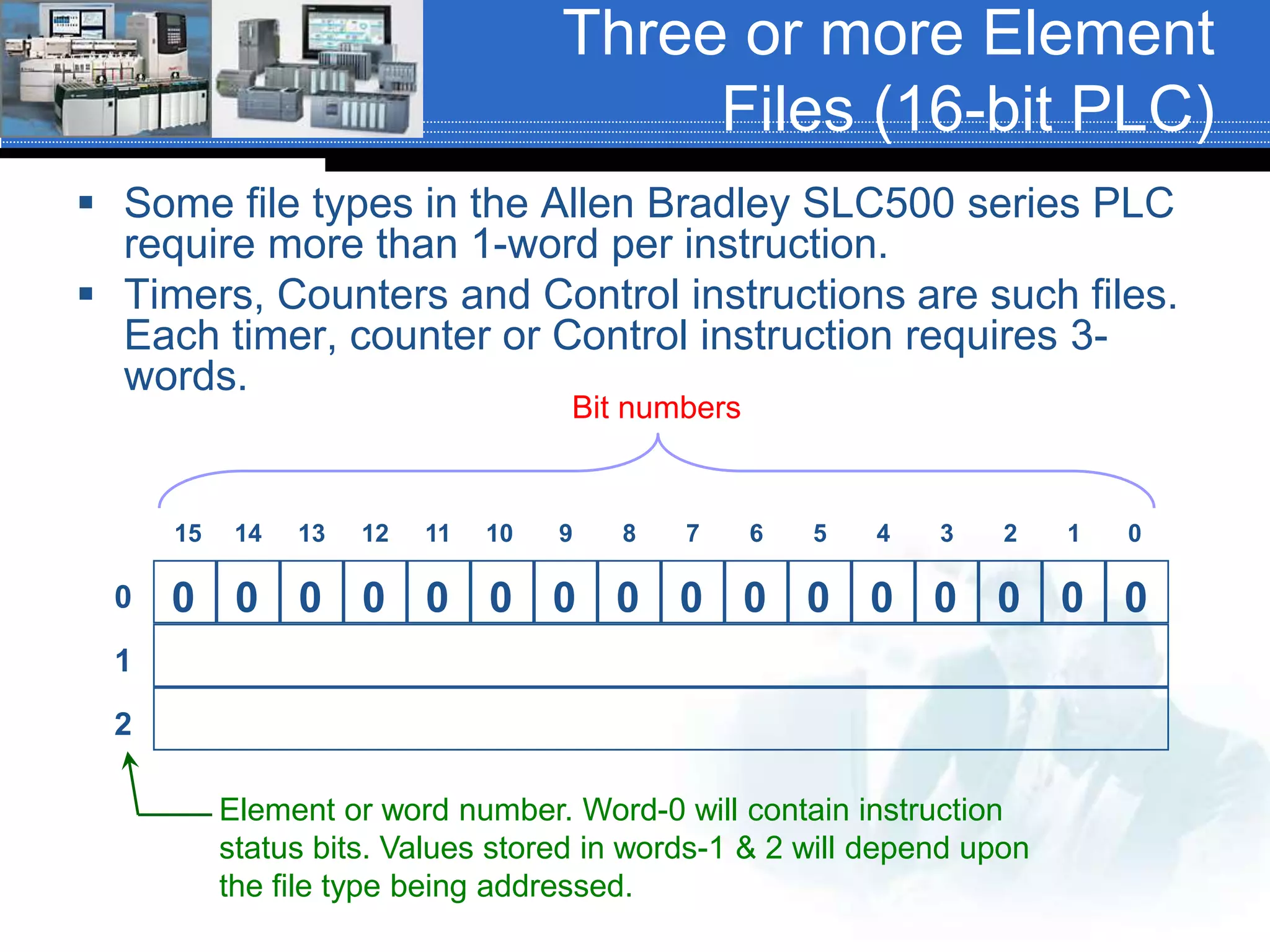

This document discusses memory structure and addressing in programmable logic controllers (PLCs). It describes the different types of memory structures as address-based, tag-based, and a combination. It then focuses on Allen-Bradley SLC500 PLCs which use rack-based, address-based memory. The document explains how the PLC program memory stores ladder logic instructions and covers addressing schemes for input/output modules and internal memory types like bits, timers and counters. Input and output interactions with physical devices are demonstrated through examples.