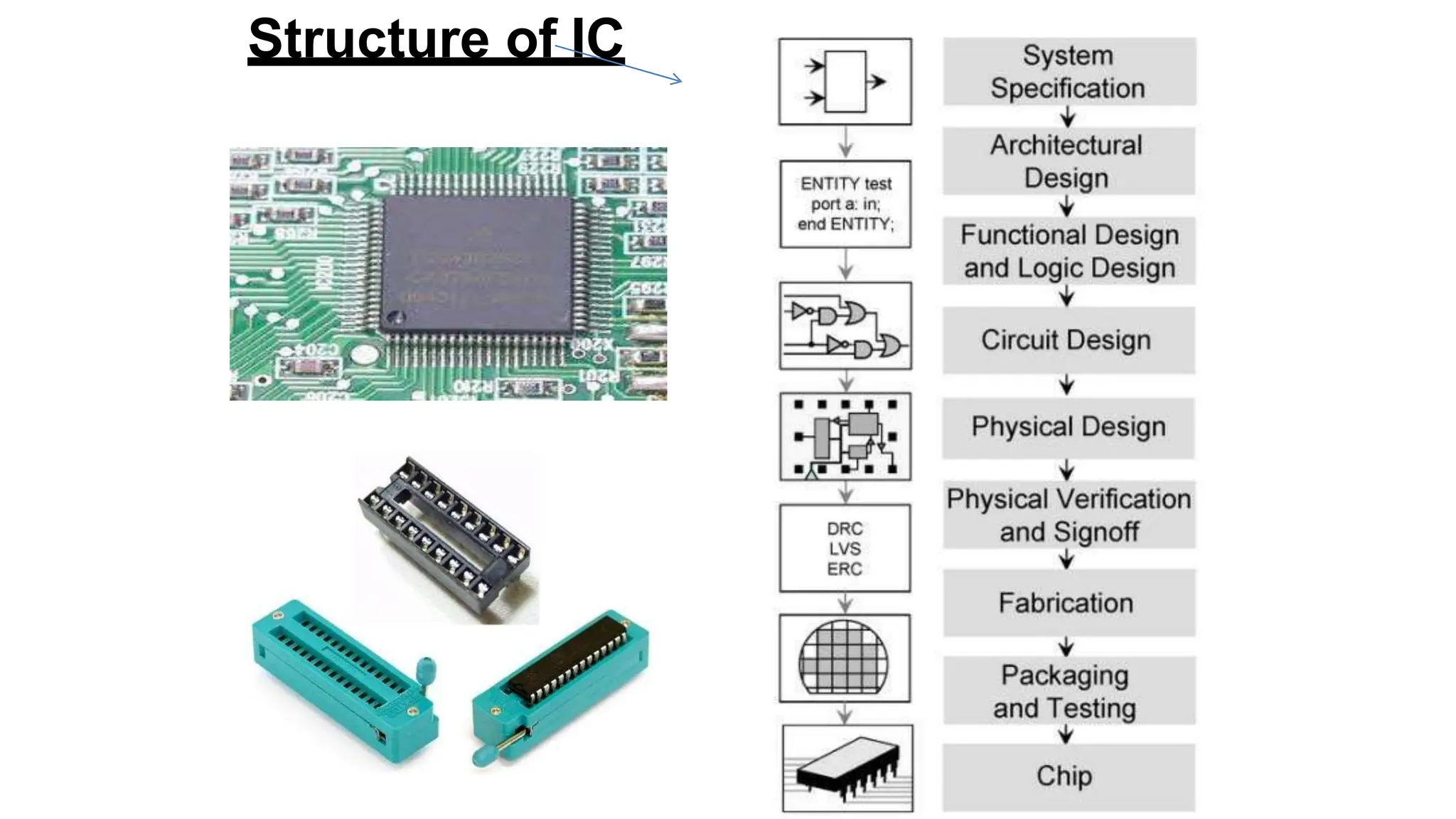

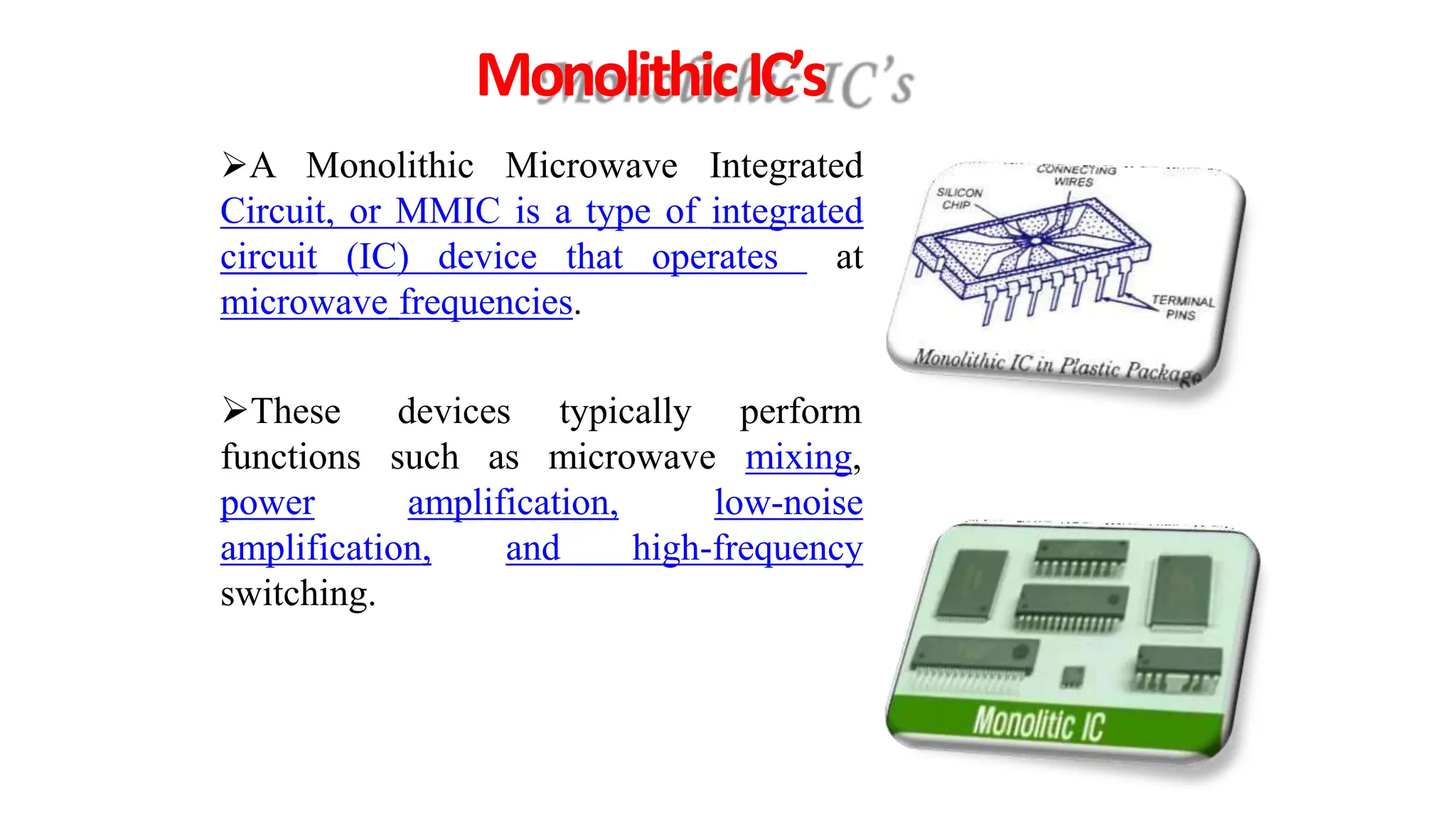

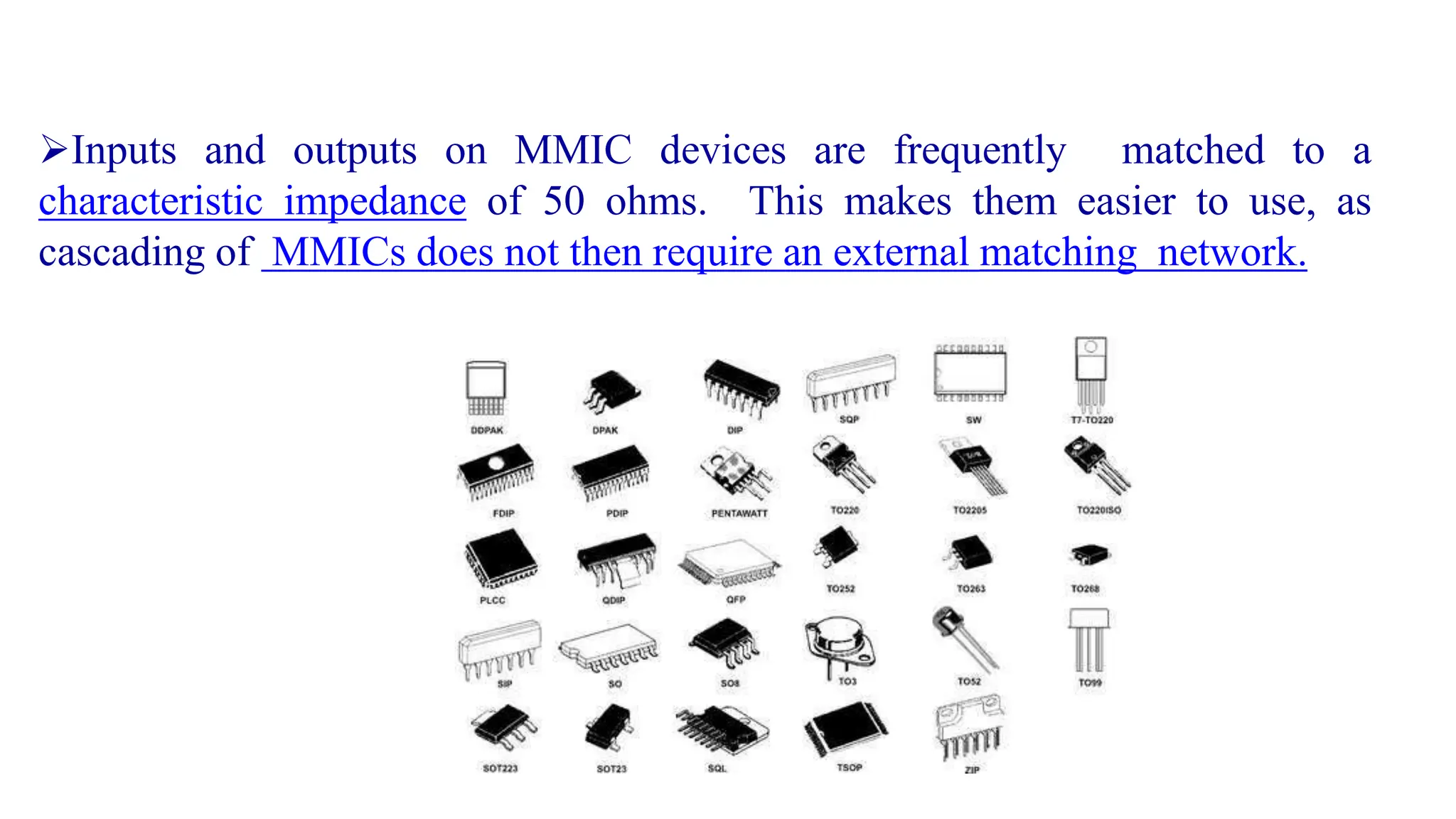

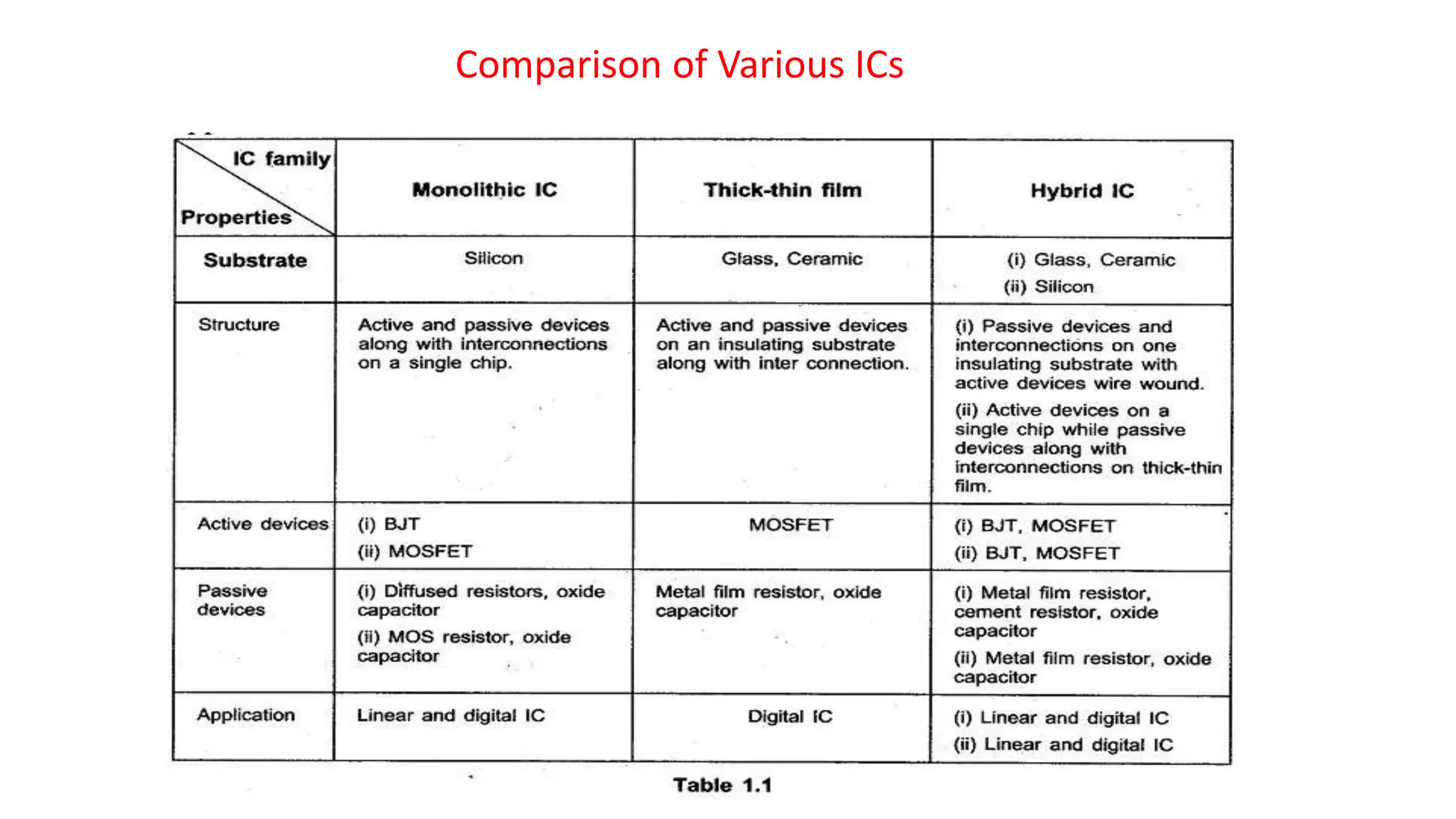

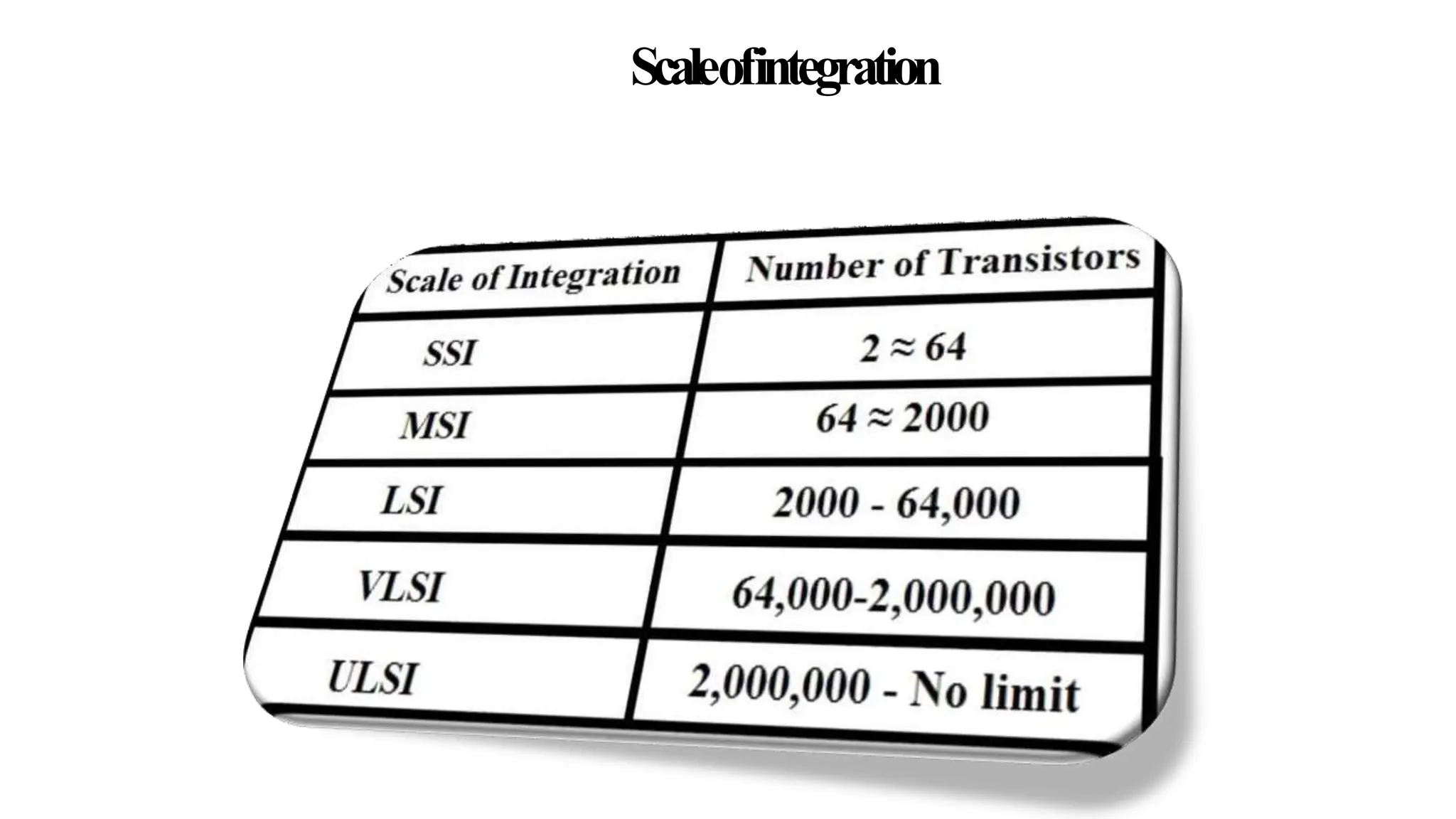

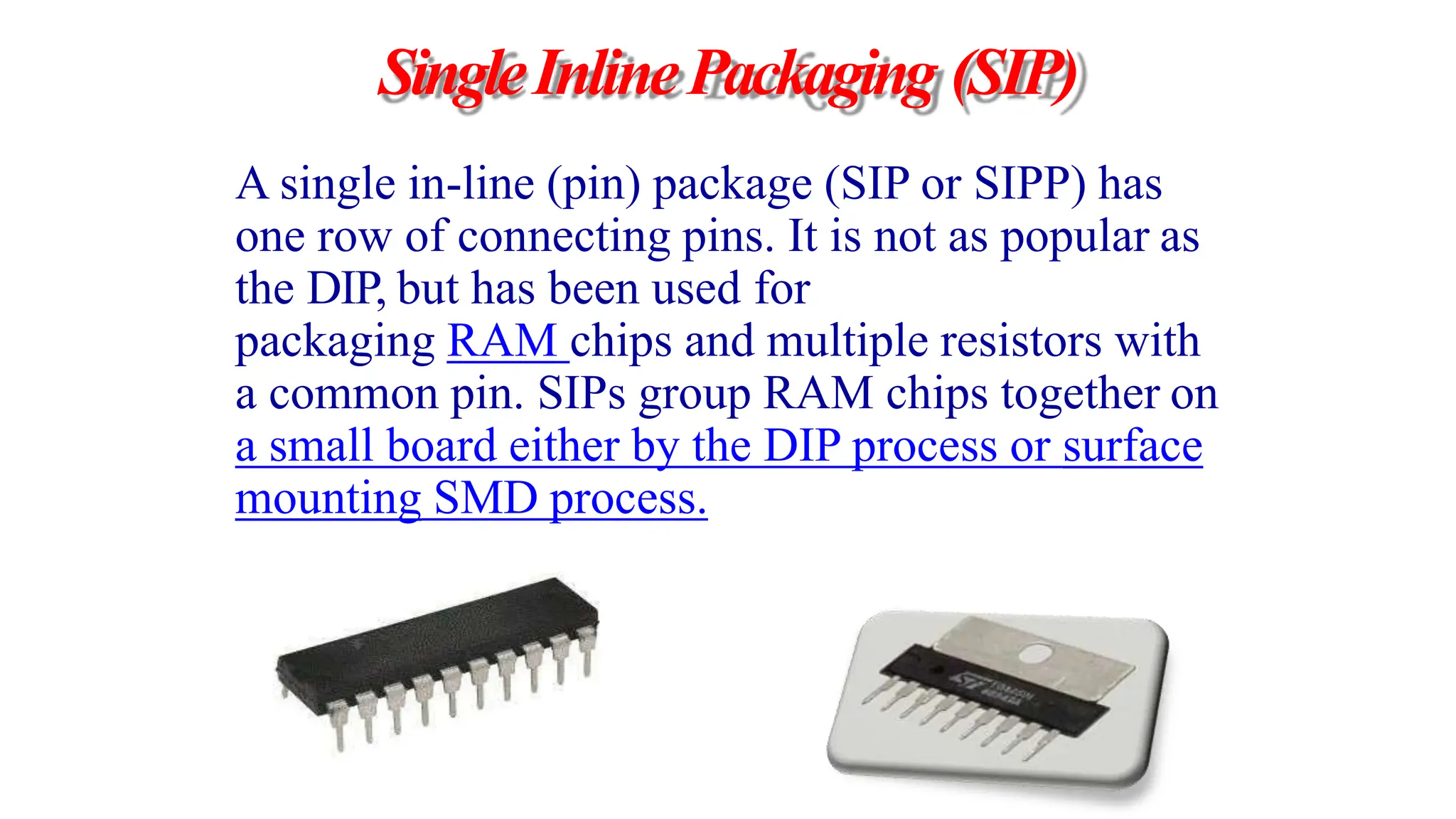

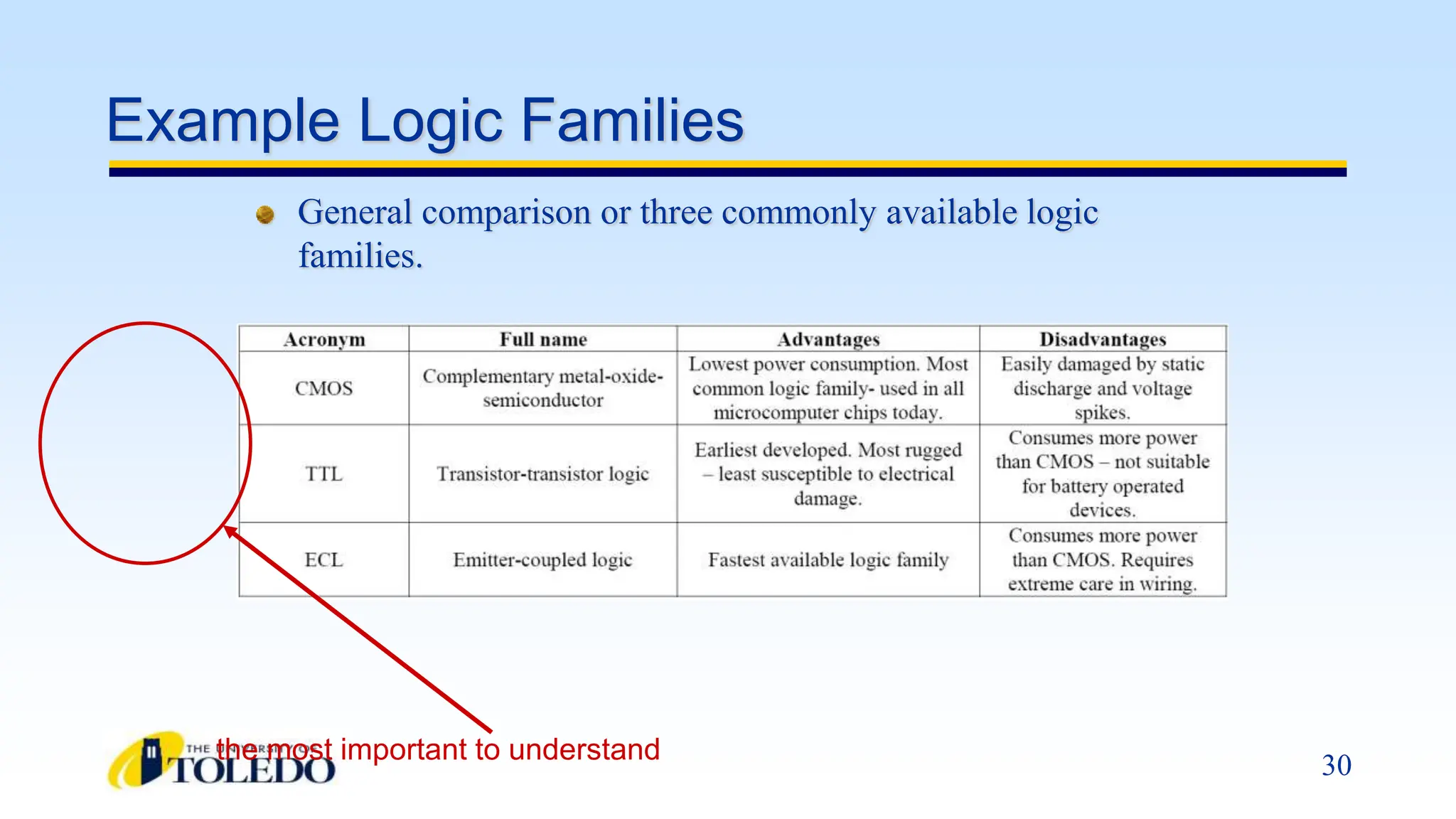

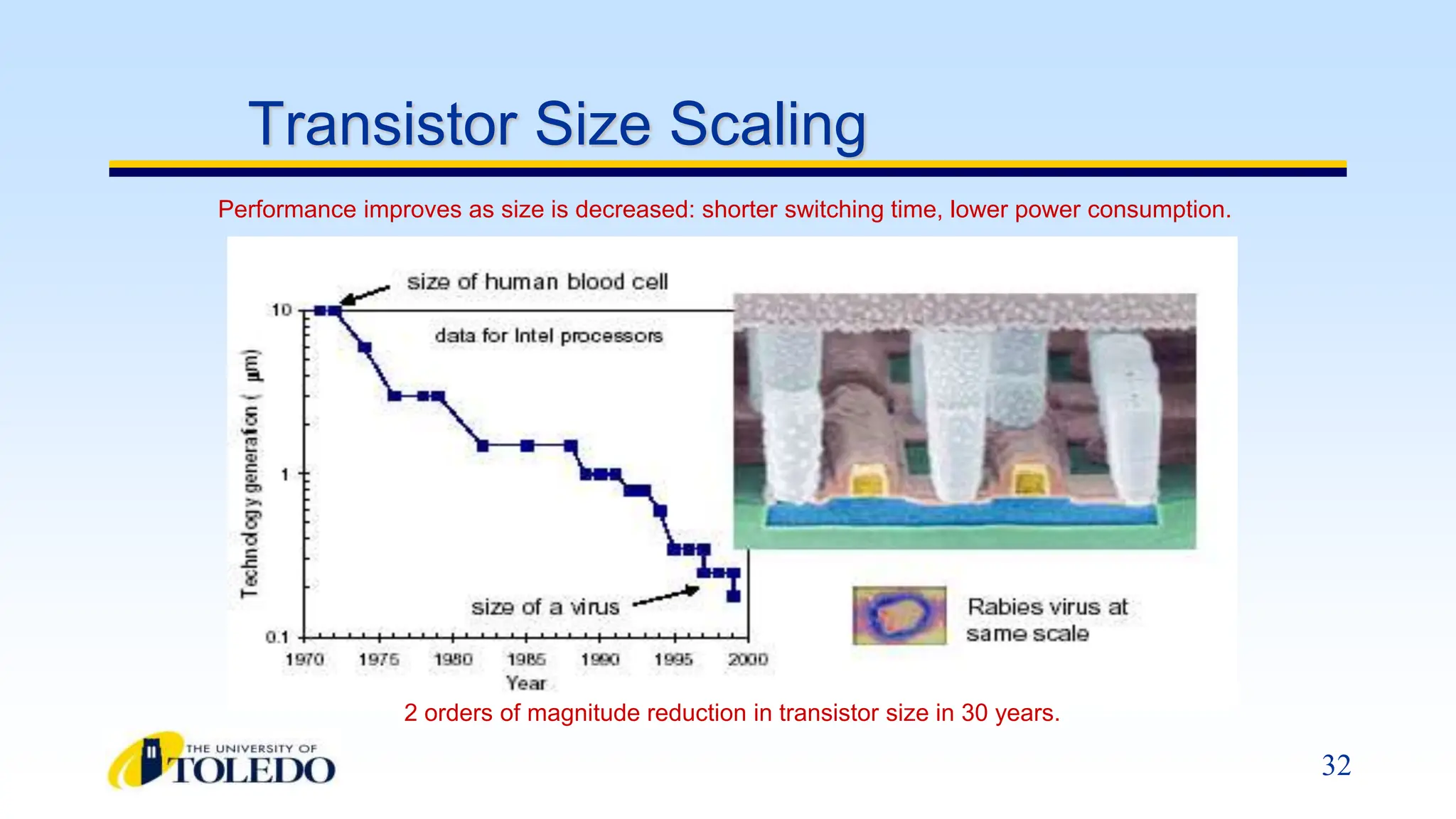

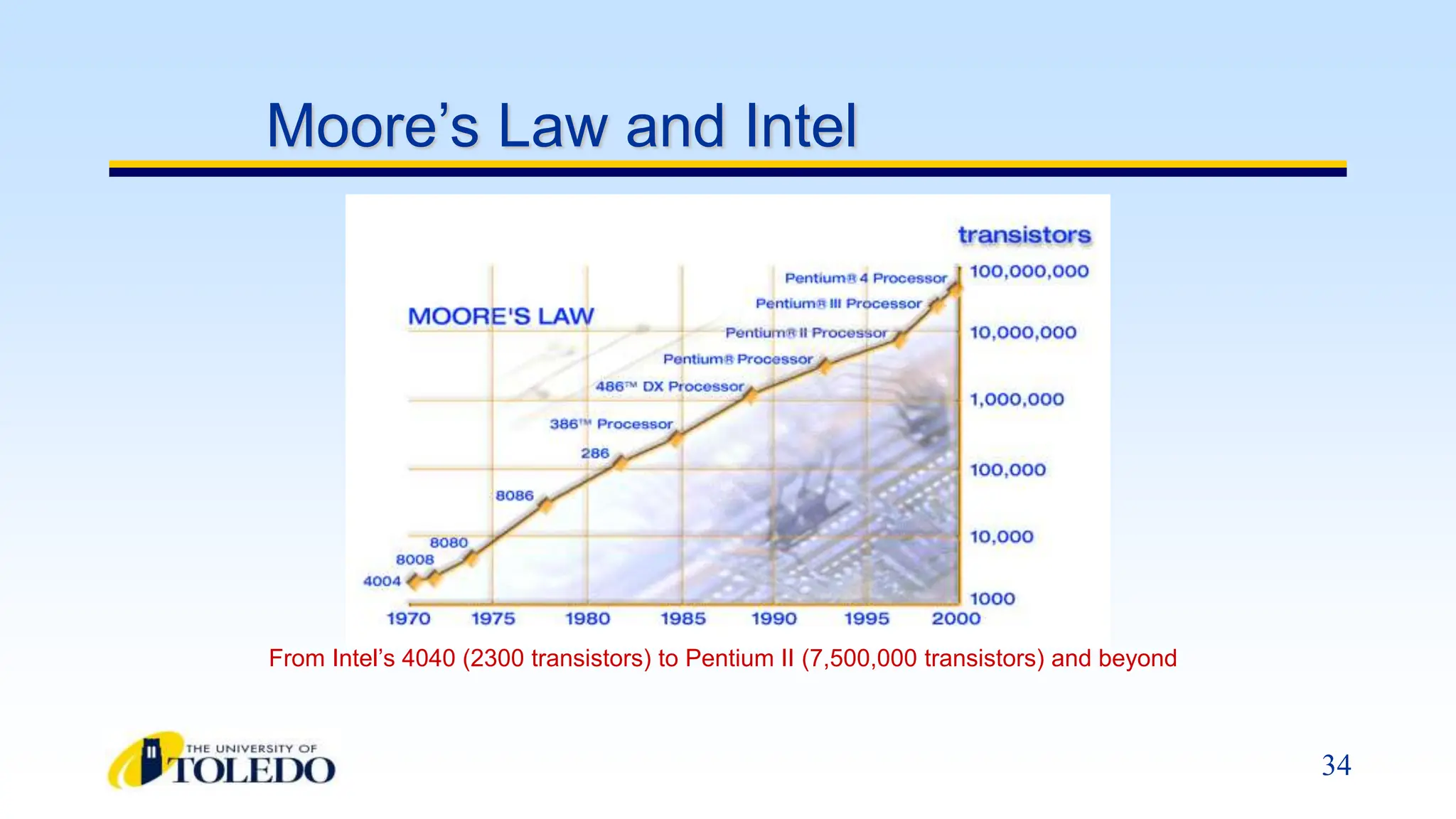

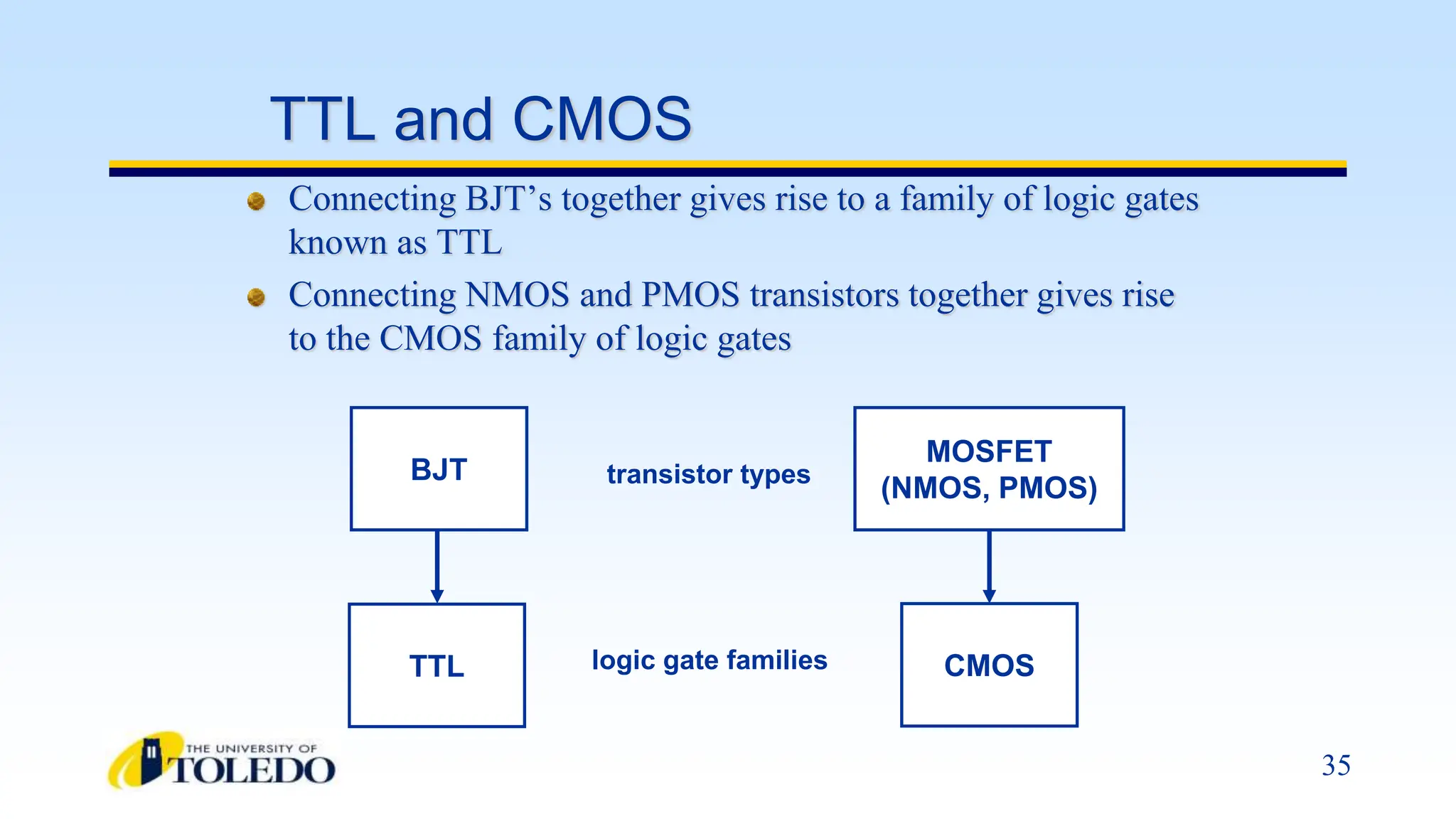

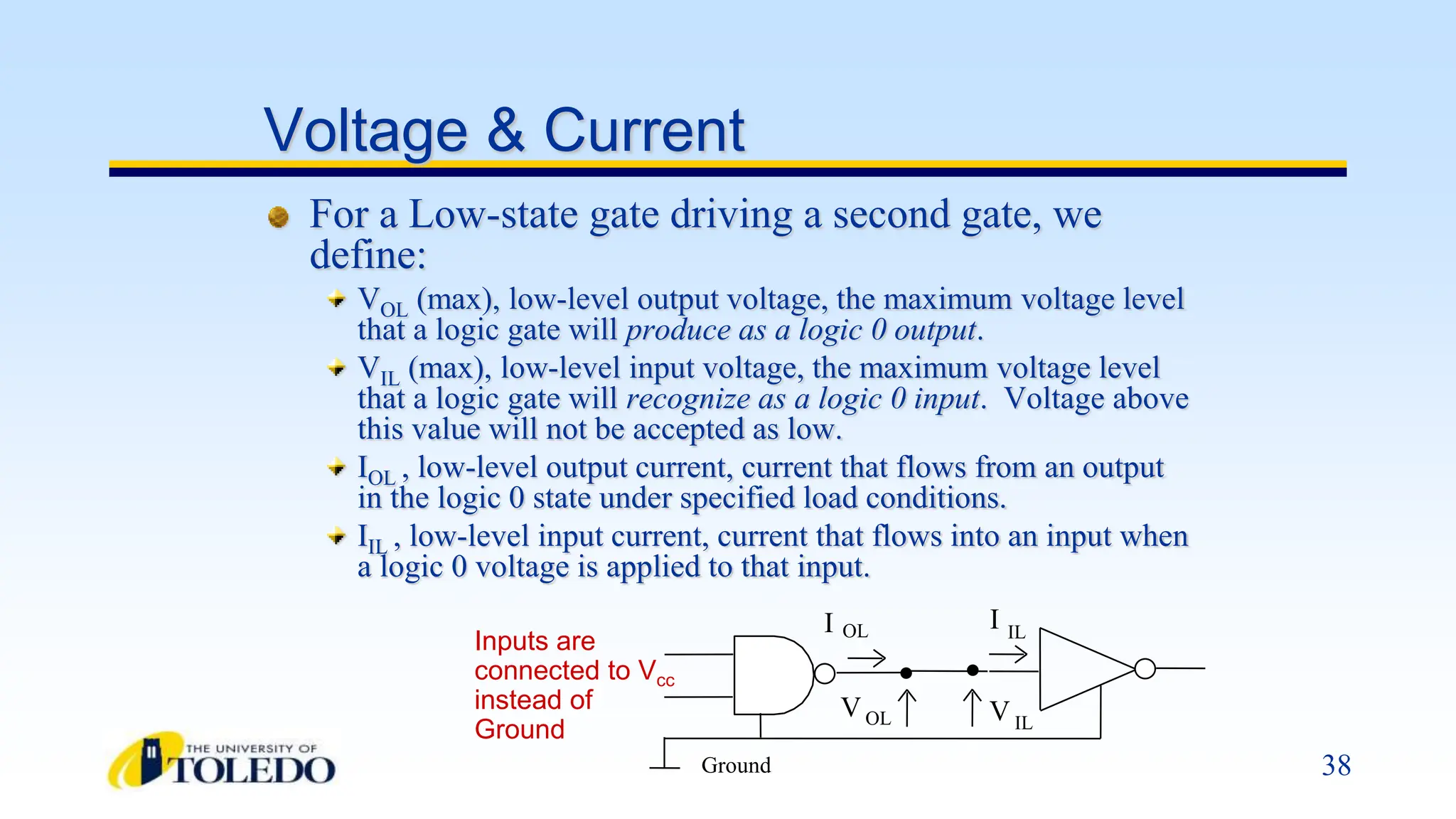

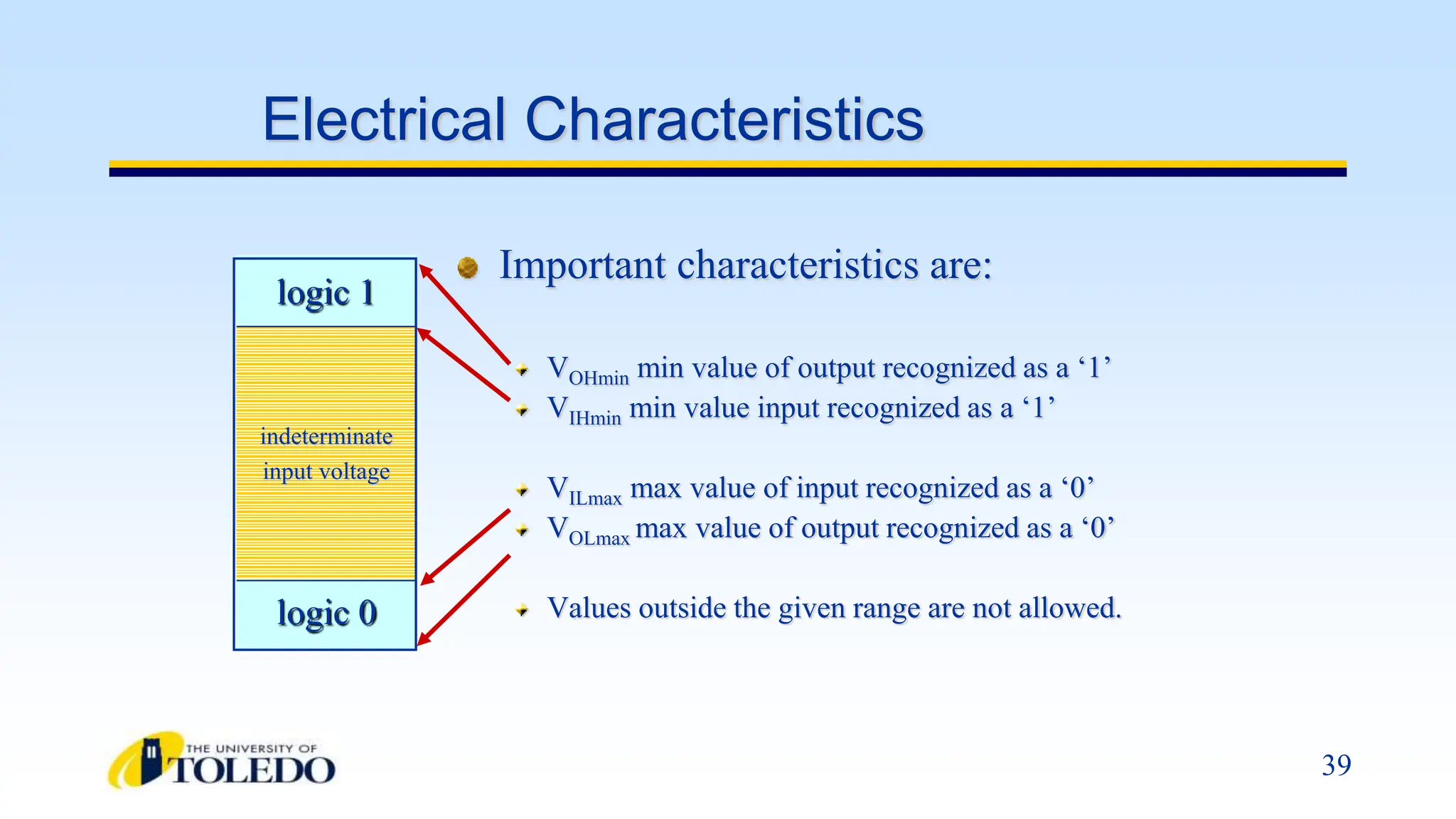

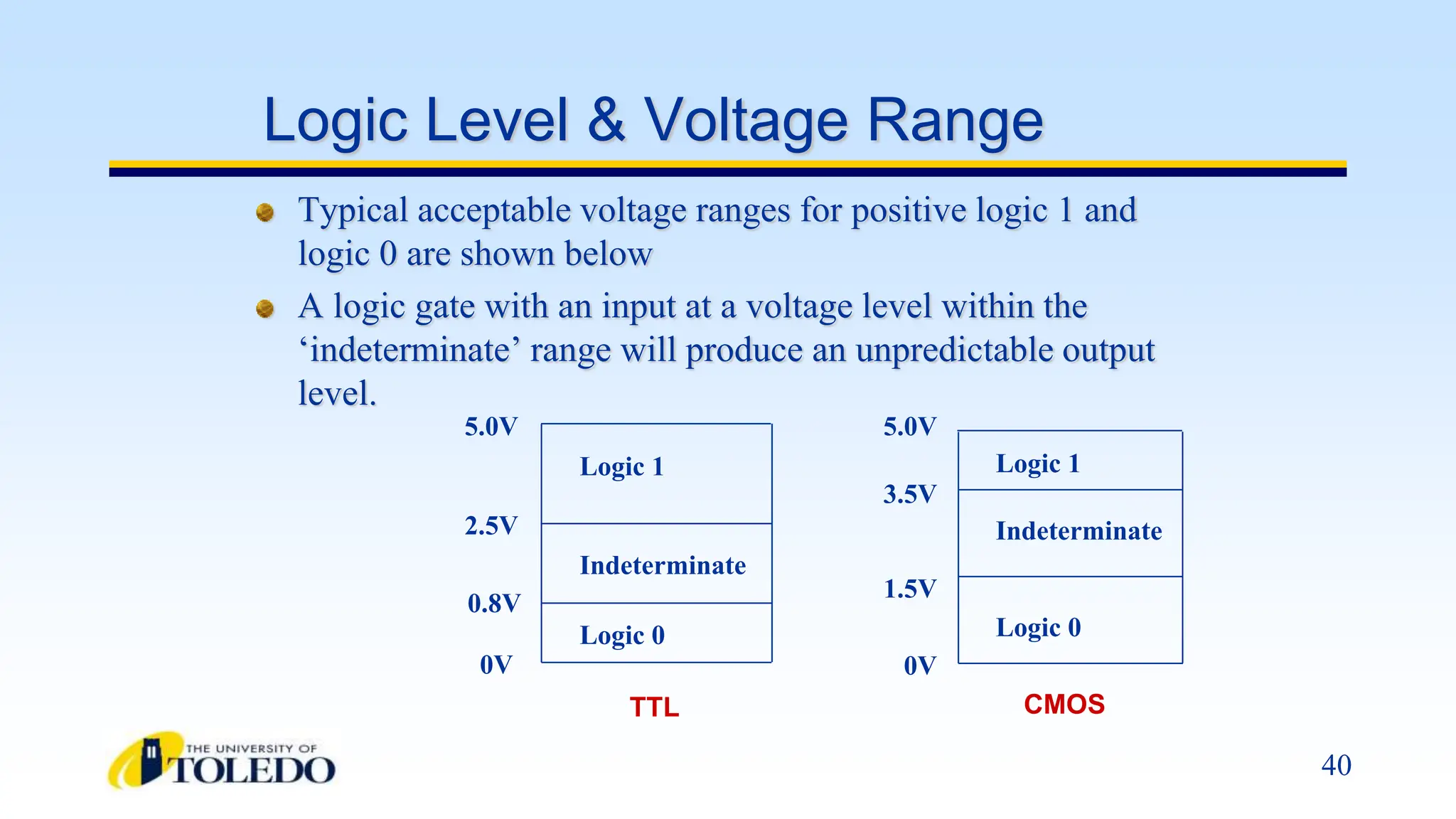

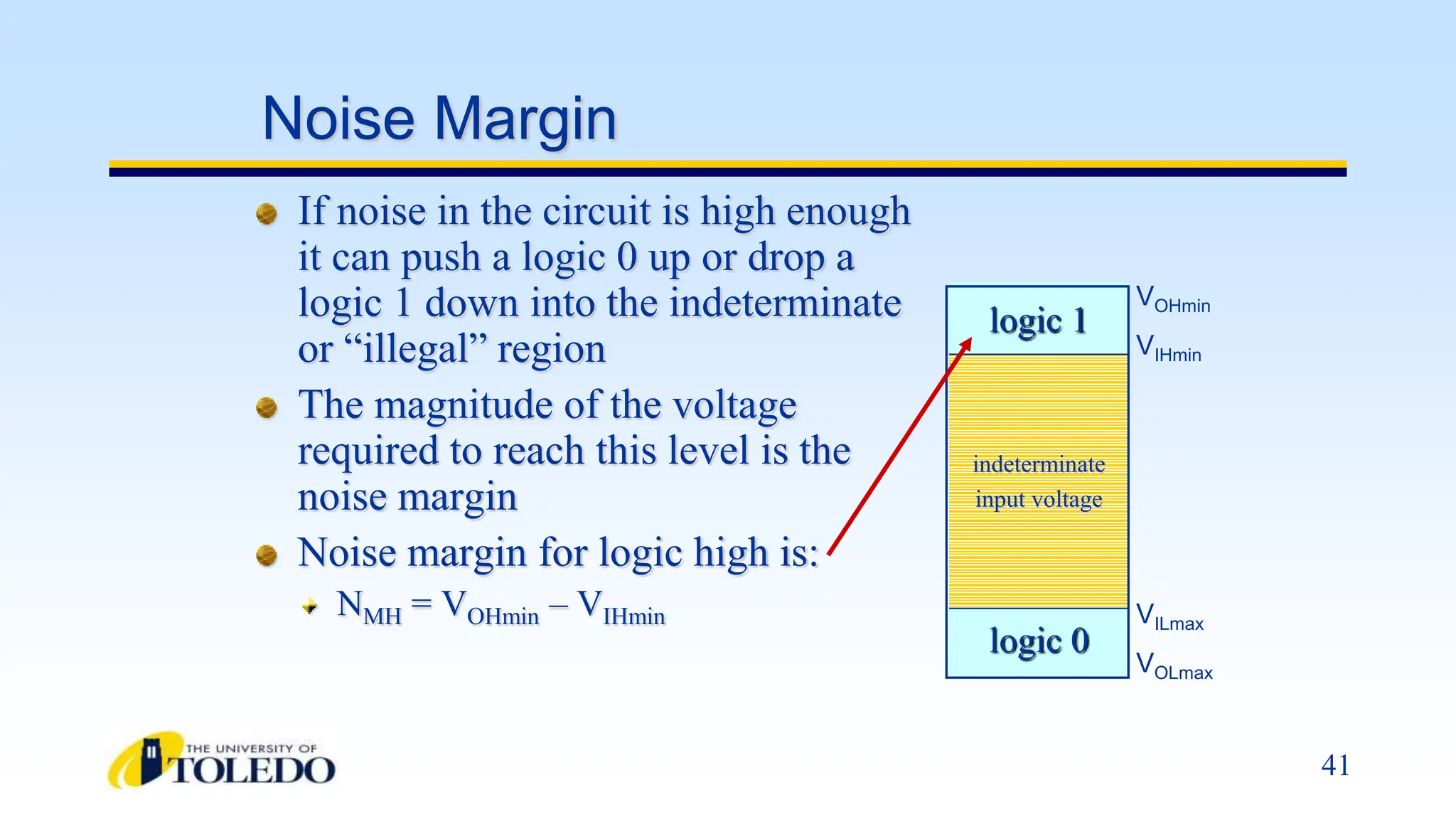

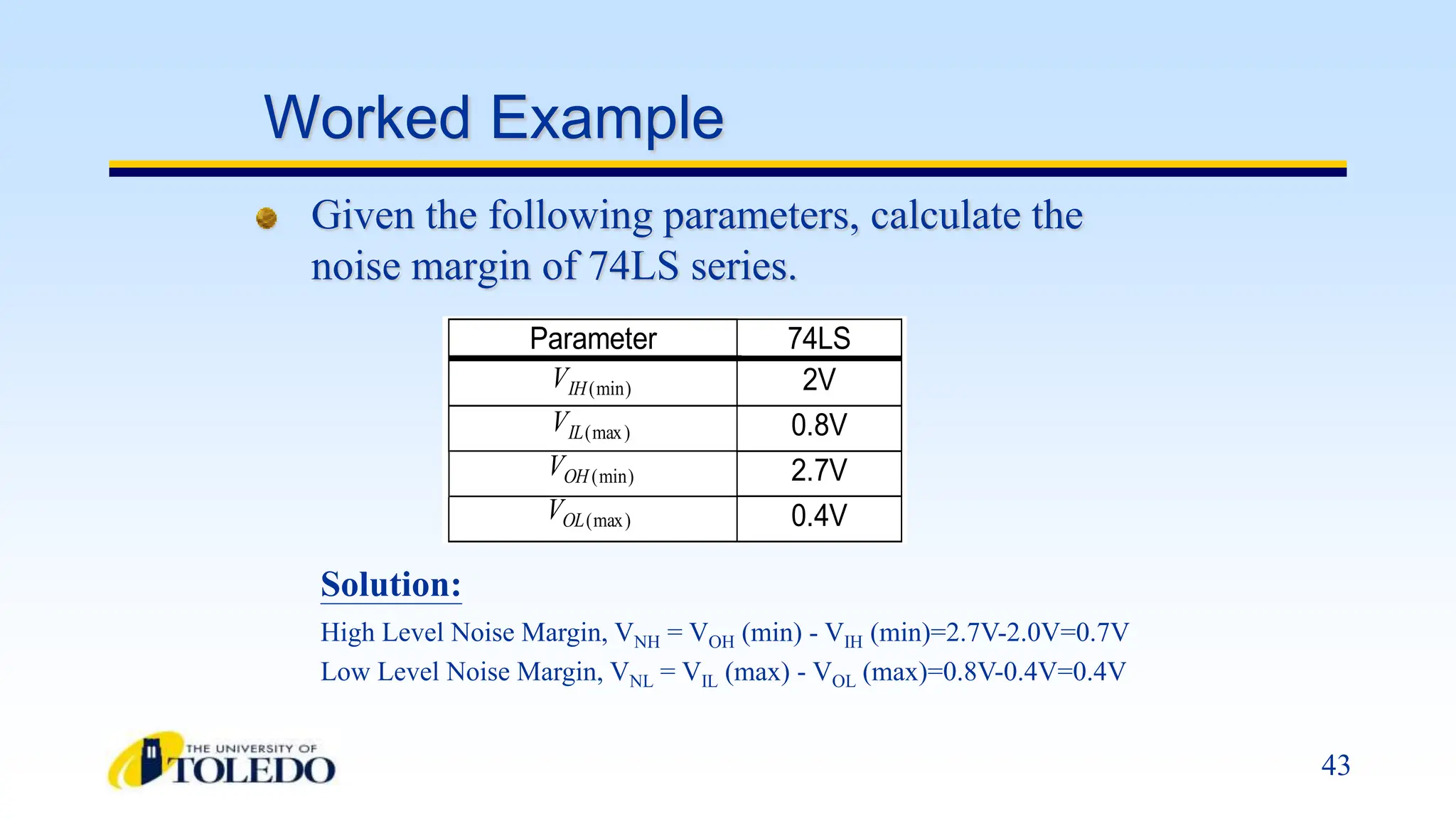

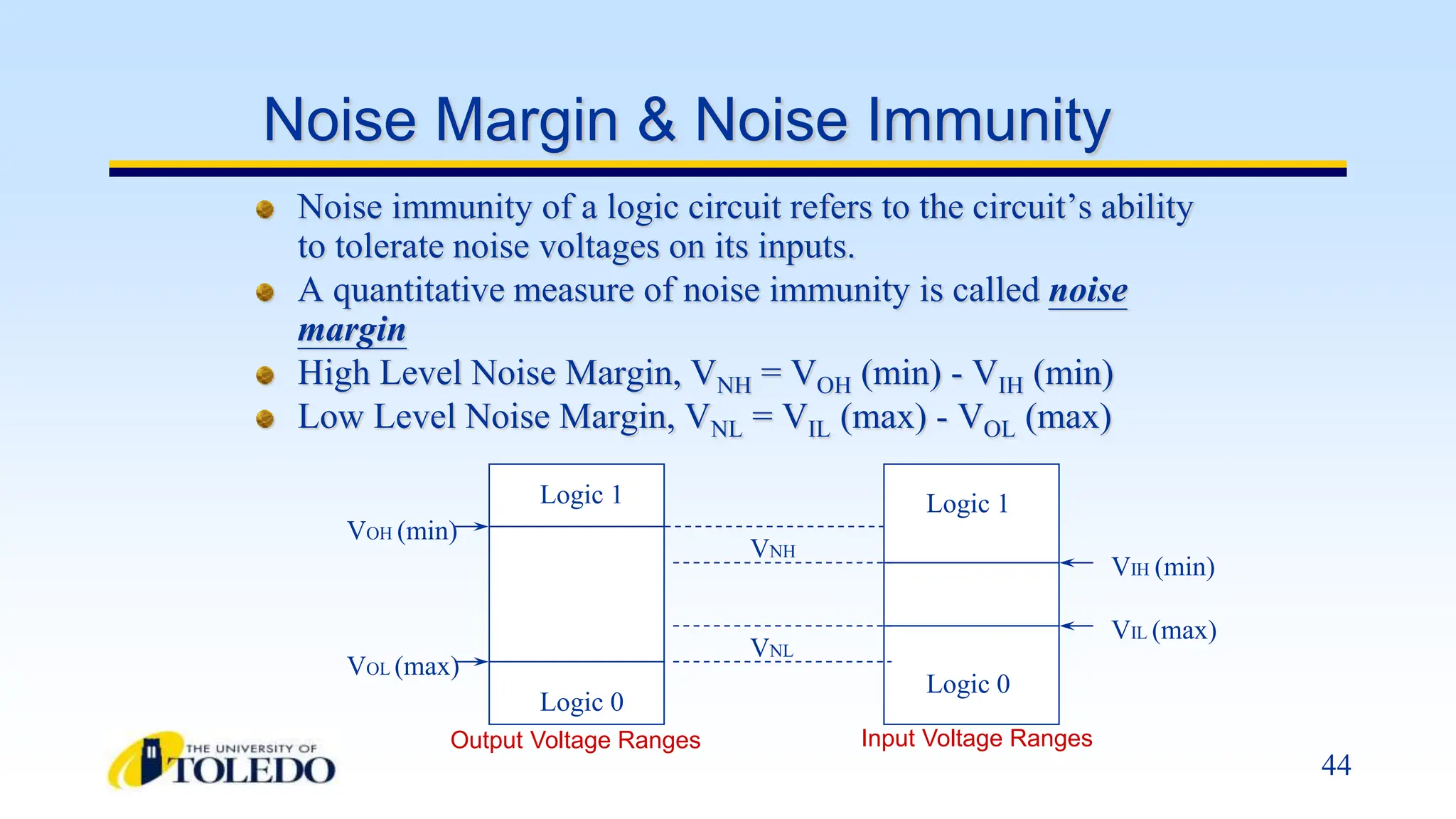

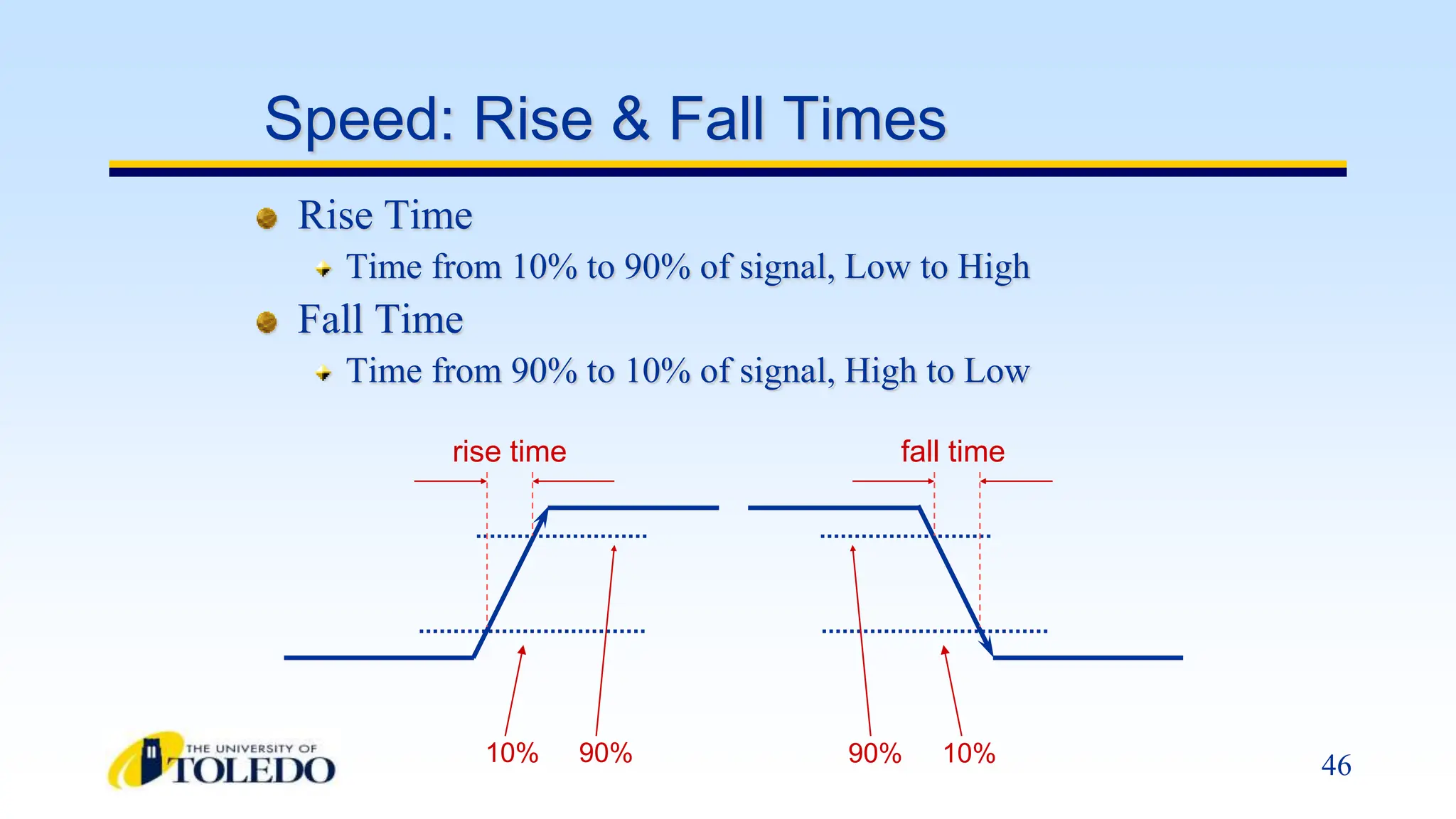

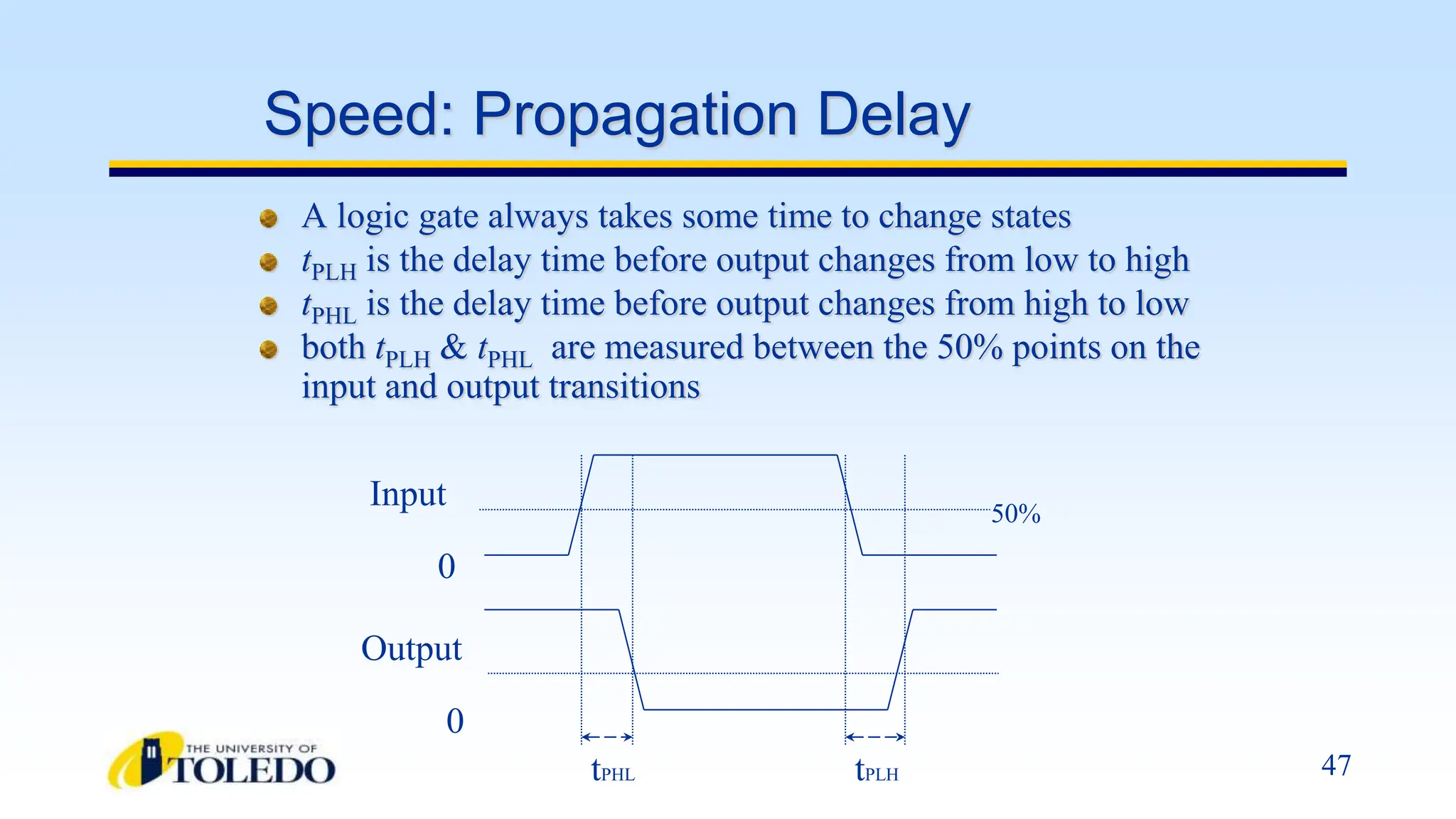

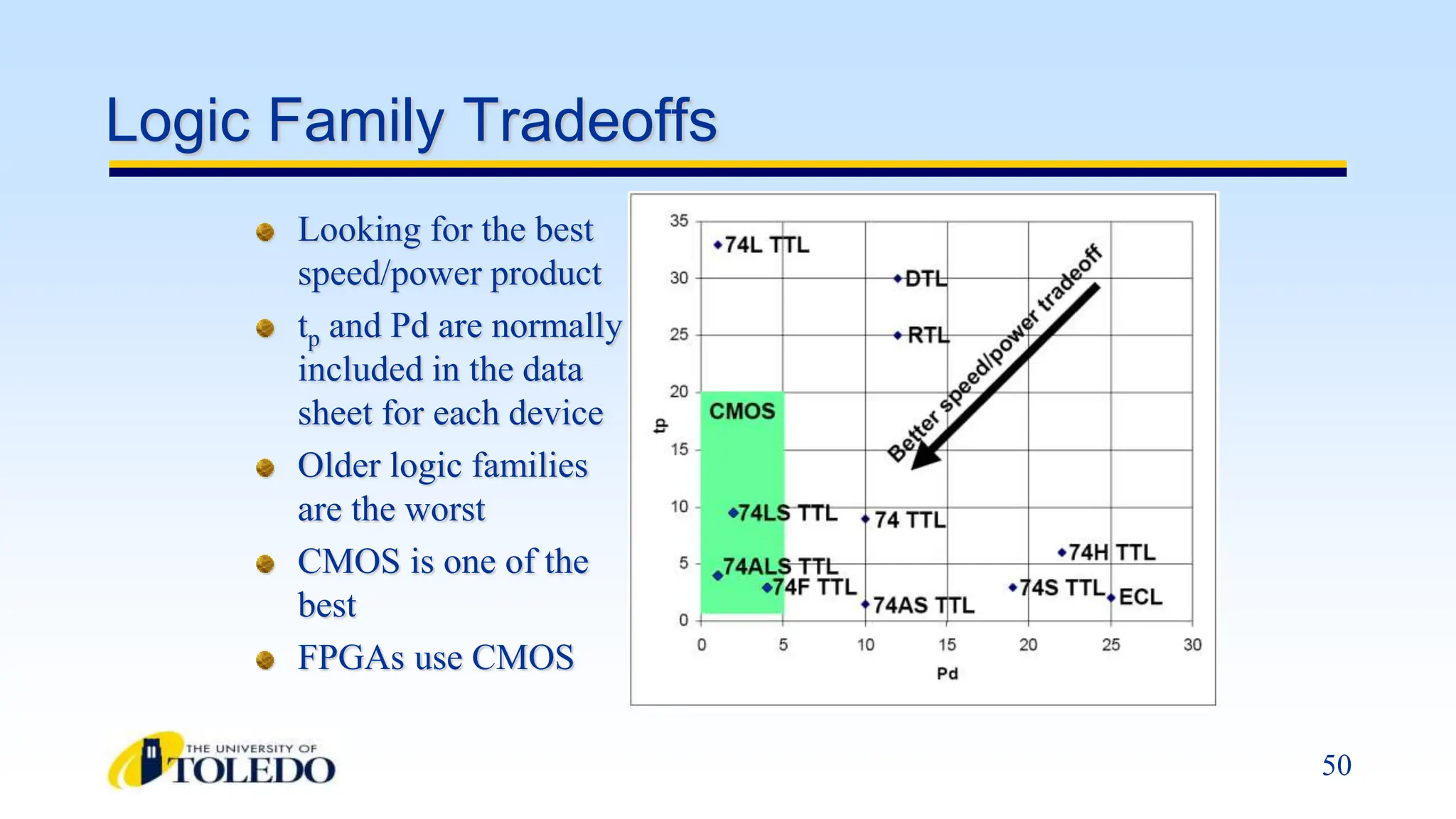

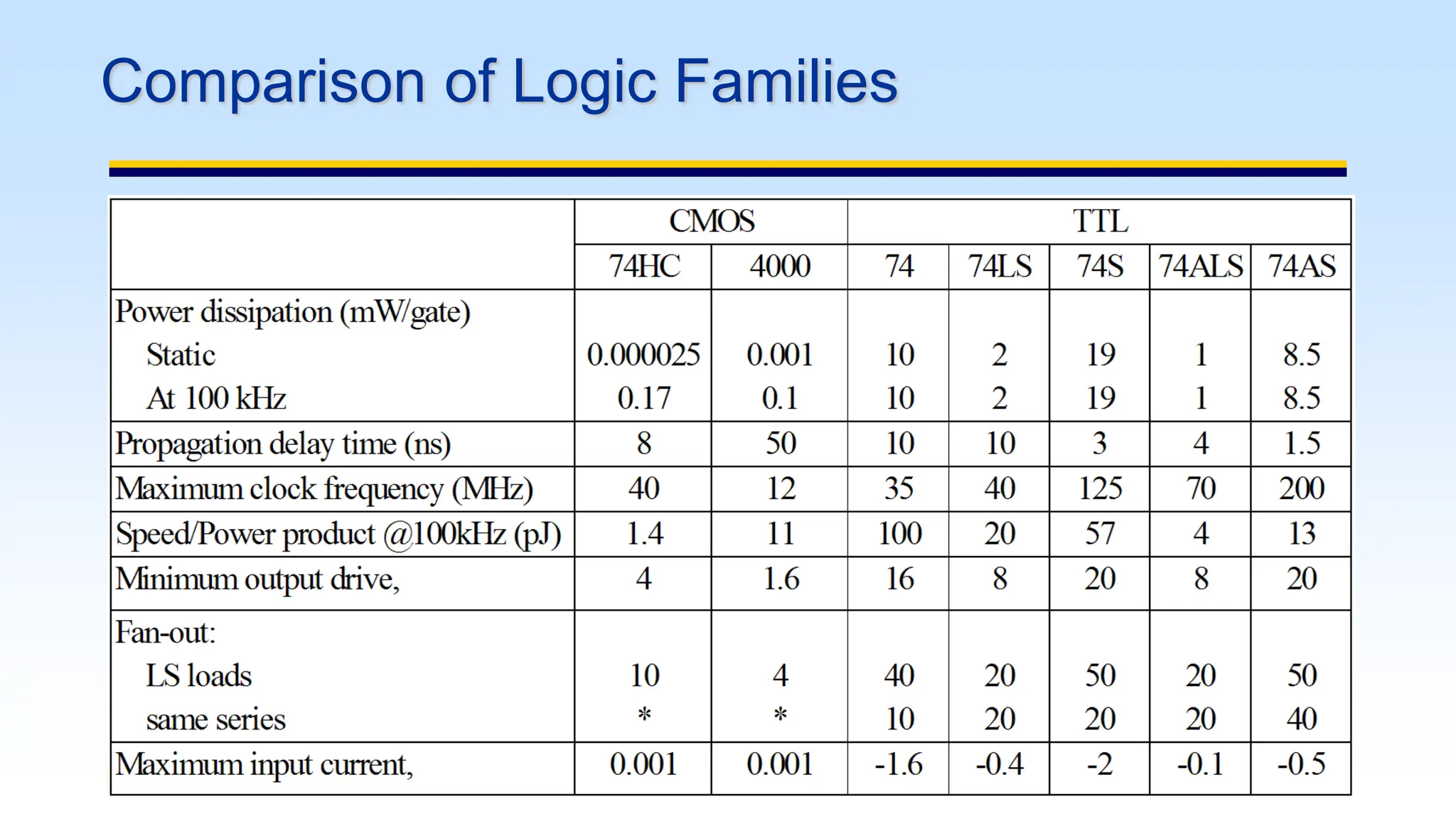

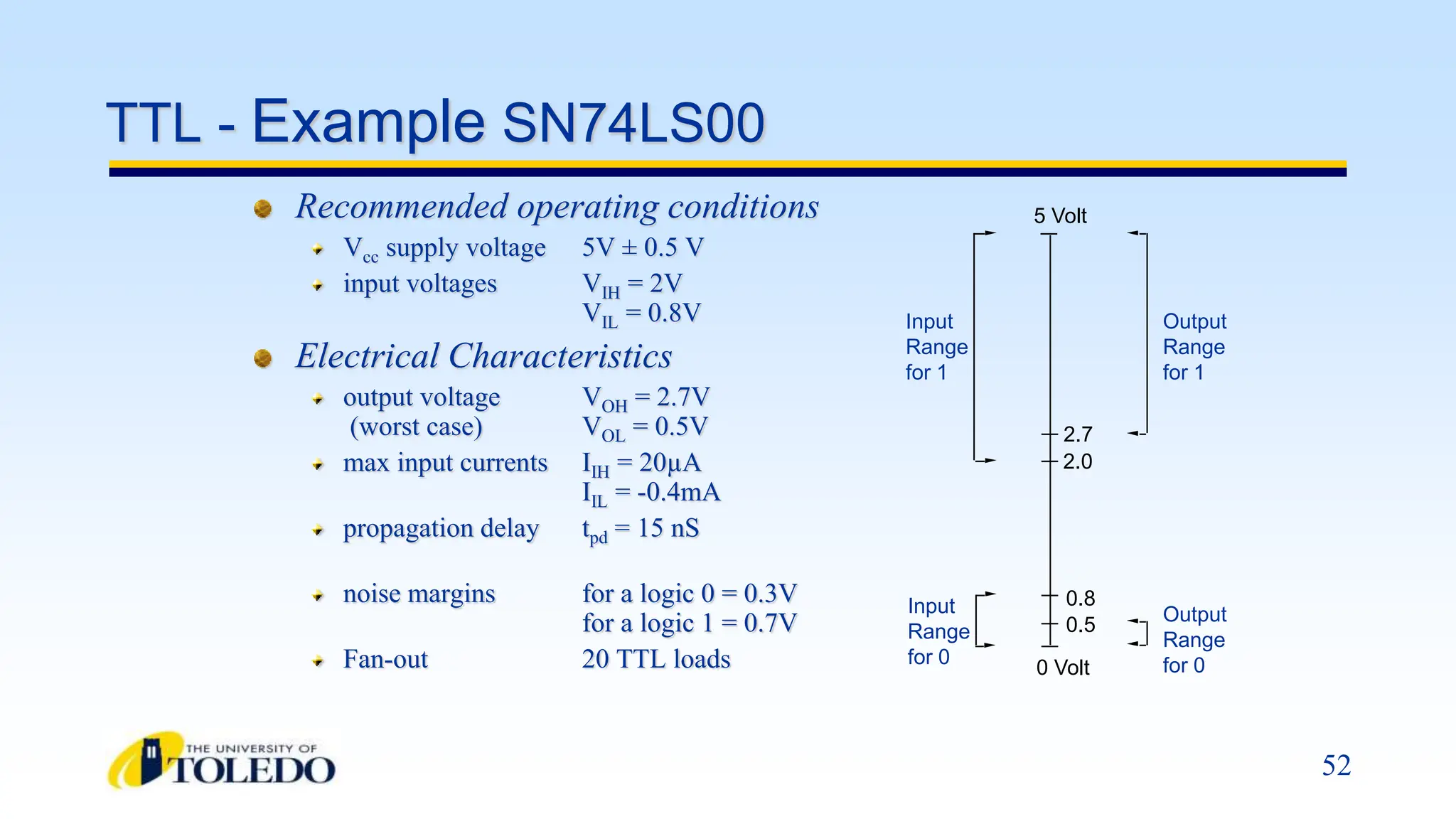

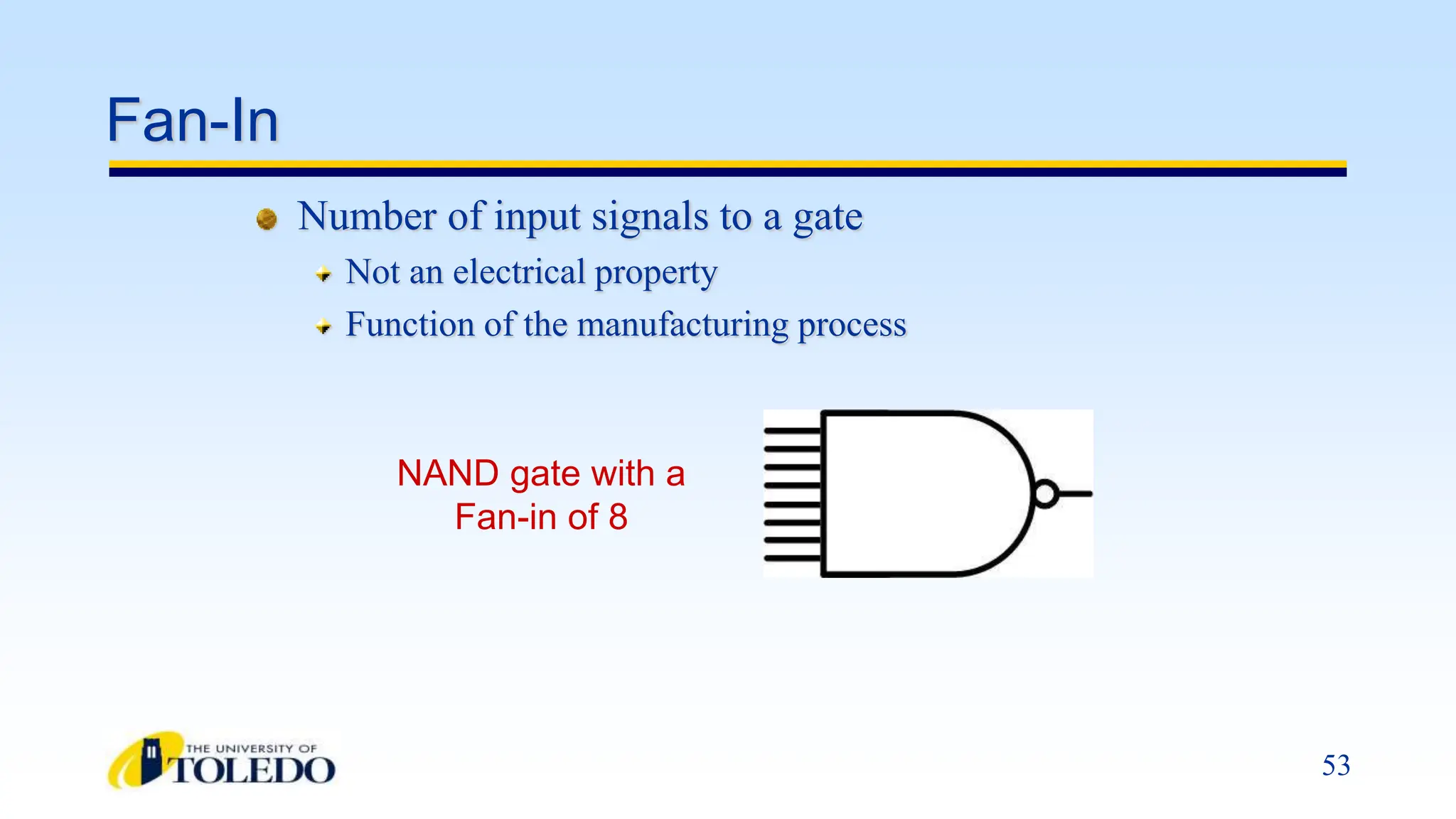

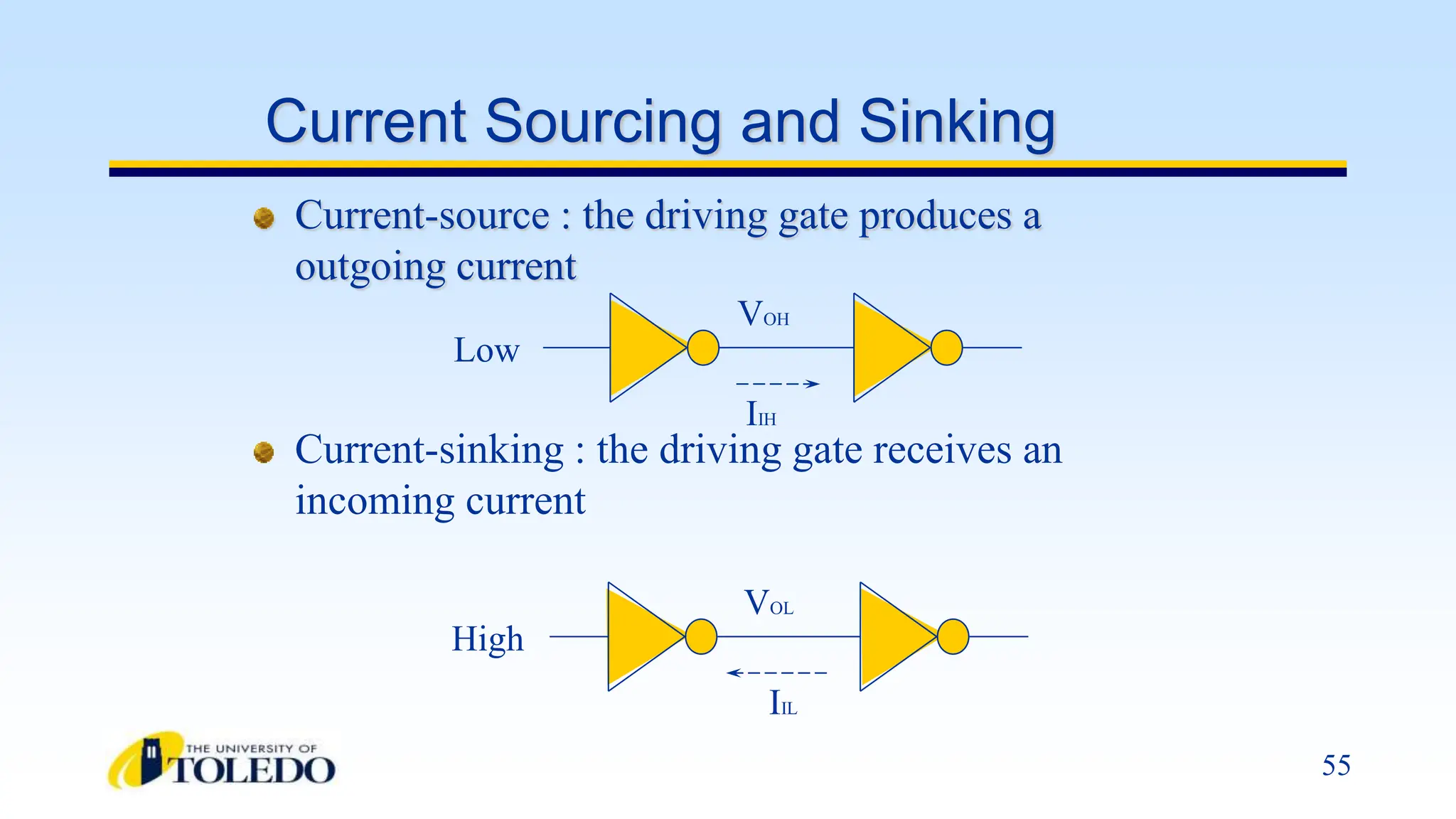

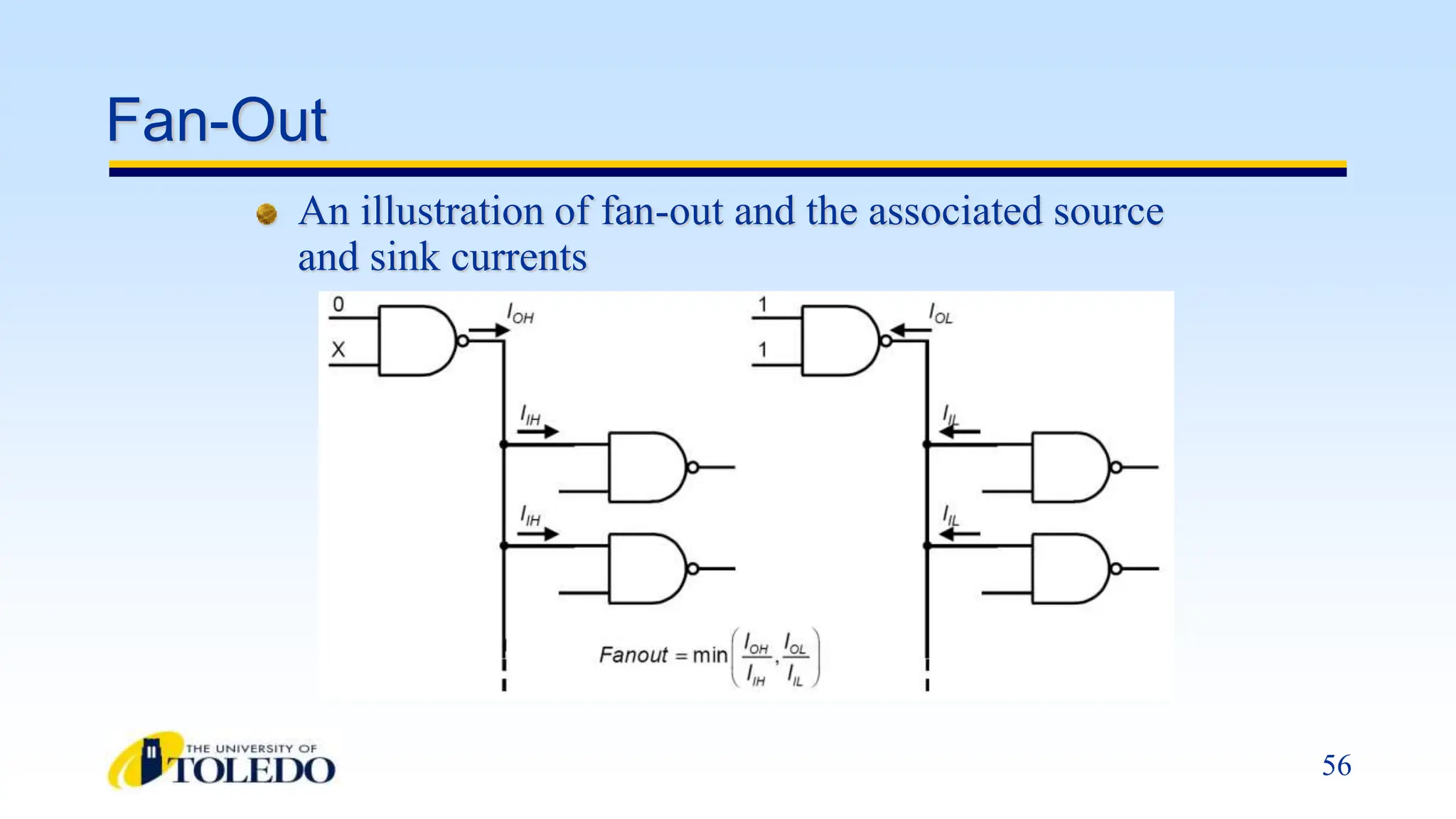

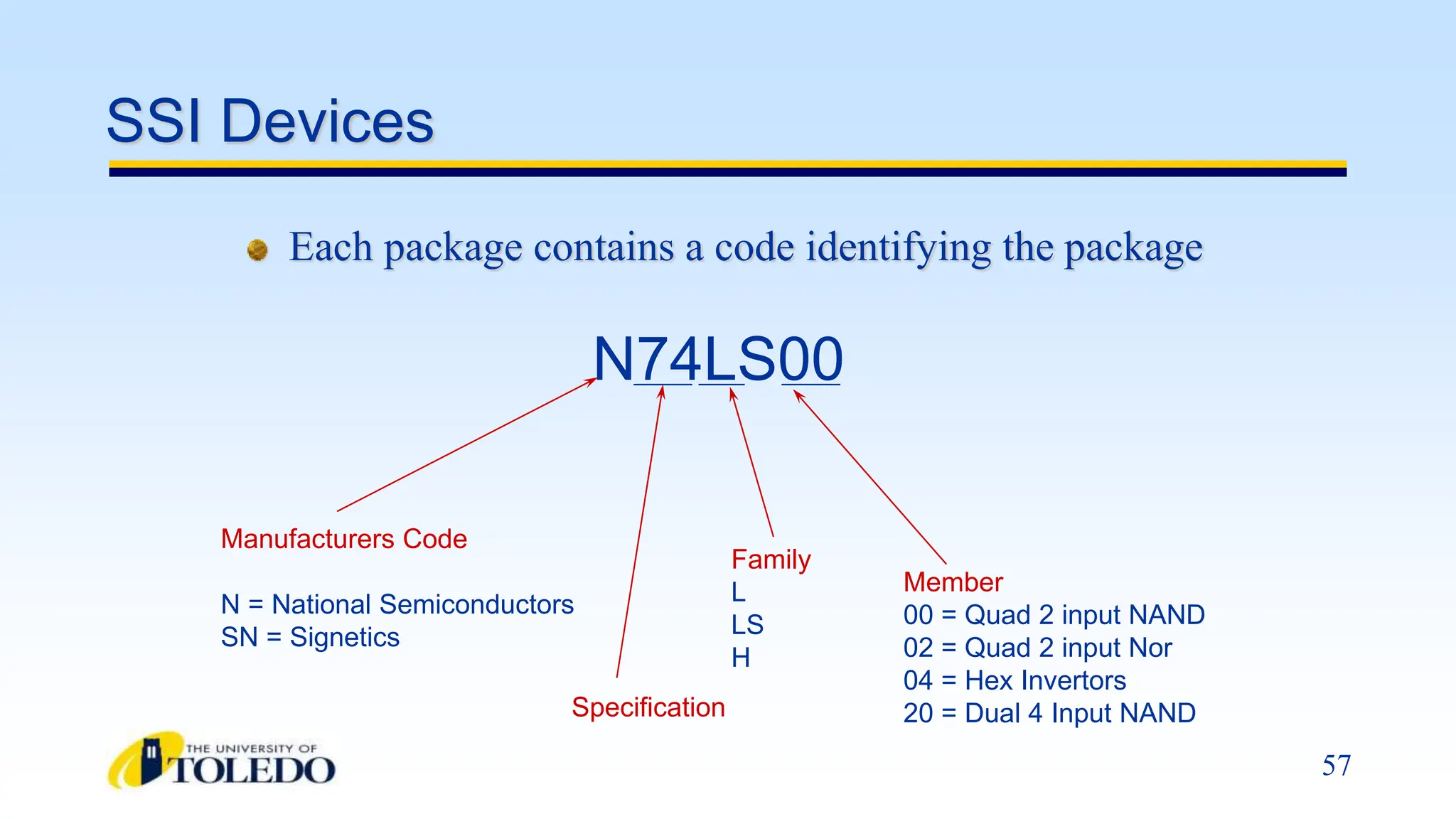

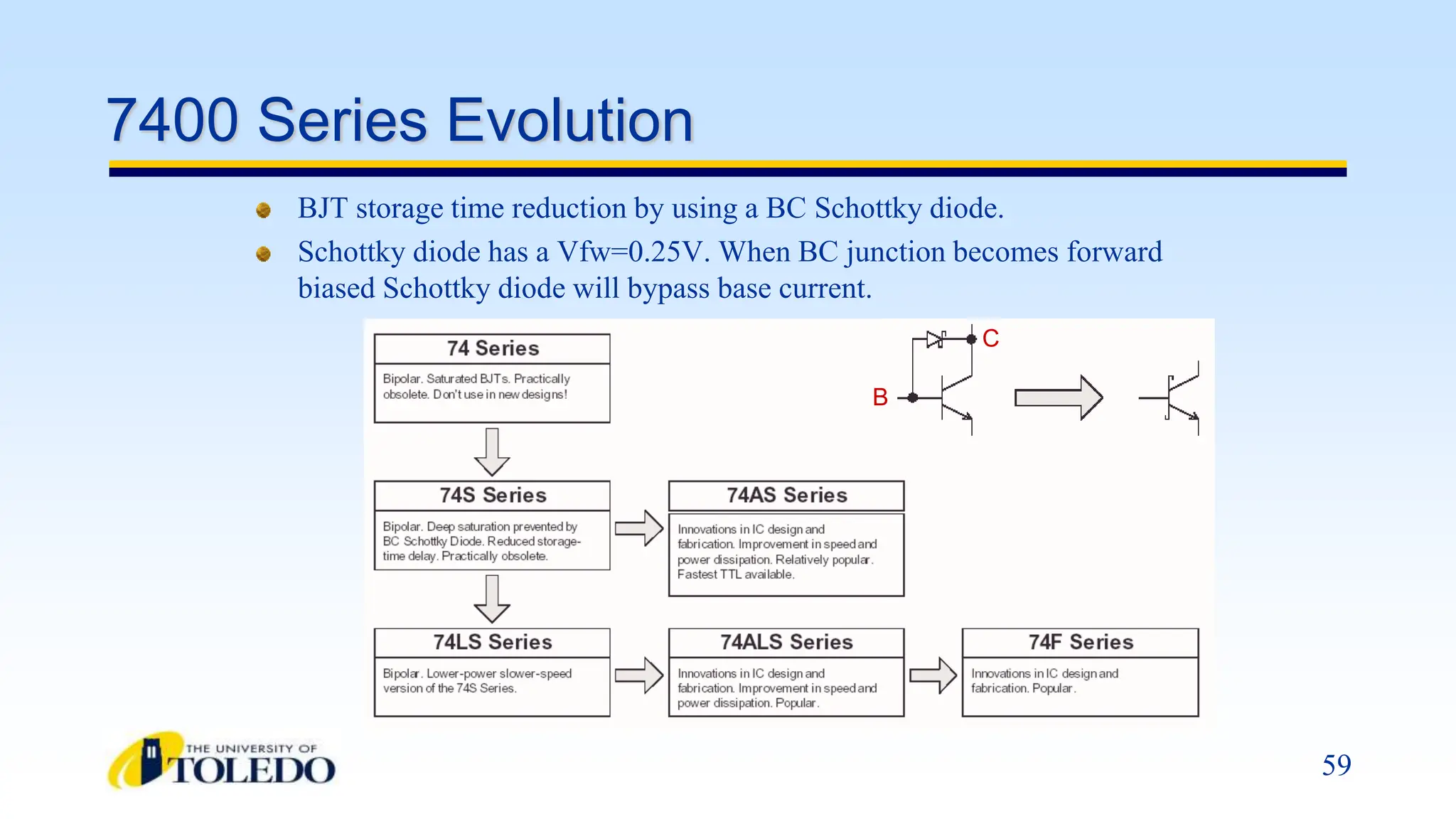

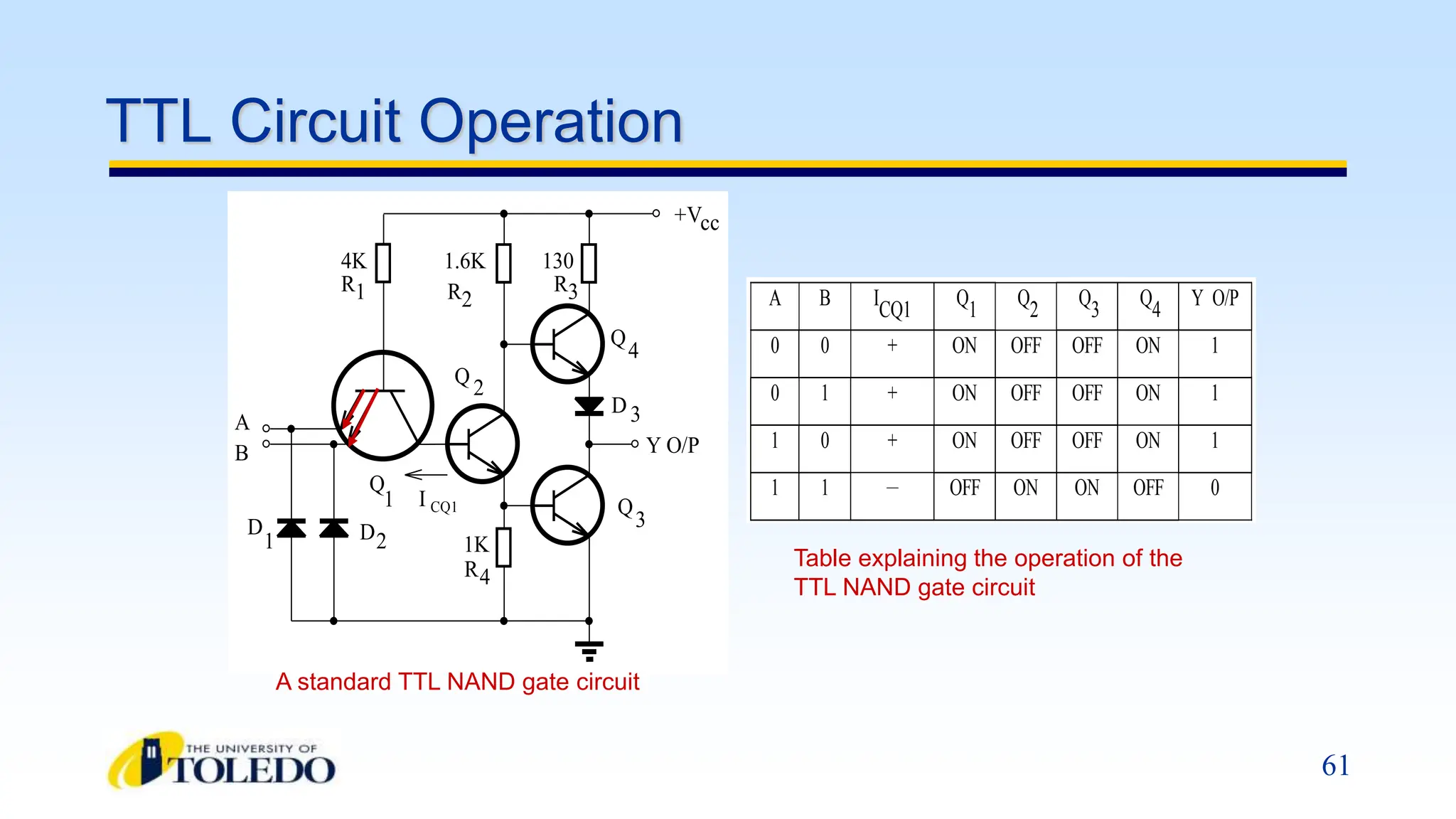

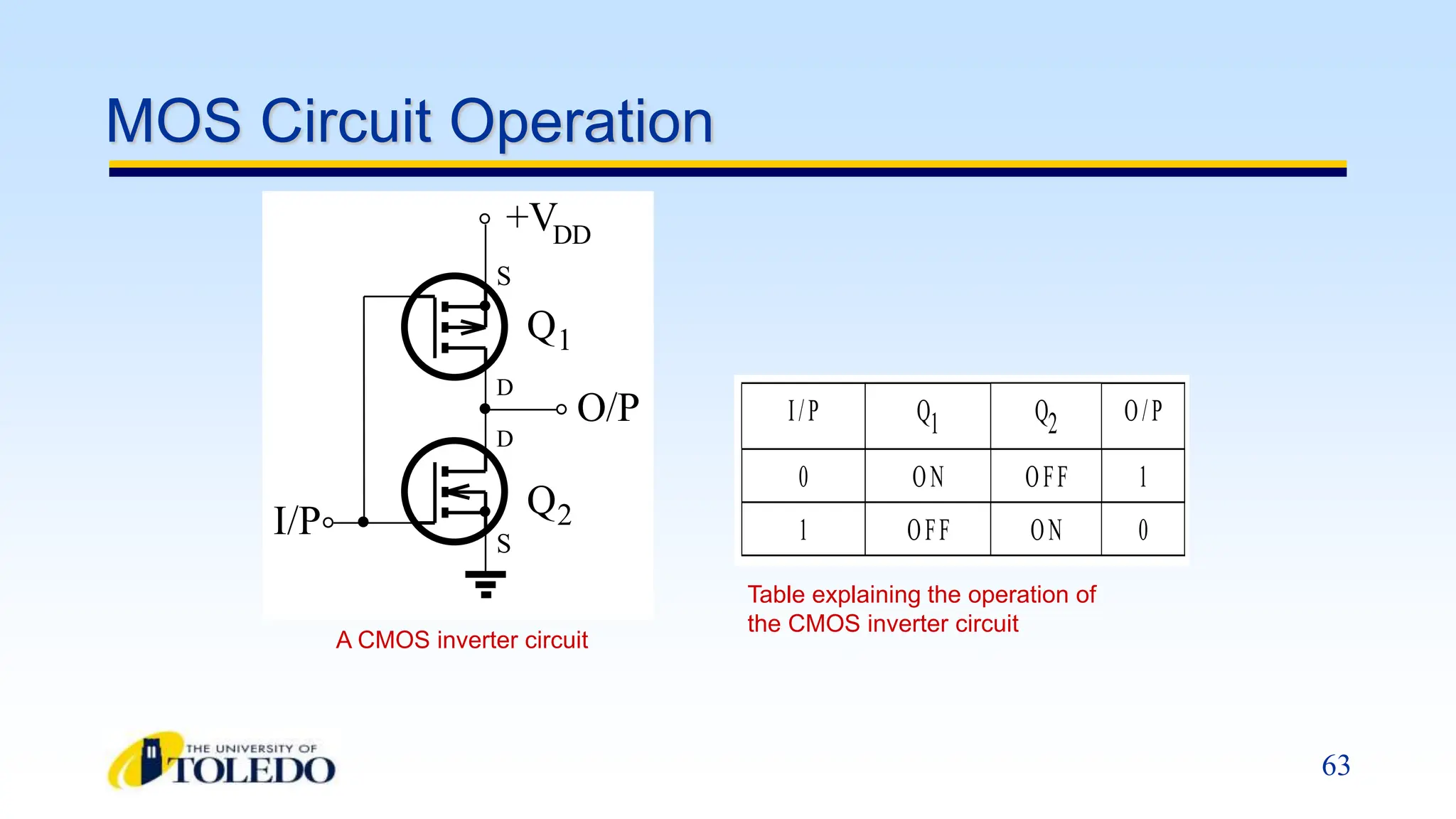

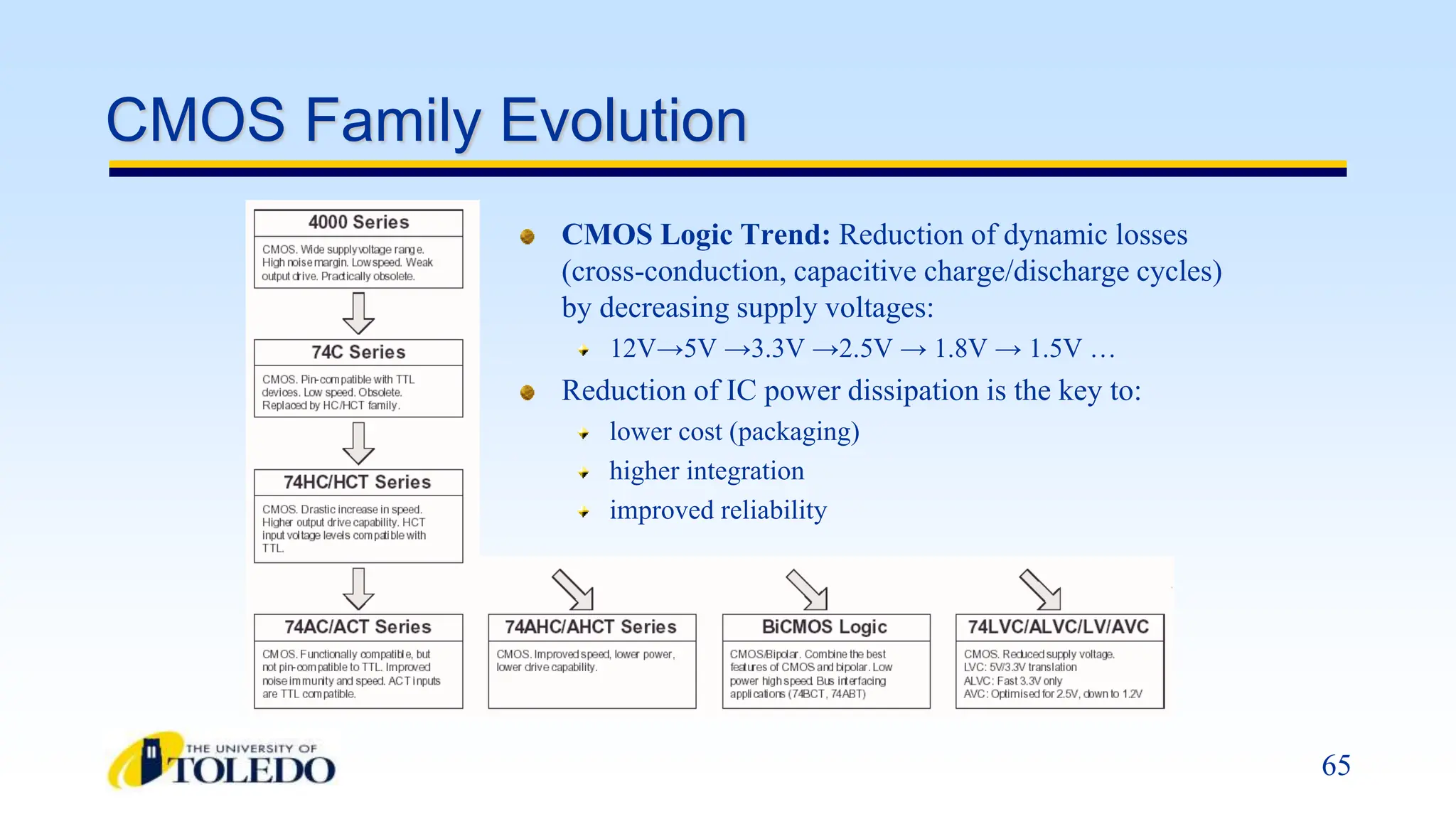

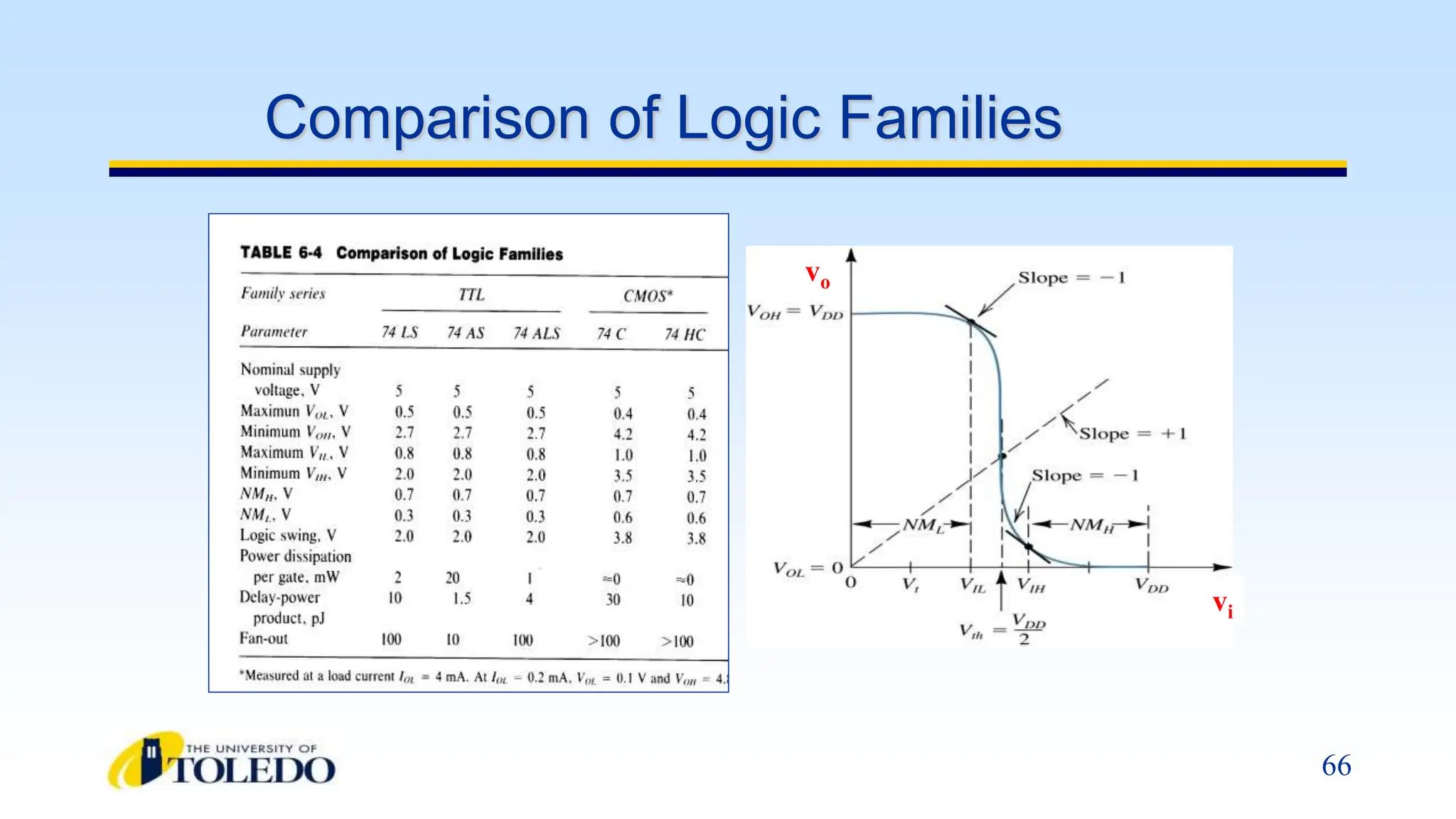

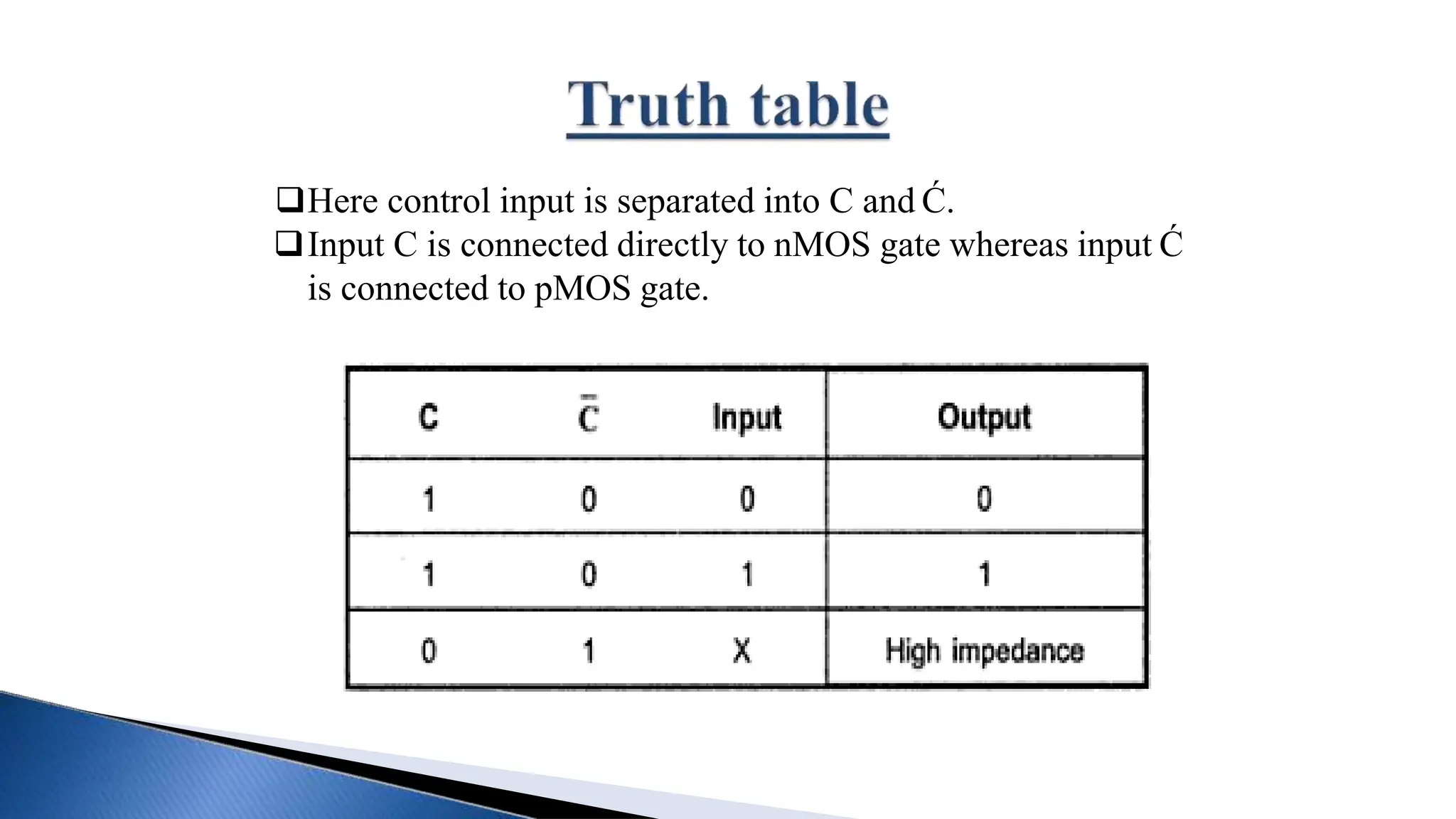

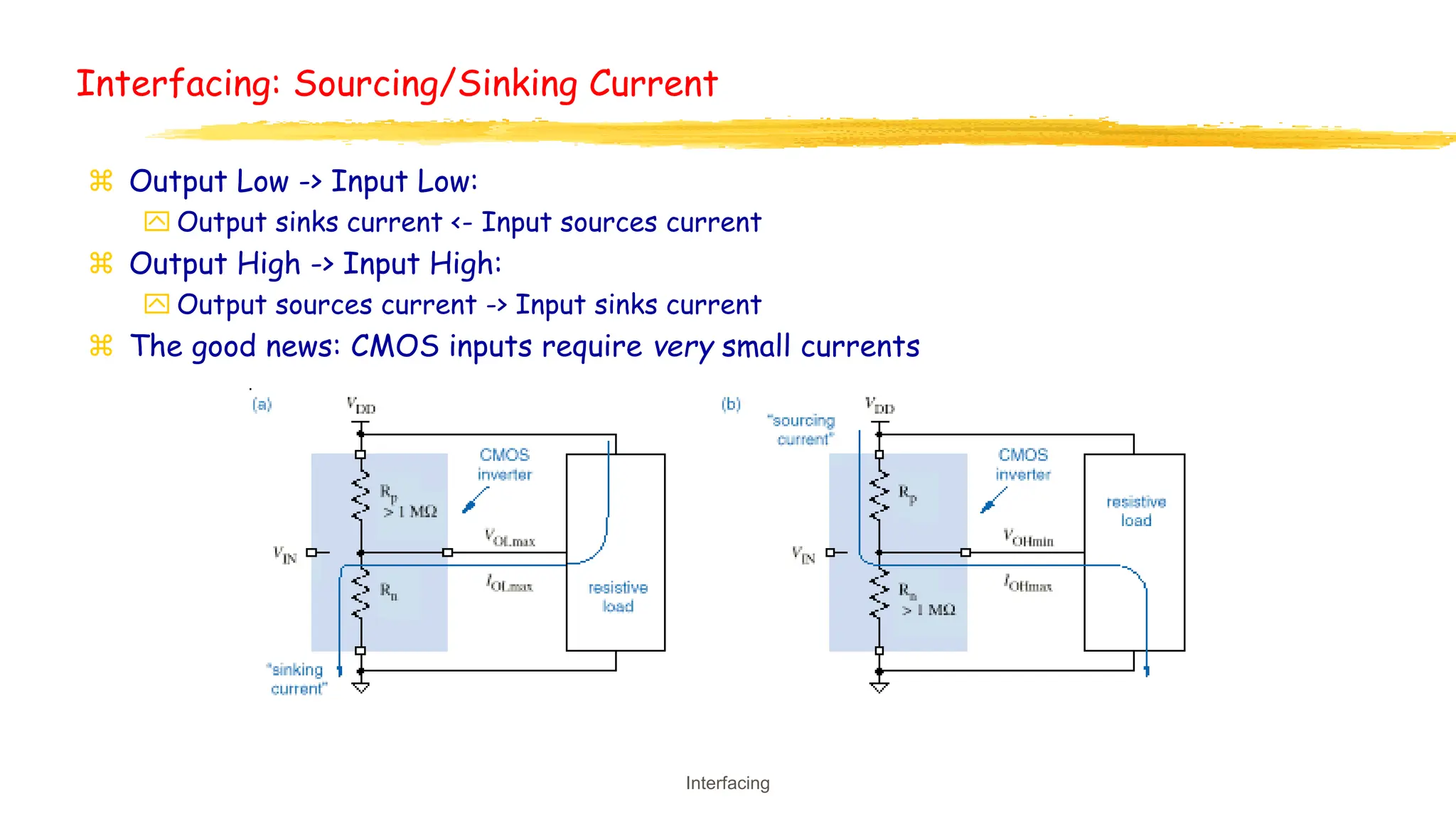

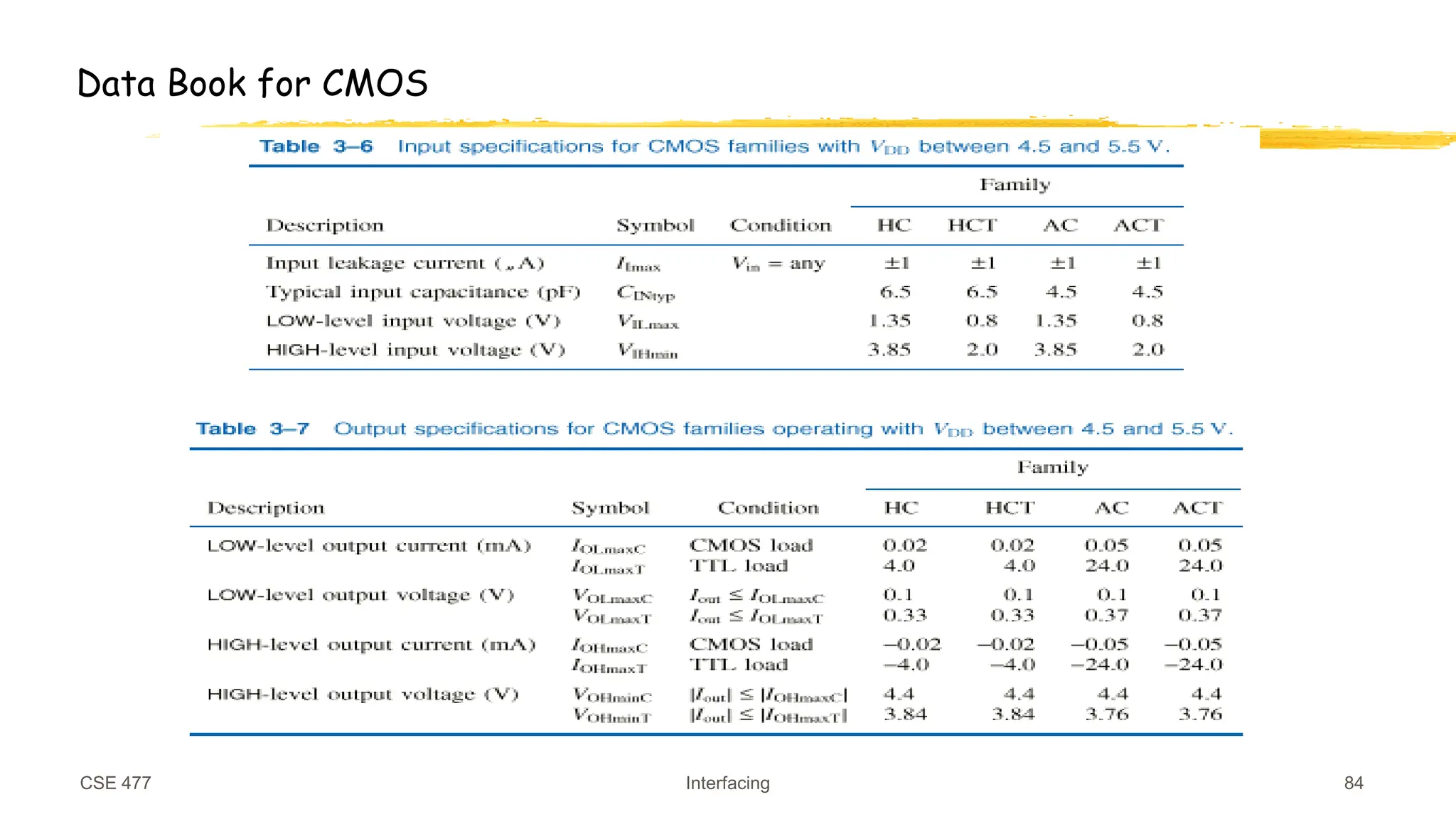

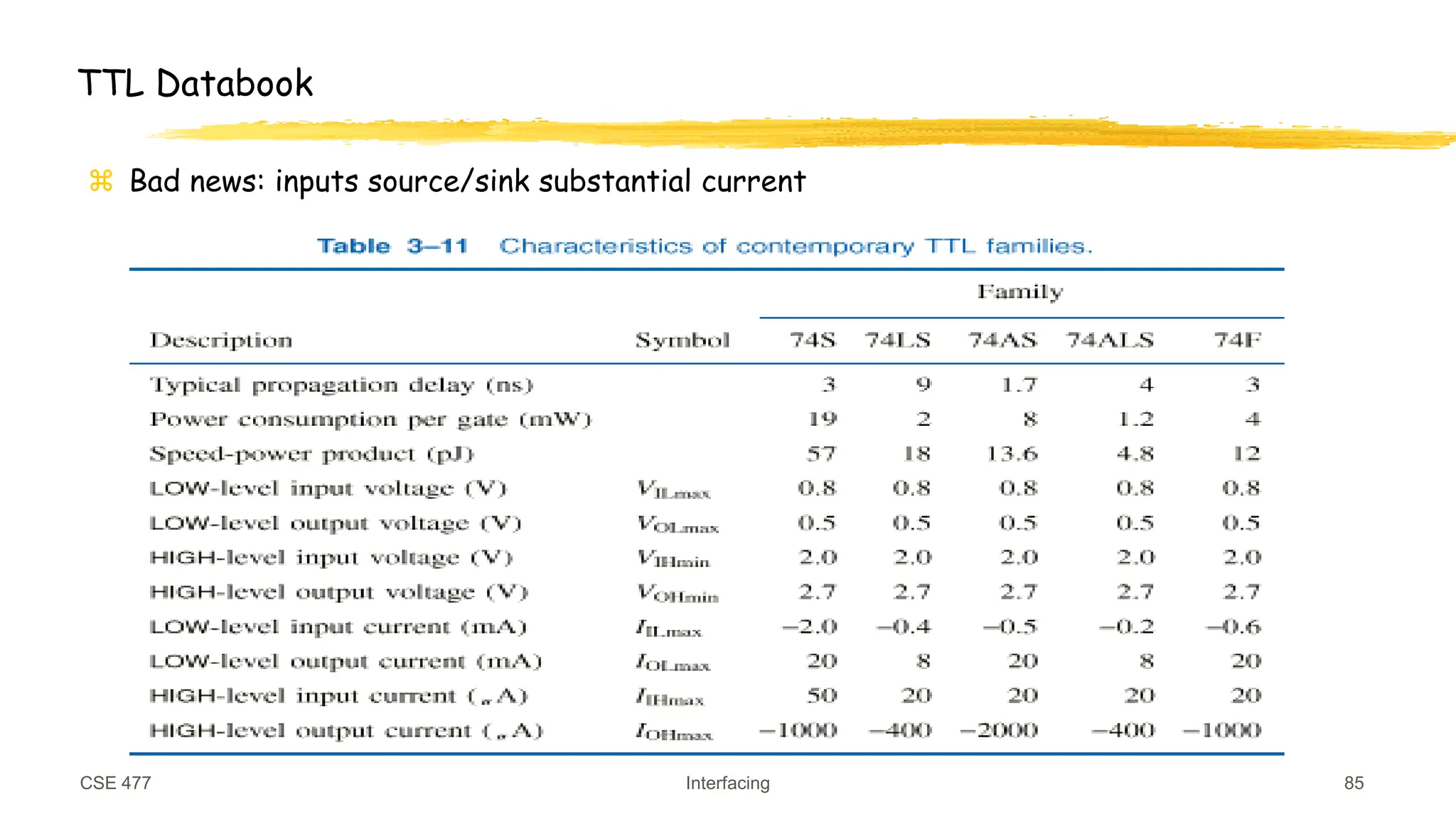

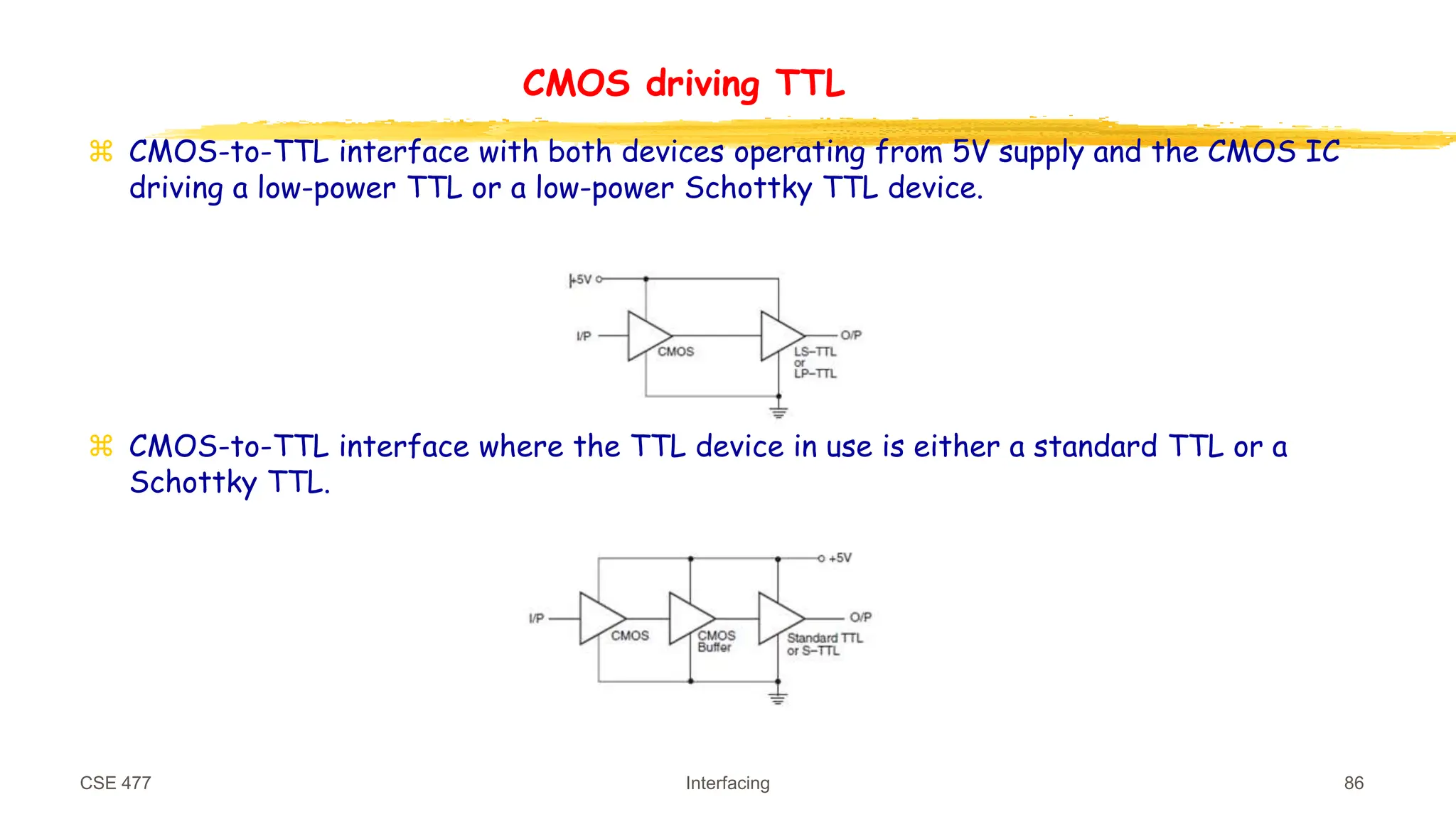

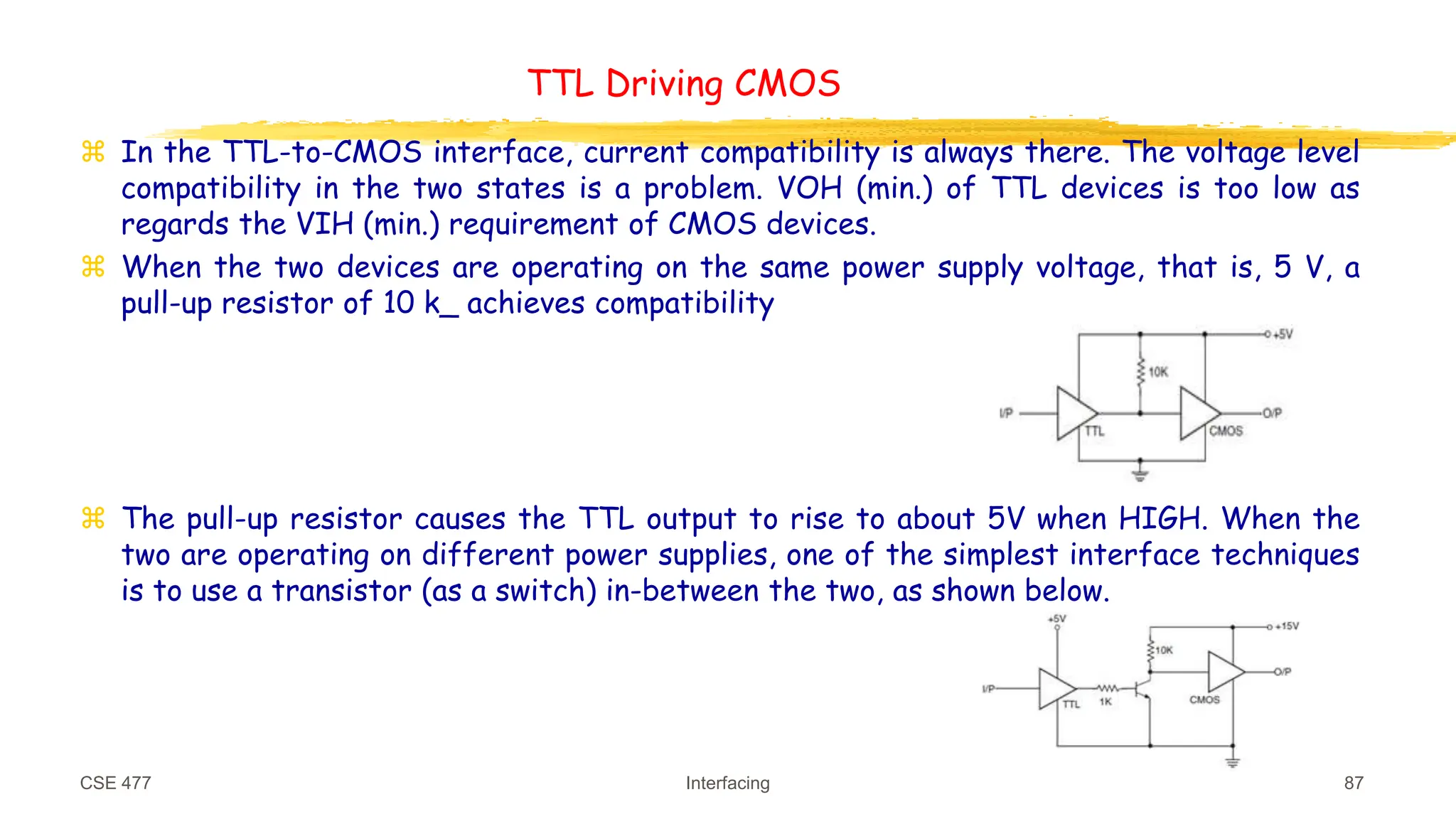

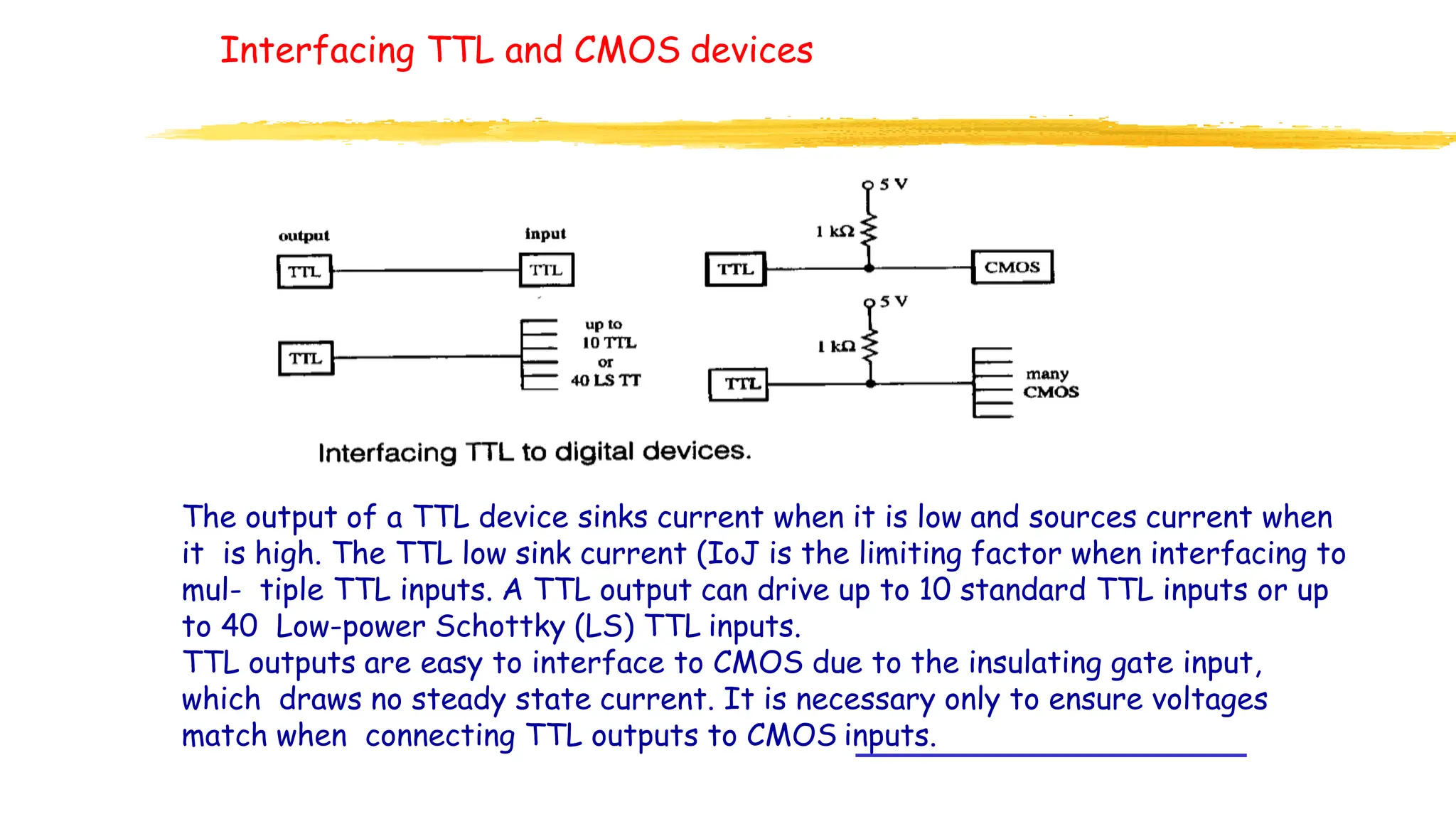

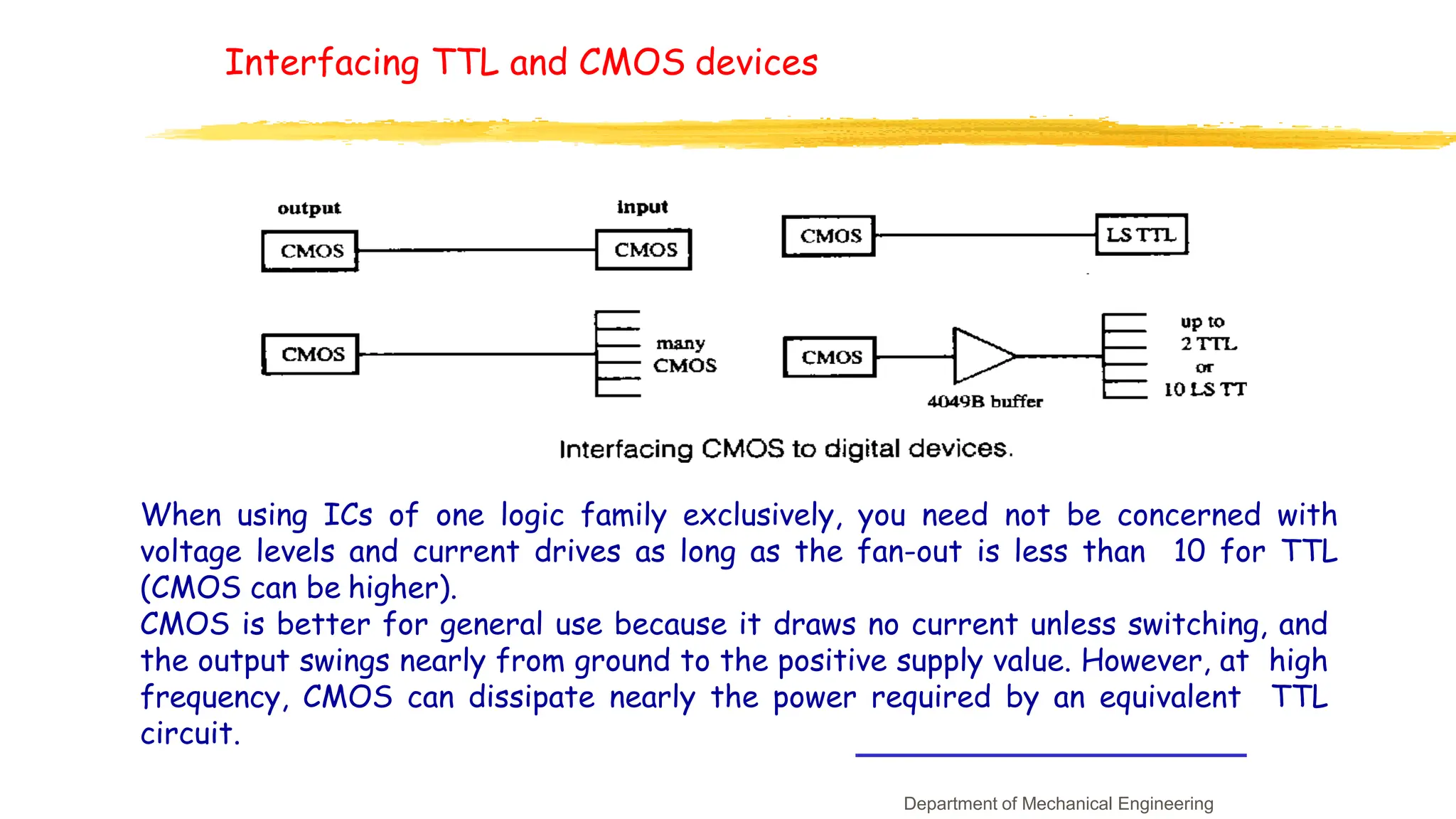

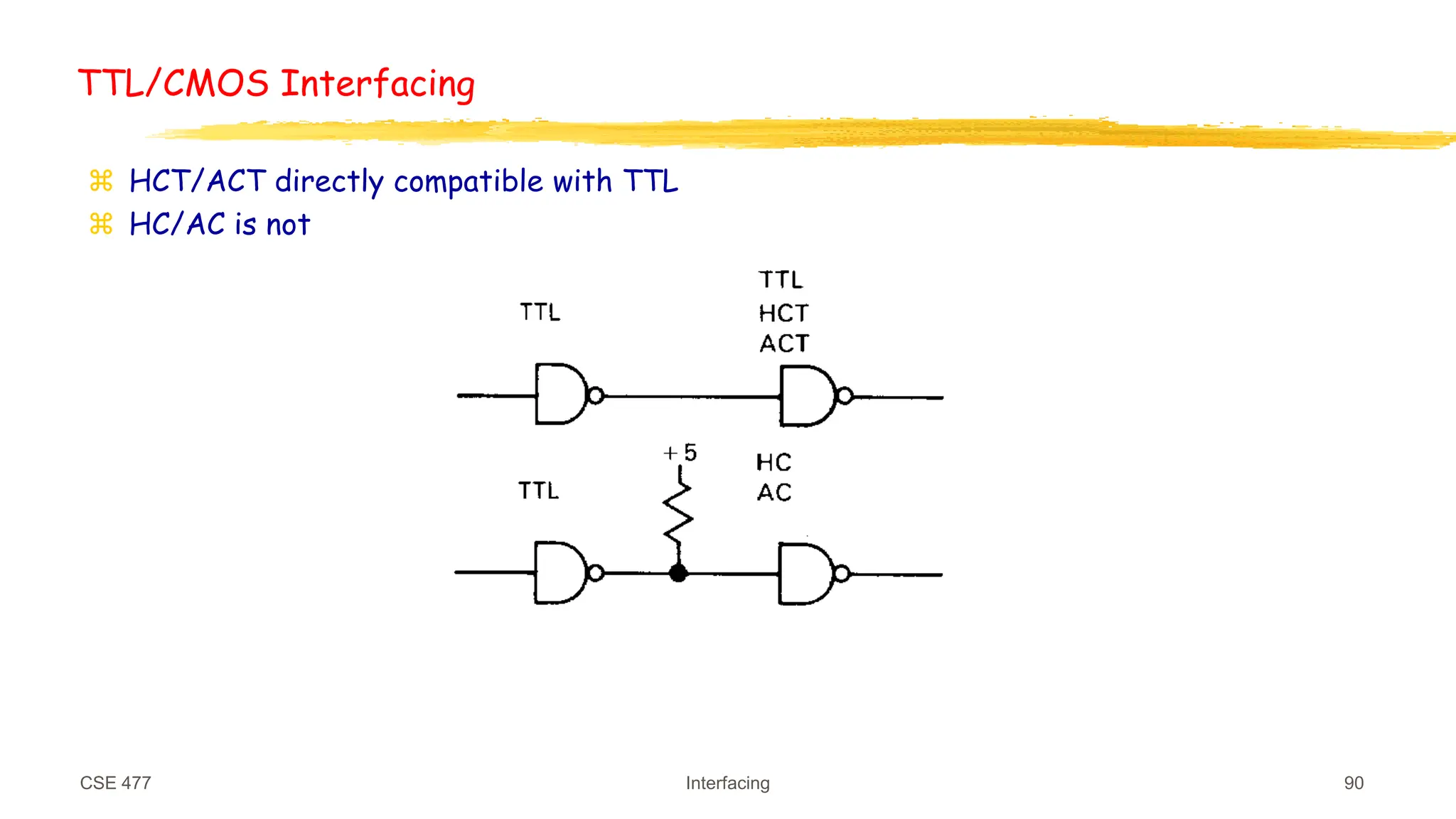

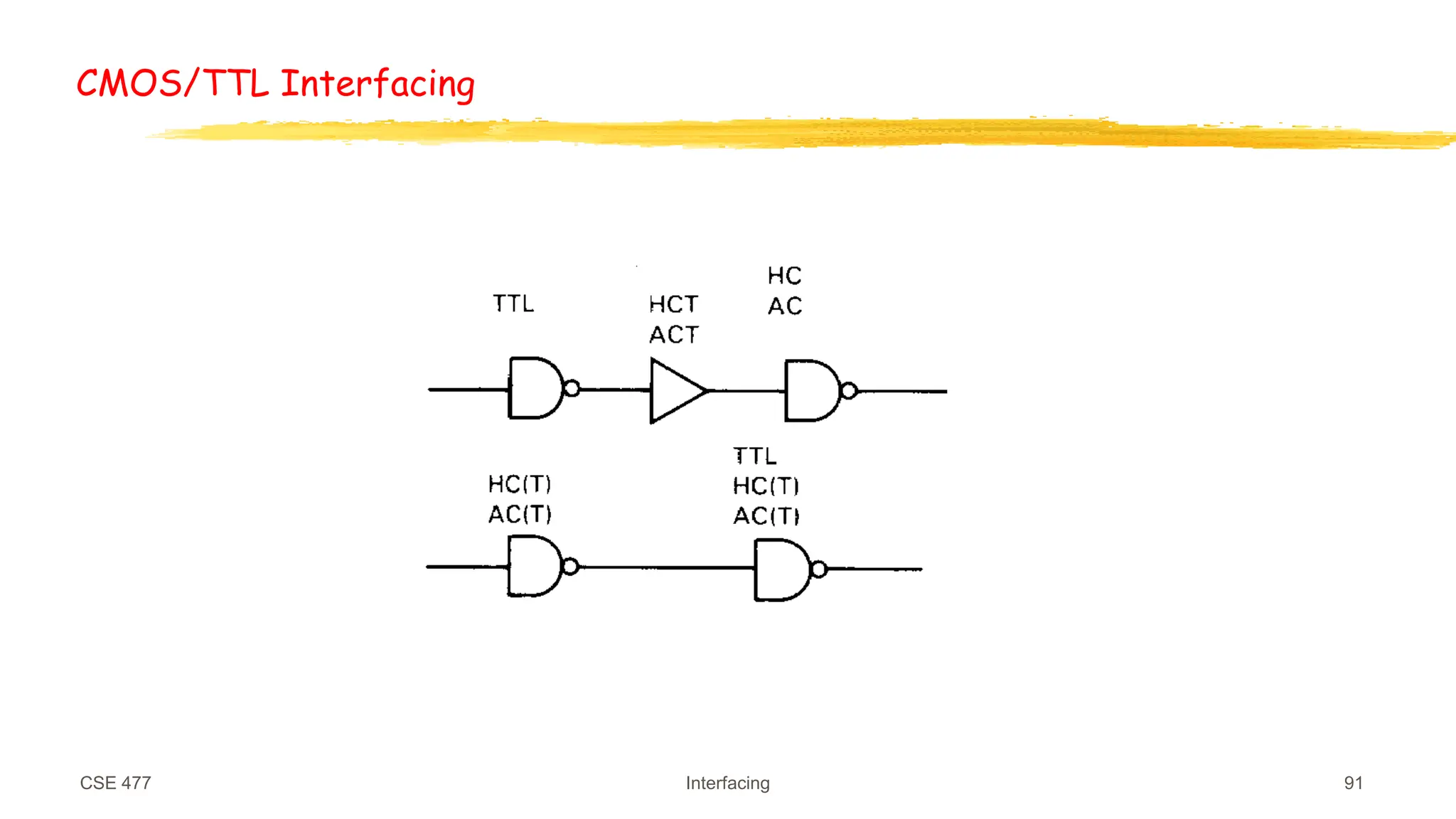

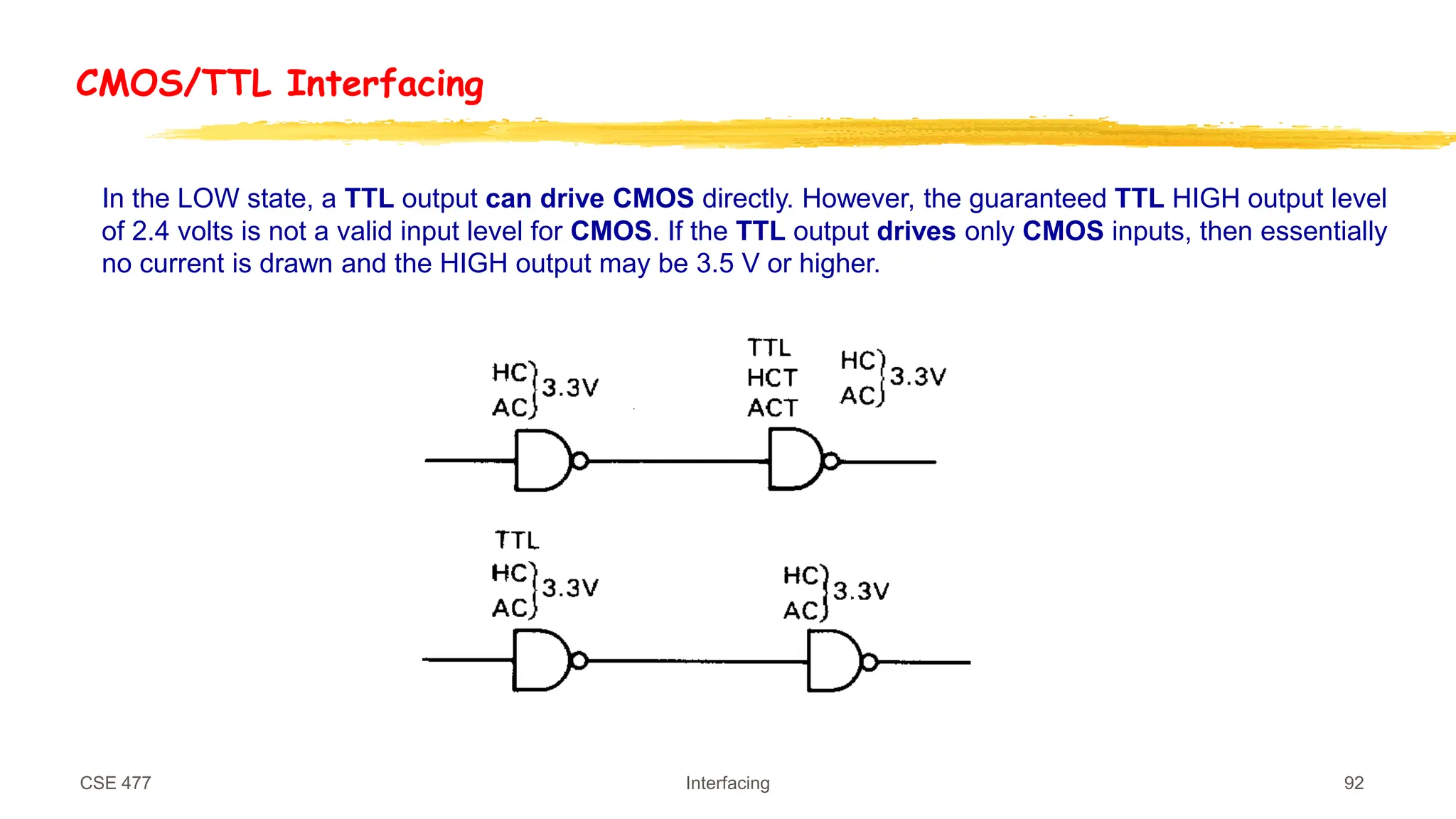

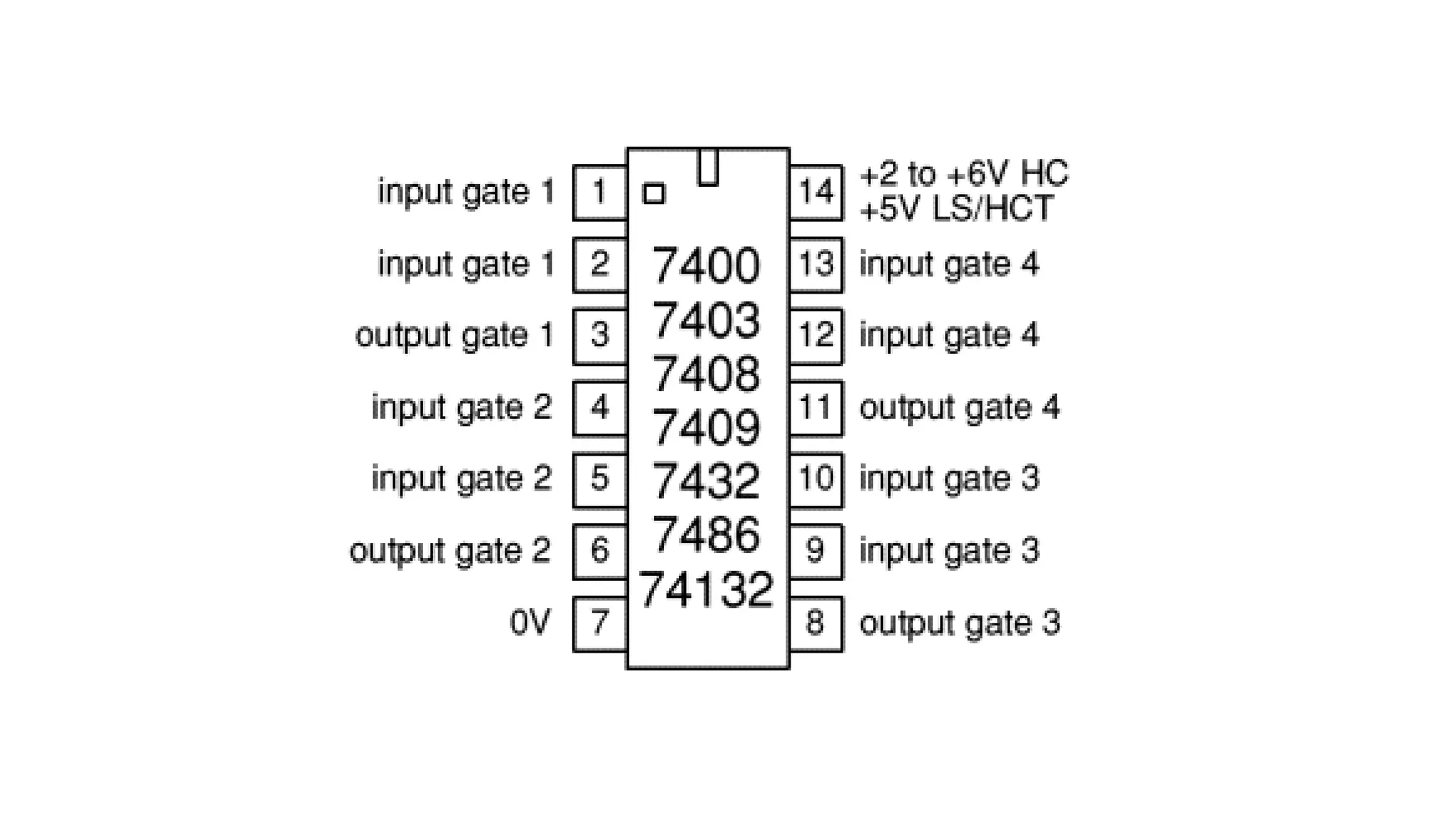

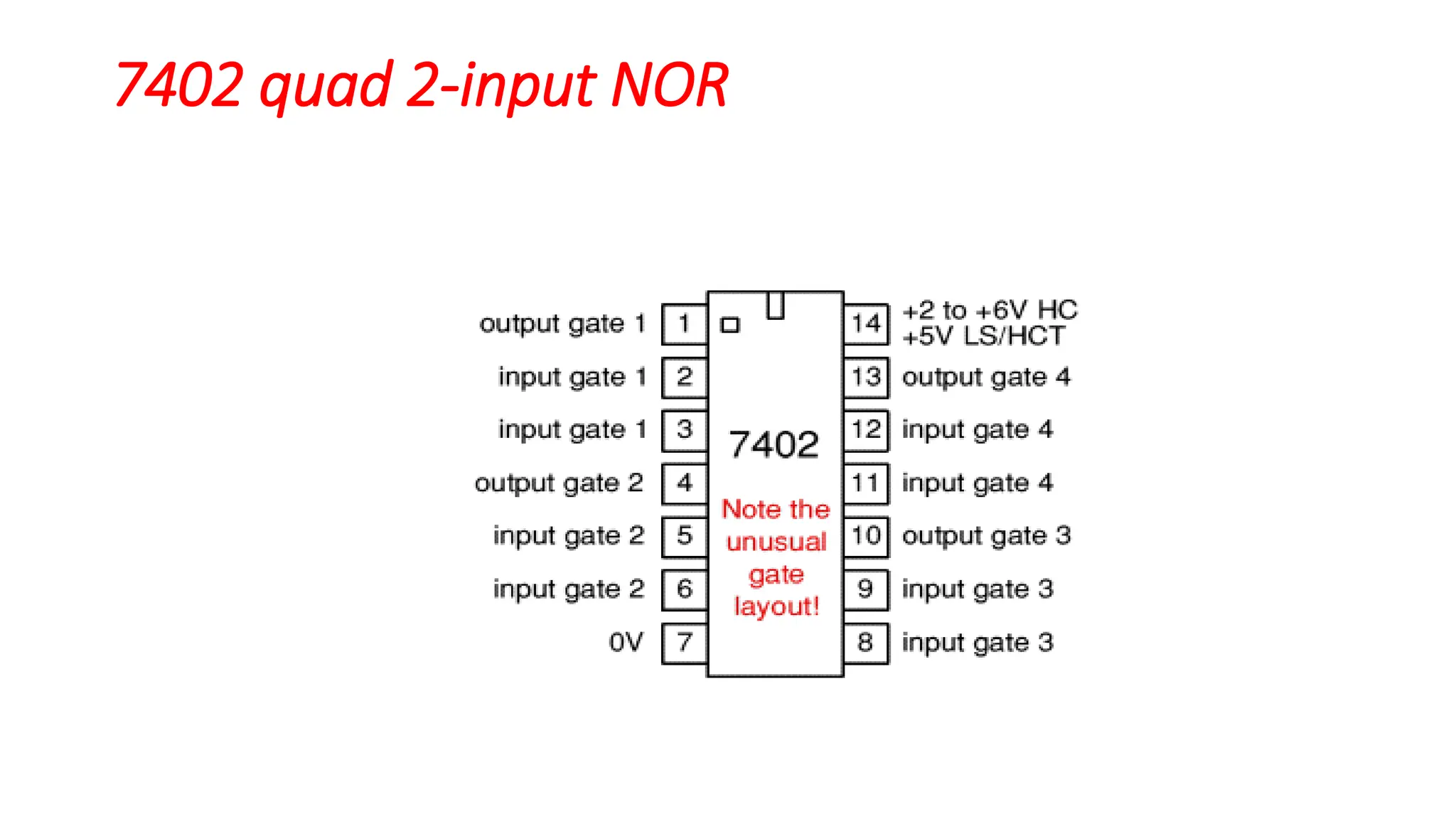

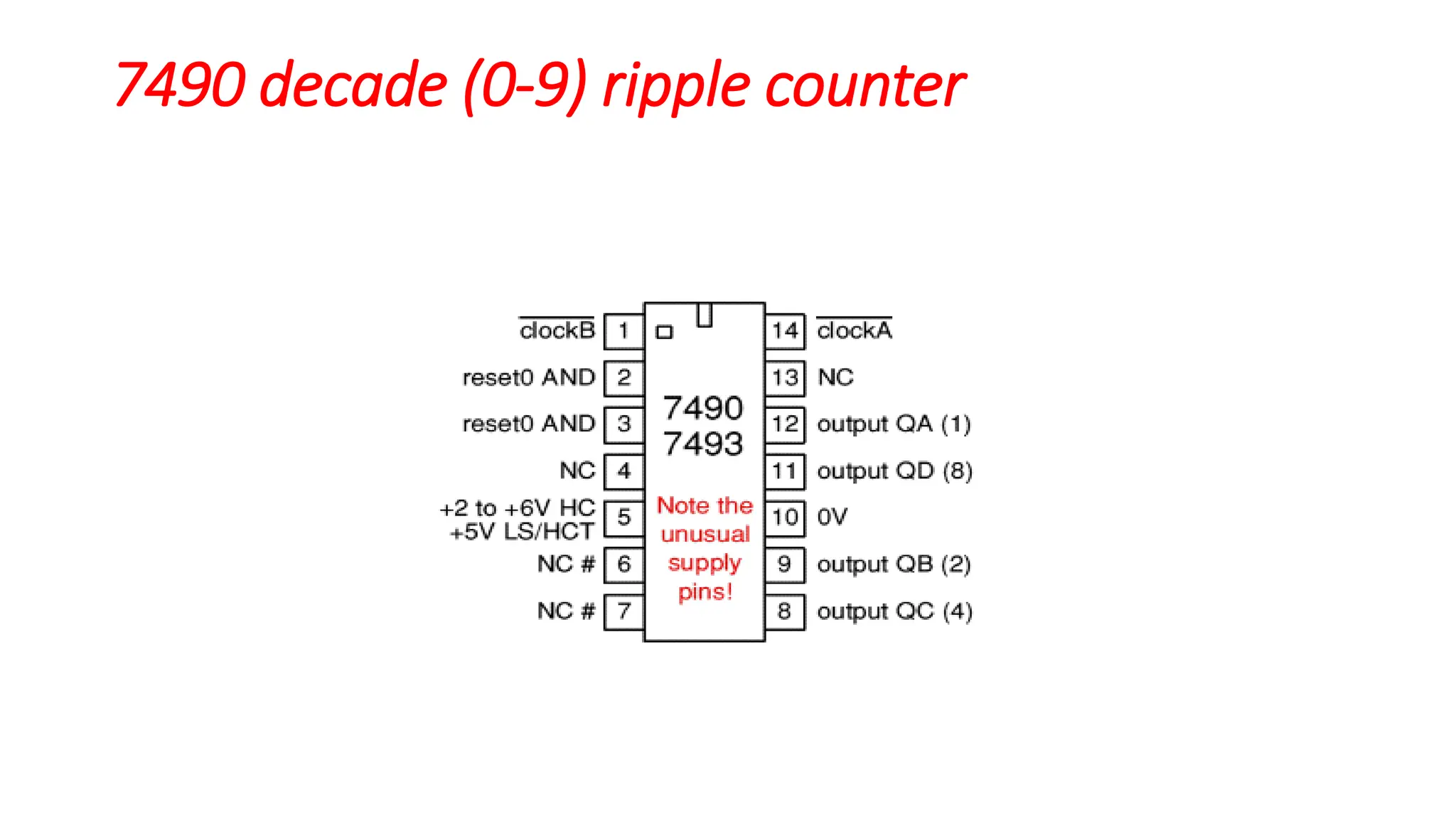

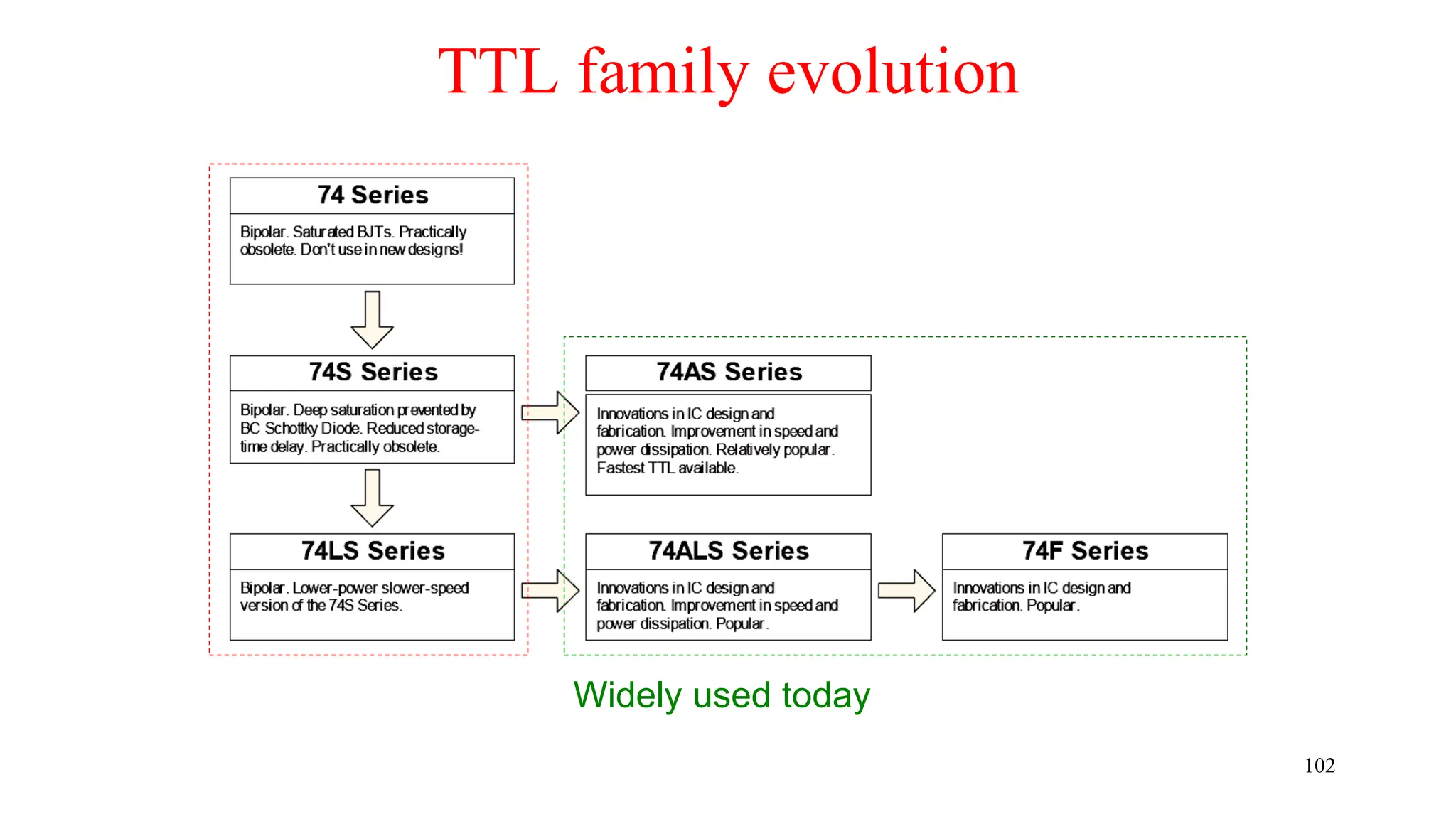

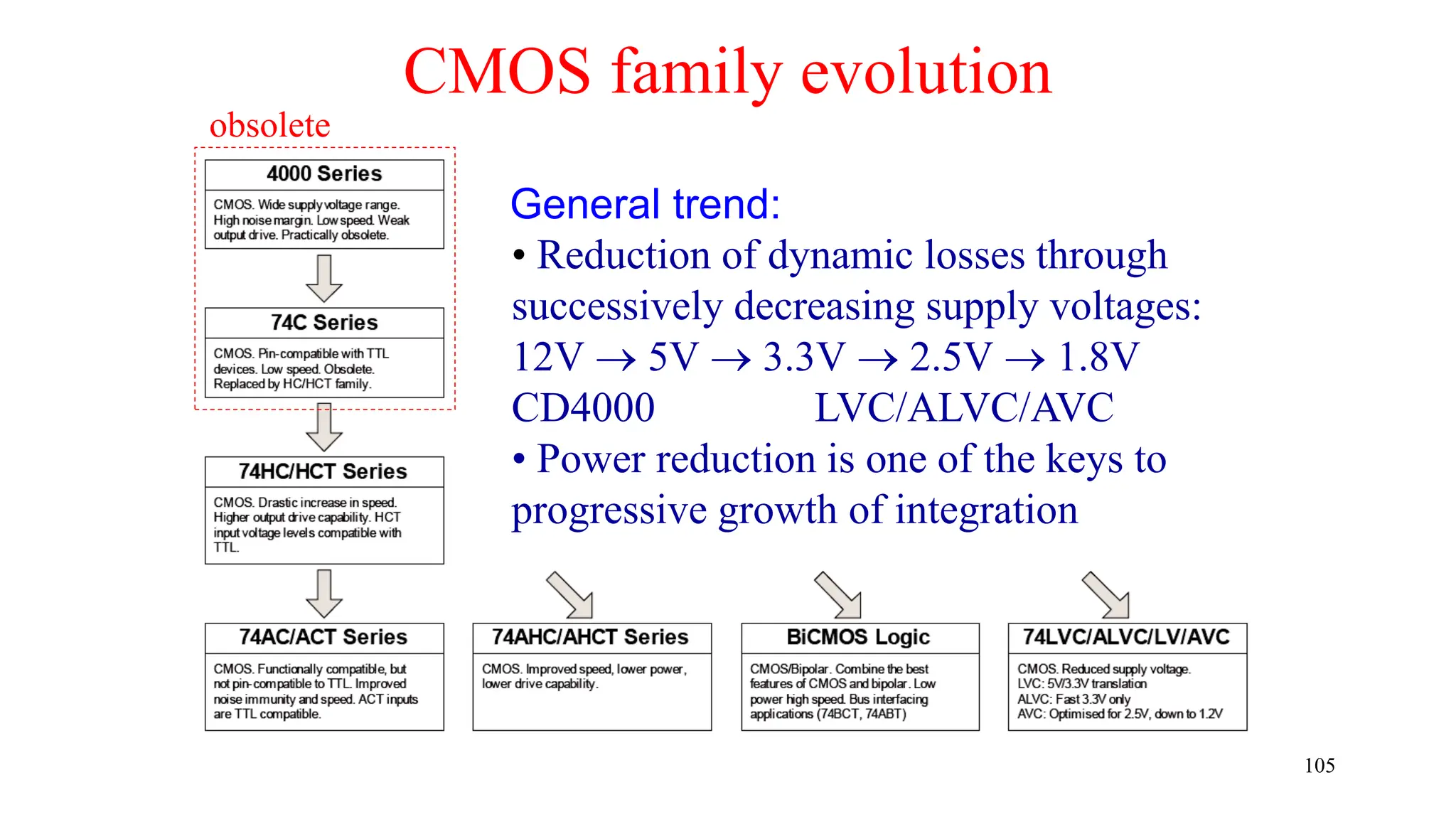

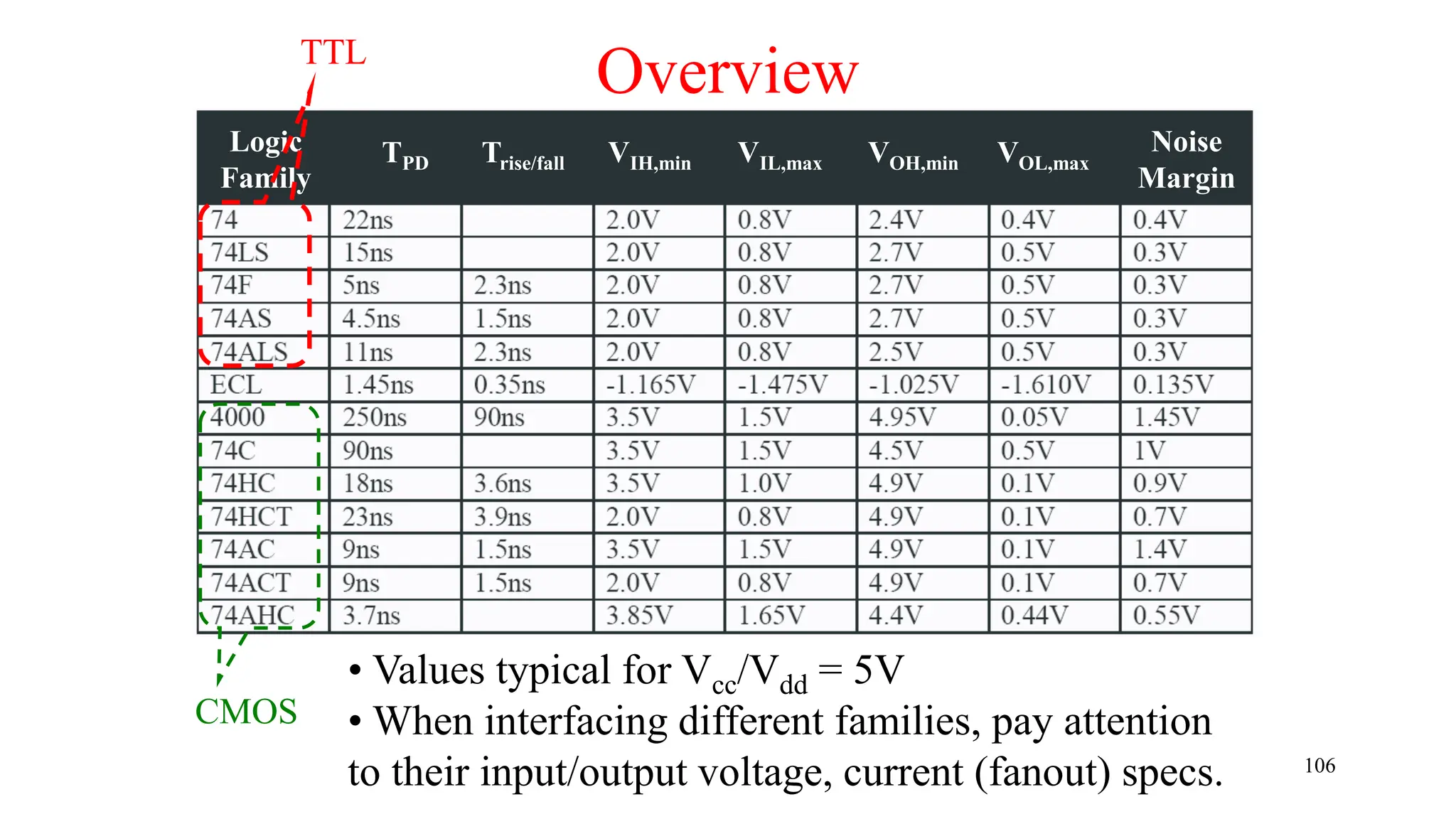

This document covers various aspects of digital integrated circuits, including classifications, structures, advantages, disadvantages, and applications of different logic families. It discusses the evolution of integrated circuits from small-scale integration to technologies like VLSI, along with specifics about TTL and CMOS, their packaging, and electrical characteristics. Additionally, it highlights parameters essential for evaluating logic families, such as noise margins, propagation delays, and power dissipation.