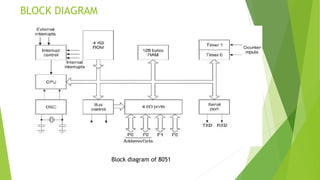

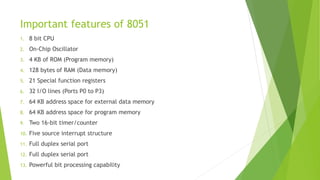

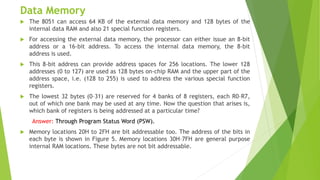

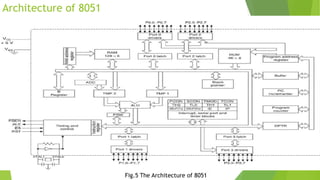

The 8051 microcontroller is designed for real-time applications like industrial control and automobiles. It has features like interrupts, bit addressability, and an enhanced instruction set that make it powerful and cost-effective. The 8051 has 4KB of internal ROM, 128 bytes of internal RAM, 32 I/O lines, and can access up to 64KB each of external program and data memory. It has various special function registers that control timers, serial ports, and interrupts to interface with peripherals. The 8051's architecture includes a CPU, program memory, data memory, ports, and special function registers connected via an internal bus.