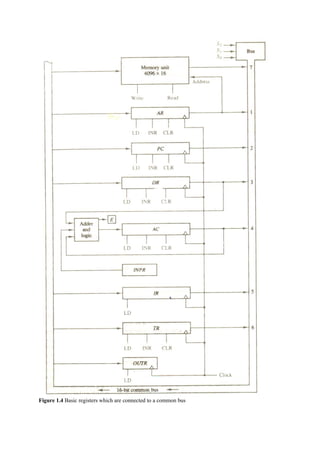

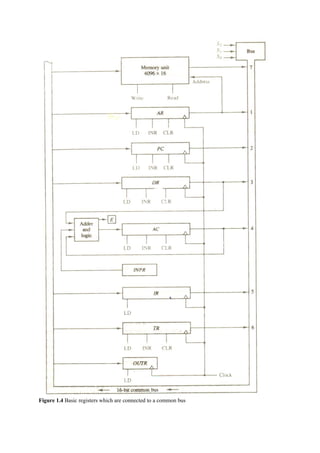

This document discusses computer instruction codes and the basic organization of a stored program computer. It describes how instruction codes specify operations for the computer to perform and are stored with data in memory. Each instruction is read from memory and placed in a control register to be executed. The document also outlines the basic registers used in a computer, including registers for holding instructions, data, memory addresses, and input/output. These registers are connected via a common bus system to transfer information between registers and memory.