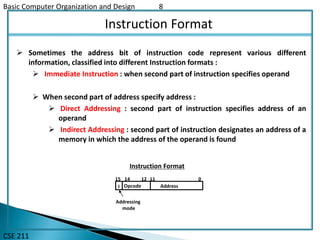

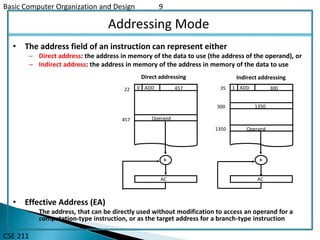

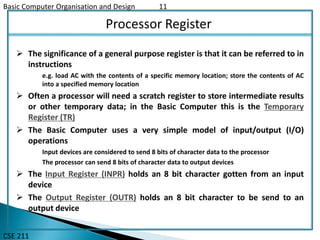

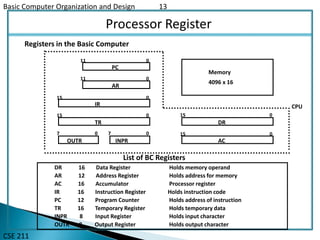

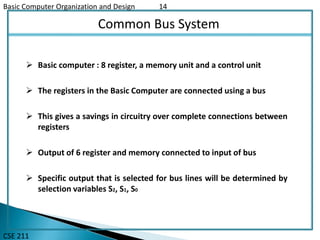

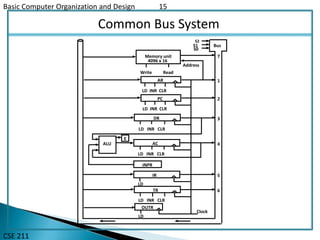

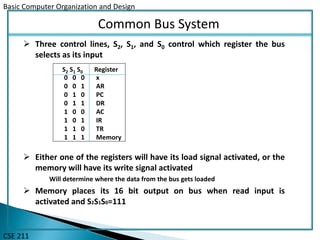

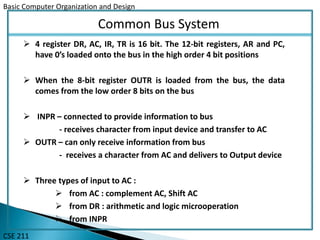

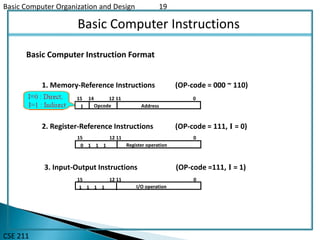

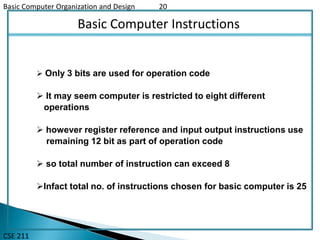

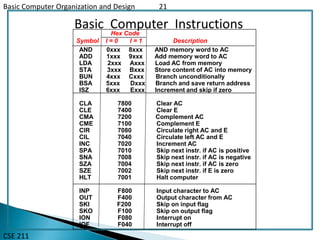

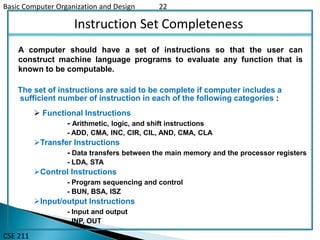

The document provides an overview of a course on basic computer organization and design. It describes the components of a basic computer including the processor, memory, registers, bus, and instruction set. The processor contains registers like the program counter, address register, data register, accumulator, and input/output registers. The memory can hold 4096 16-bit words. The instruction set includes memory reference, register reference, and input/output instructions that allow basic arithmetic, logic, branching, and I/O operations.