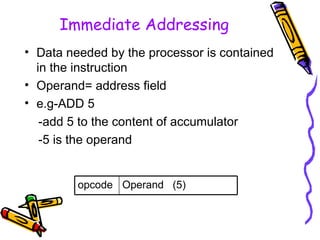

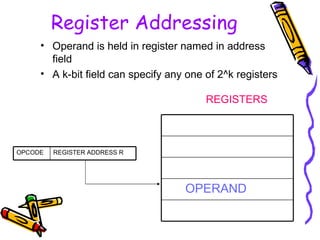

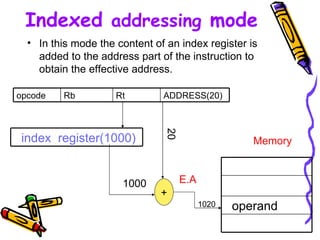

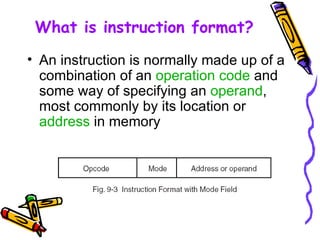

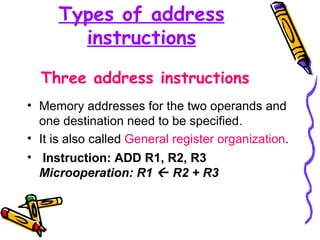

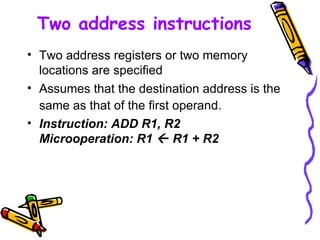

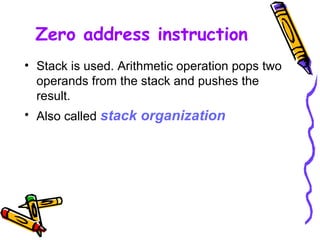

An instruction format specifies an operation code and operands. There are three main types of instruction formats: three address instructions specify memory addresses for two operands and one destination; two address instructions specify two memory locations or registers with the destination assumed to be the first operand; and one address instructions use a single accumulator register for all data manipulation. Addressing modes further specify how the address field of an instruction is interpreted to determine the effective address of an operand. Common addressing modes include immediate, register, register indirect, auto-increment/decrement, direct, indirect, relative, indexed, and base register addressing.

![EVALUATE X=(A+B)*(C+D) ADD R1, A, B R1 M[A]+M[B] ADD R2, C, D R2 M[C]+M[D] MUL X, R1, R2 M[X] R1*R2](https://image.slidesharecdn.com/instructionformat-110818112559-phpapp01/85/Instruction-format-4-320.jpg)

![EVALUATE X=(A+B)*(C+D) MOV R1, A R1 M[A] ADD R1, B R1 R1+M[B] MOV R2, C R2 M[C] ADD R2, D R2 R2+M[D] MUL R1,R2 R1 R1*R2 MOV X,R1 M[X] R1](https://image.slidesharecdn.com/instructionformat-110818112559-phpapp01/85/Instruction-format-6-320.jpg)

![One address instructions One address can be a register name or memory address. SINGLE ACCUMULATOR ORGANIZATION It uses AC register for all data manipulation Instruction: ADD X Microoperation: AC AC + M[X]](https://image.slidesharecdn.com/instructionformat-110818112559-phpapp01/85/Instruction-format-7-320.jpg)

![EVALUATE X=(A+B)*(C+D) LOAD A AC M[A] ADD B AC AC+M[B] STORE T M[T] AC LOAD C AC M[C] ADD D AC AC+M[D] MUL T AC AC*M[T] STORE X M[X] AC](https://image.slidesharecdn.com/instructionformat-110818112559-phpapp01/85/Instruction-format-8-320.jpg)

![Zero address instruction Evaluate X = ( A +B ) * ( C +D ) PUSH A TOS A PUSH B TOS B ADD TOS (A+B) PUSH C TOS C PUSH D TOS D ADD TOS (C+D) MUL TOS (C+D)*(A+B) POP X M[X] TOS Store Mult ADD Push D Push C ADD Push B Push A](https://image.slidesharecdn.com/instructionformat-110818112559-phpapp01/85/Instruction-format-10-320.jpg)