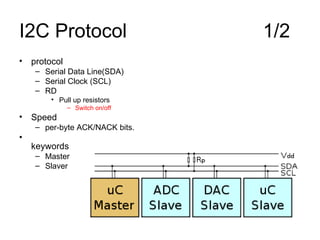

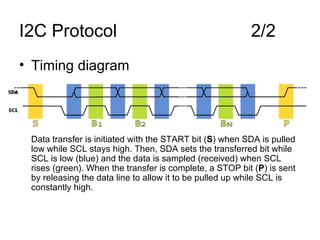

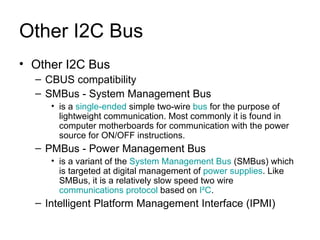

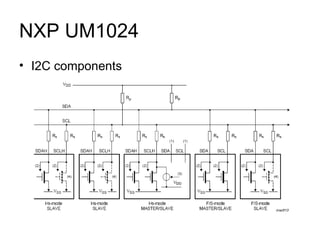

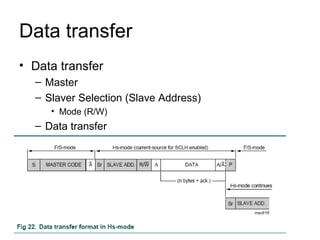

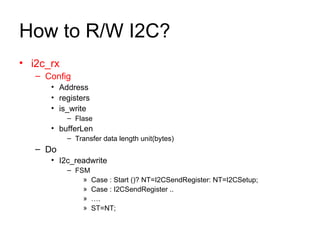

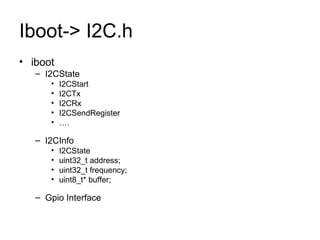

The document discusses the I2C (Inter-Integrated Circuit) protocol, which is a serial communication standard used to connect low-speed peripherals to embedded systems and other devices. It describes the basic I2C protocol including data transfer methods, components, and modes. It also provides code examples from an iBoot project that implement I2C read and write functionality using registers, state machines, and GPIO interfaces.

![Iboot-> I2C.c iBoot->I2C / 2 I2C Bus i2c_setup clock_gate_switch(I2C0_CLOCKGATE, ON); init_i2c(&I2C[0], FrequencyBasePeripheral); settings Frequency; divisorRequired; Prescaler; gpio_custom_io; Methods I2CError i2c_rx ( int bus, int iicaddr, const uint8_t* registers, int num_regs, void* buffer, int len); I2CError i2c_tx (int bus, int iicaddr, void* buffer, int len);](https://image.slidesharecdn.com/i2c-100513045613-phpapp02/85/I2-c-11-320.jpg)