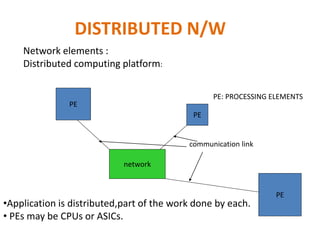

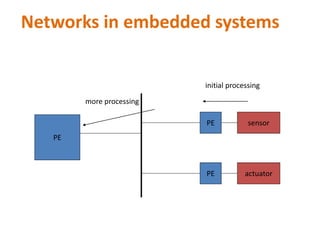

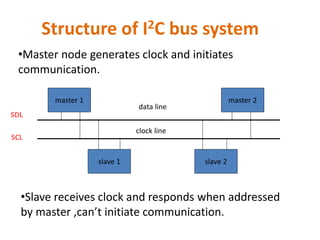

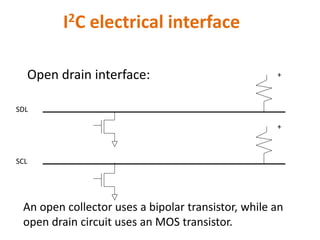

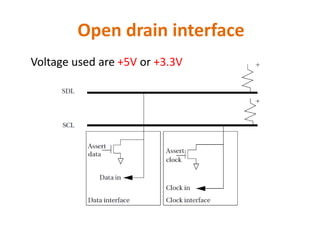

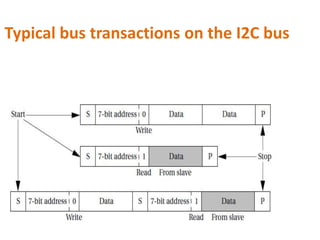

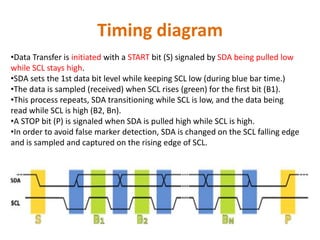

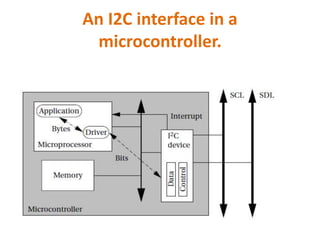

This document discusses the I2C bus which is commonly used to link microcontrollers into industrial control systems. It provides an overview of the key aspects of the I2C bus including its structure, electrical interface using an open drain configuration, physical protocol using start and stop sequences, device addressing, and typical bus transactions. The I2C bus allows for communication between processing elements that may be physically separated, enabling improved debugging and diagnosis of issues across a distributed network.