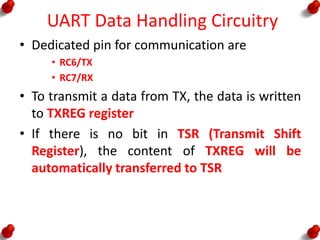

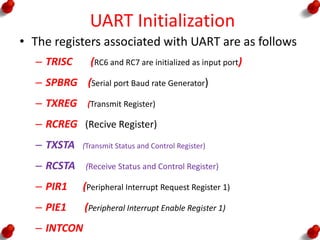

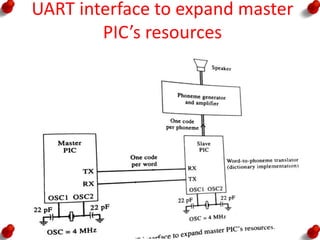

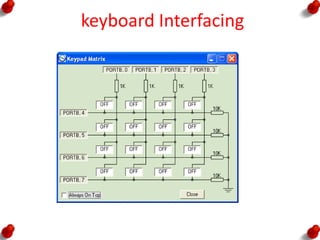

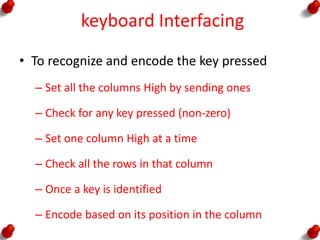

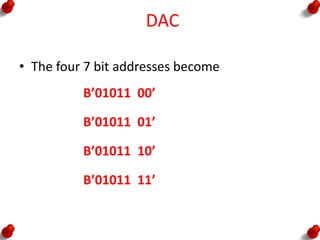

This document provides an overview of peripherals and interfacing using various communication protocols. It discusses the I2C bus protocol for accessing peripheral chips. It covers the operation of the I2C bus including start/stop bits and acknowledgement. It then summarizes the use of various peripherals that interface using I2C including EEPROM, analog to digital converters, LCDs, and sensors. It also covers serial communication protocols like UART and interfacing for devices like keyboards.