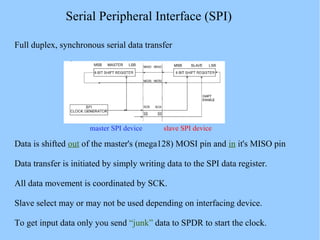

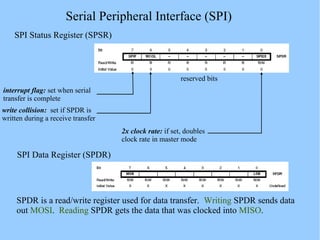

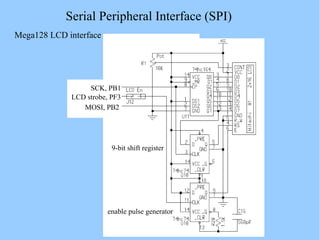

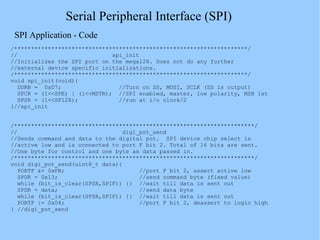

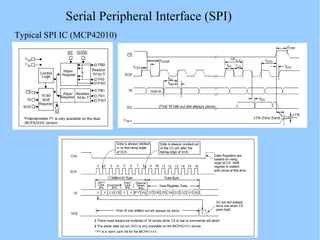

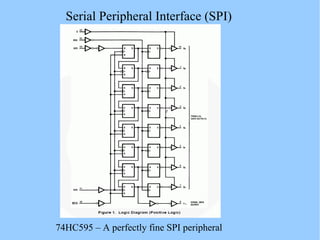

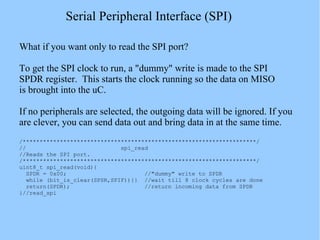

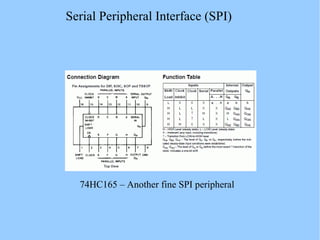

The document describes the Serial Peripheral Interface (SPI) protocol which allows for full duplex synchronous serial communication between a master and slave device using 4 pins - MOSI, MISO, SCK, and an optional SS pin. It details the SPI registers for control, status, and data and provides examples of SPI communication with peripherals like digital pots and shift registers. Common issues like conflicts with programming interfaces and ensuring proper chip select signaling are also covered.