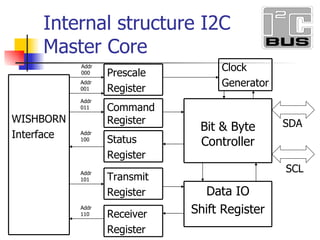

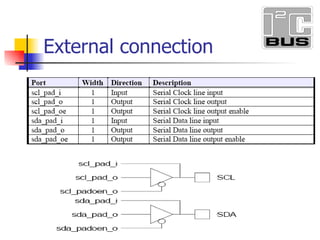

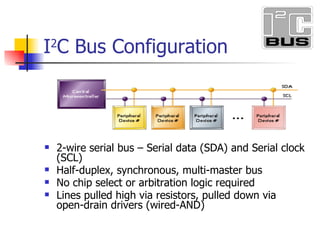

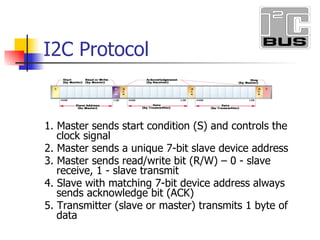

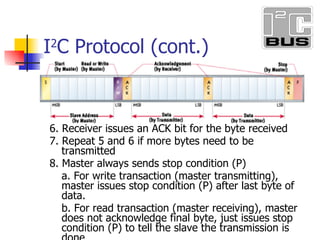

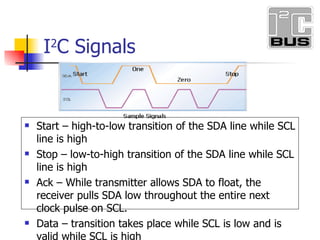

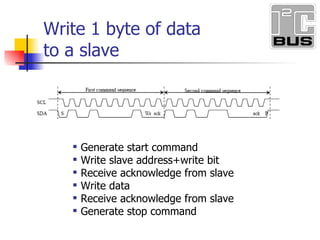

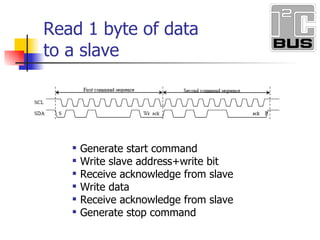

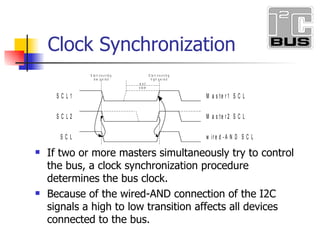

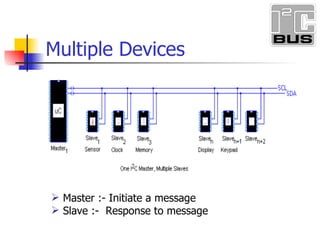

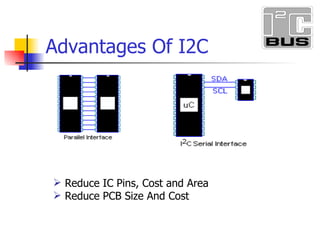

I2C is a serial communication protocol used to connect low-speed peripherals to processors and microcontrollers. It was developed by Philips in the 1980s for use in televisions. I2C uses just two bidirectional open-drain lines: serial data line (SDA) and serial clock line (SCL). Devices can operate as master or slave devices and have a 7-bit address. Communication is initiated by the master which controls the clock signal. Data is transferred in one byte packets with acknowledgement from the receiver.