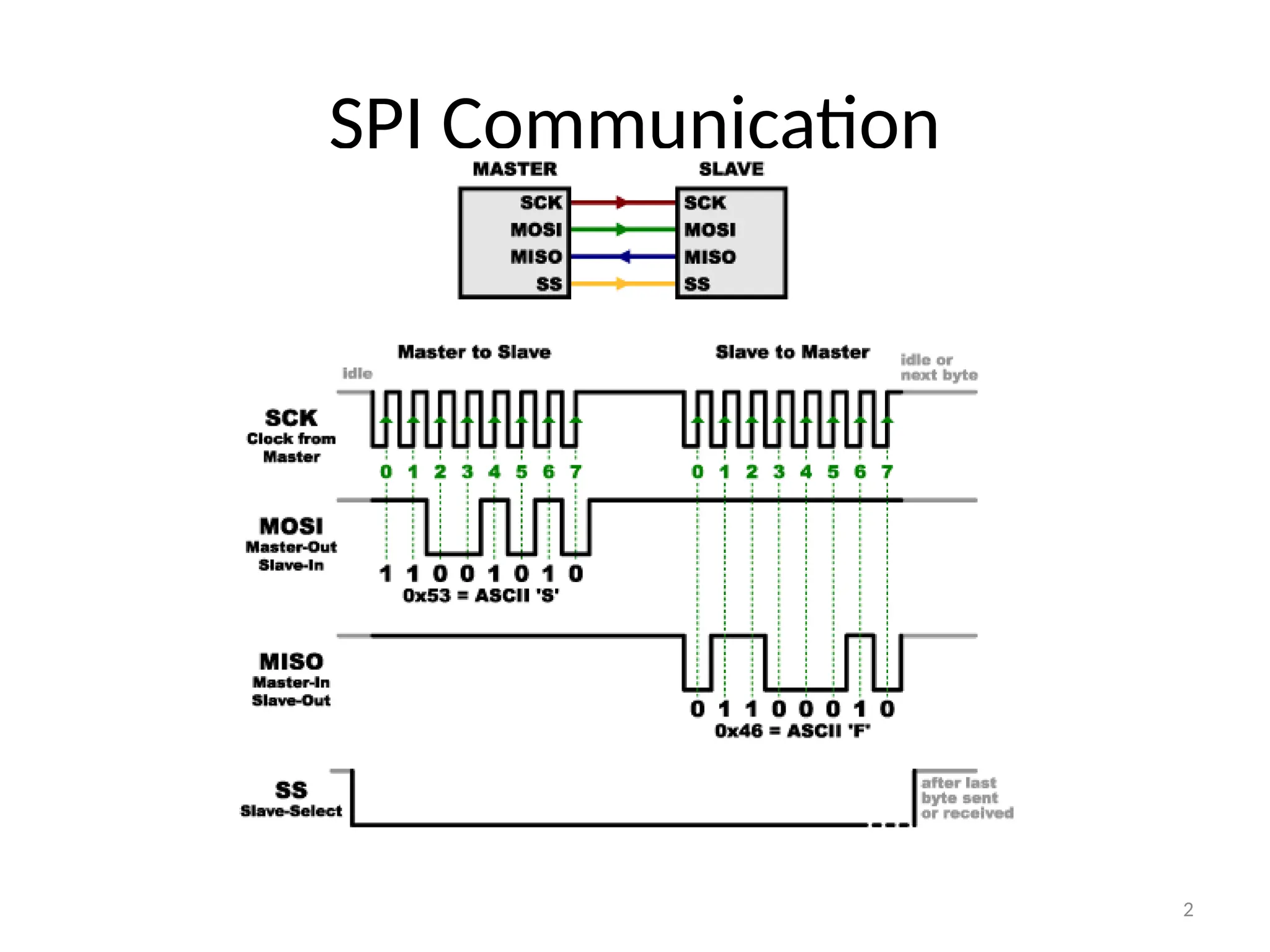

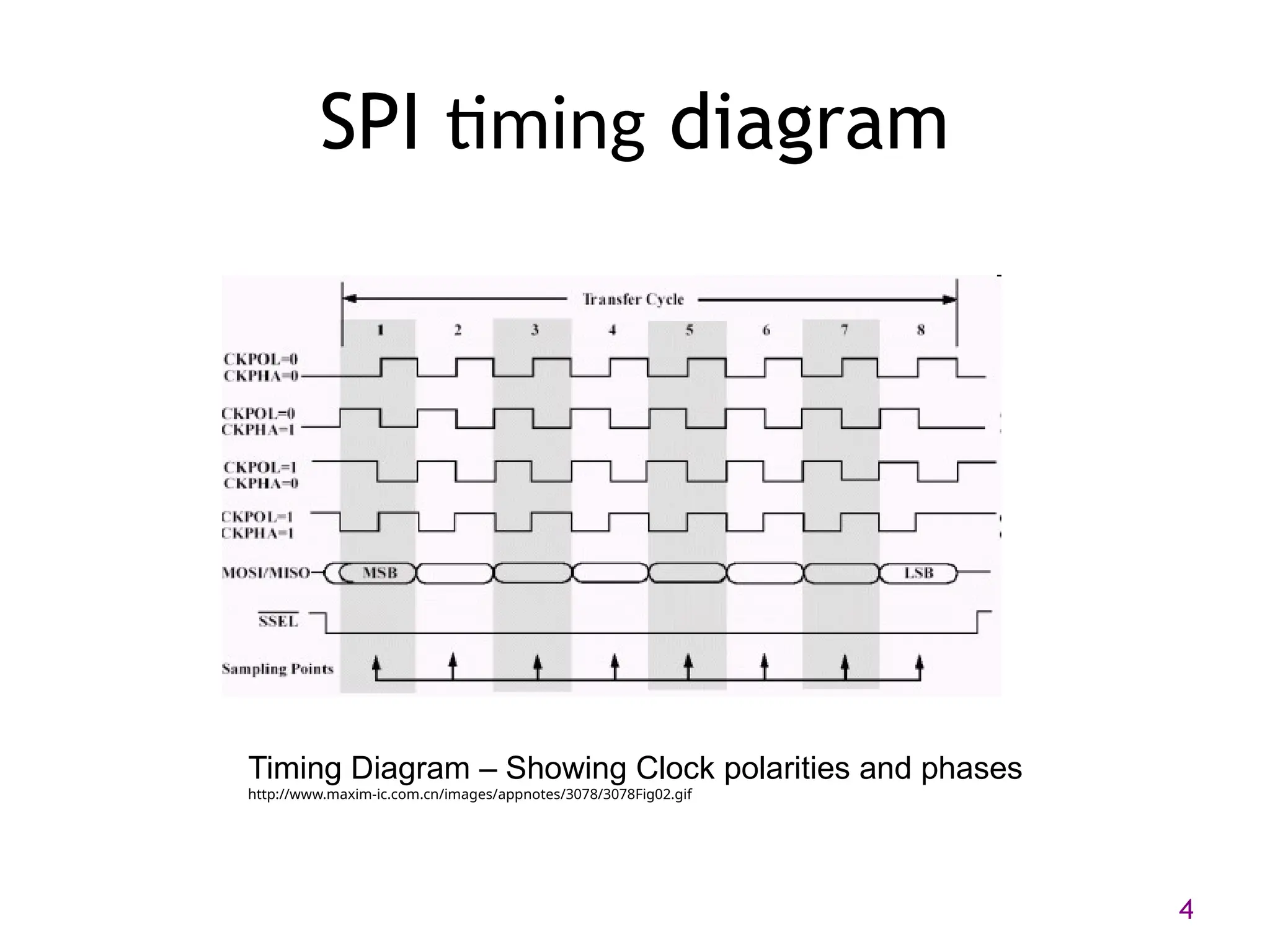

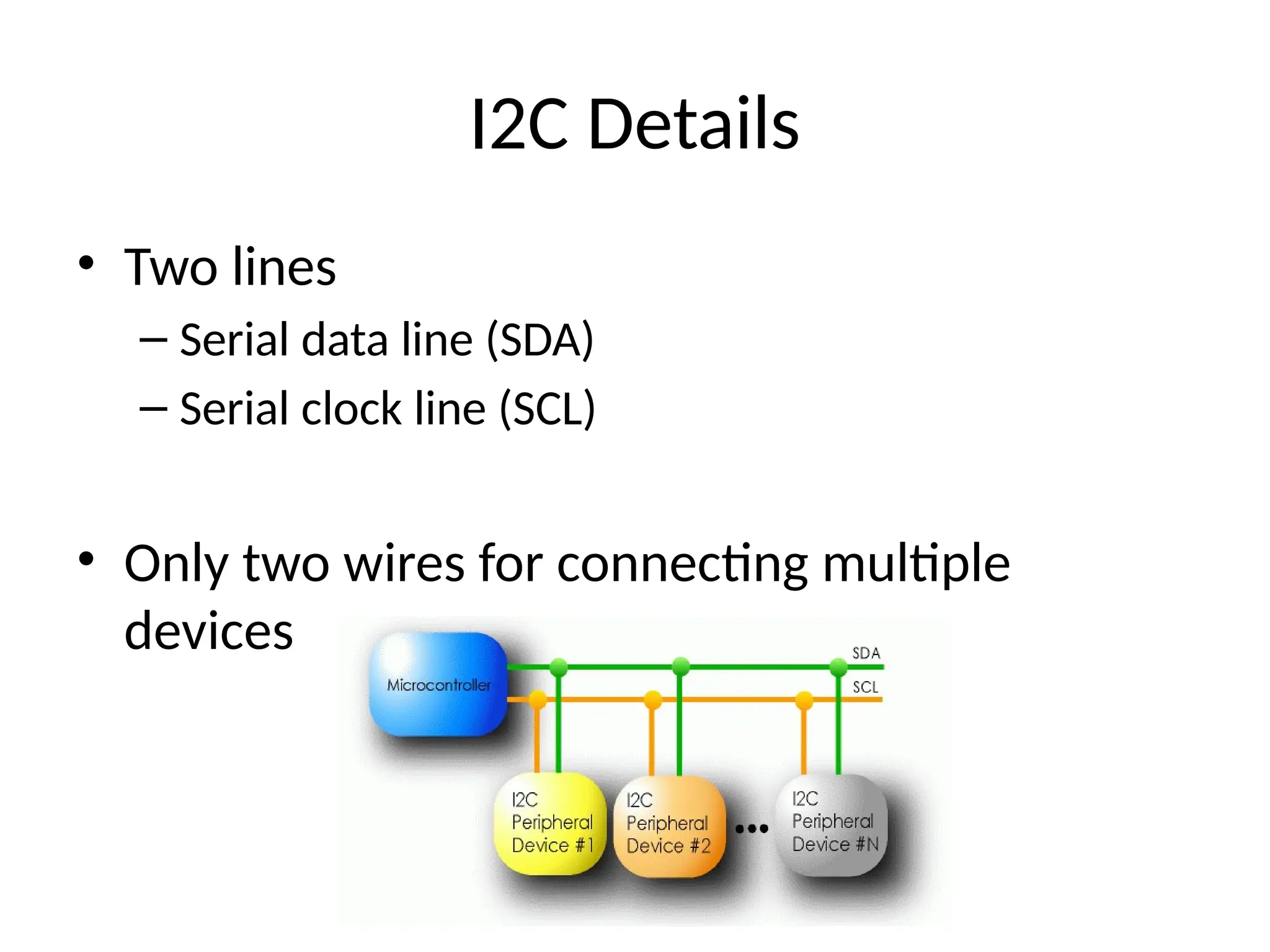

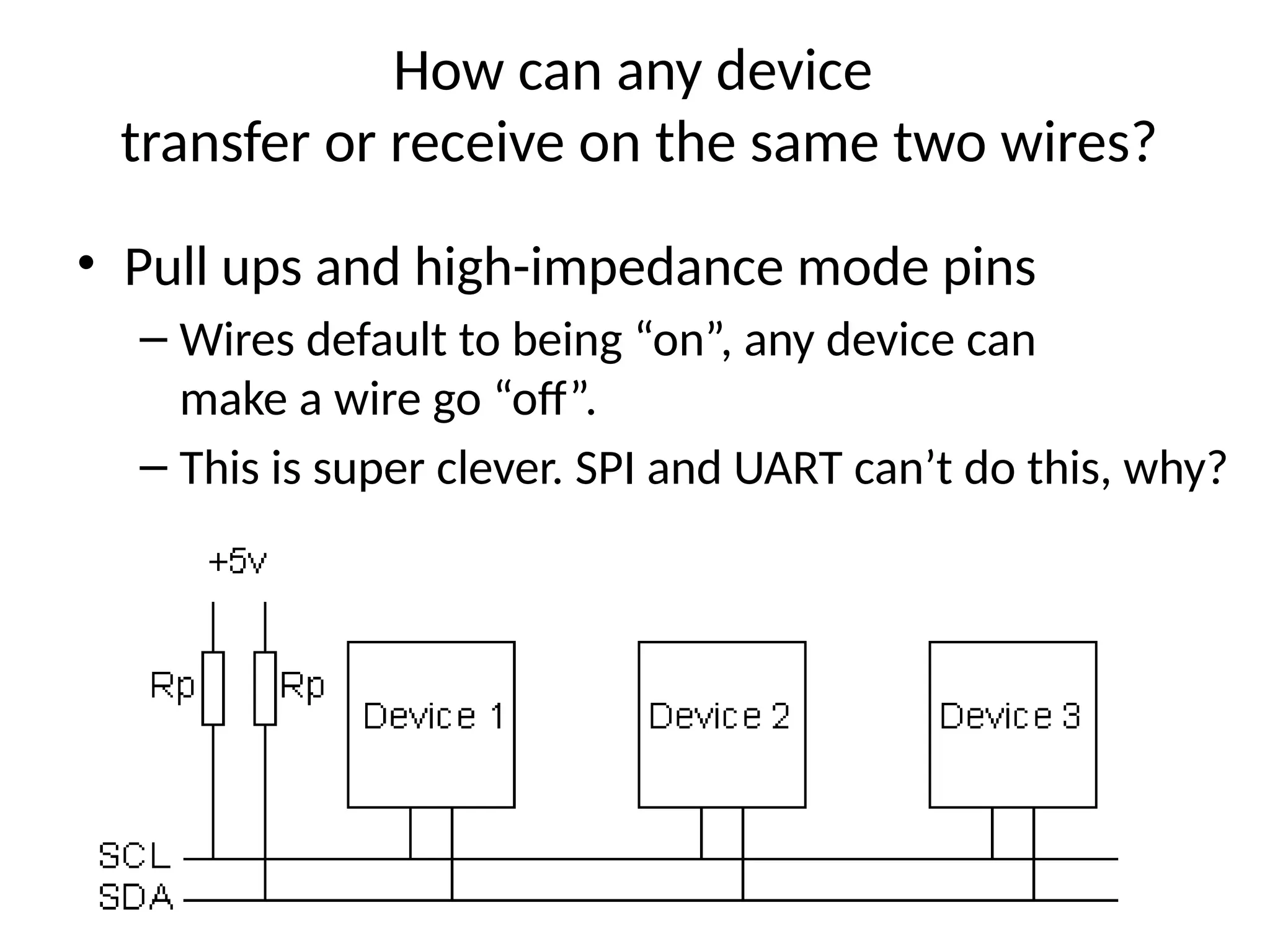

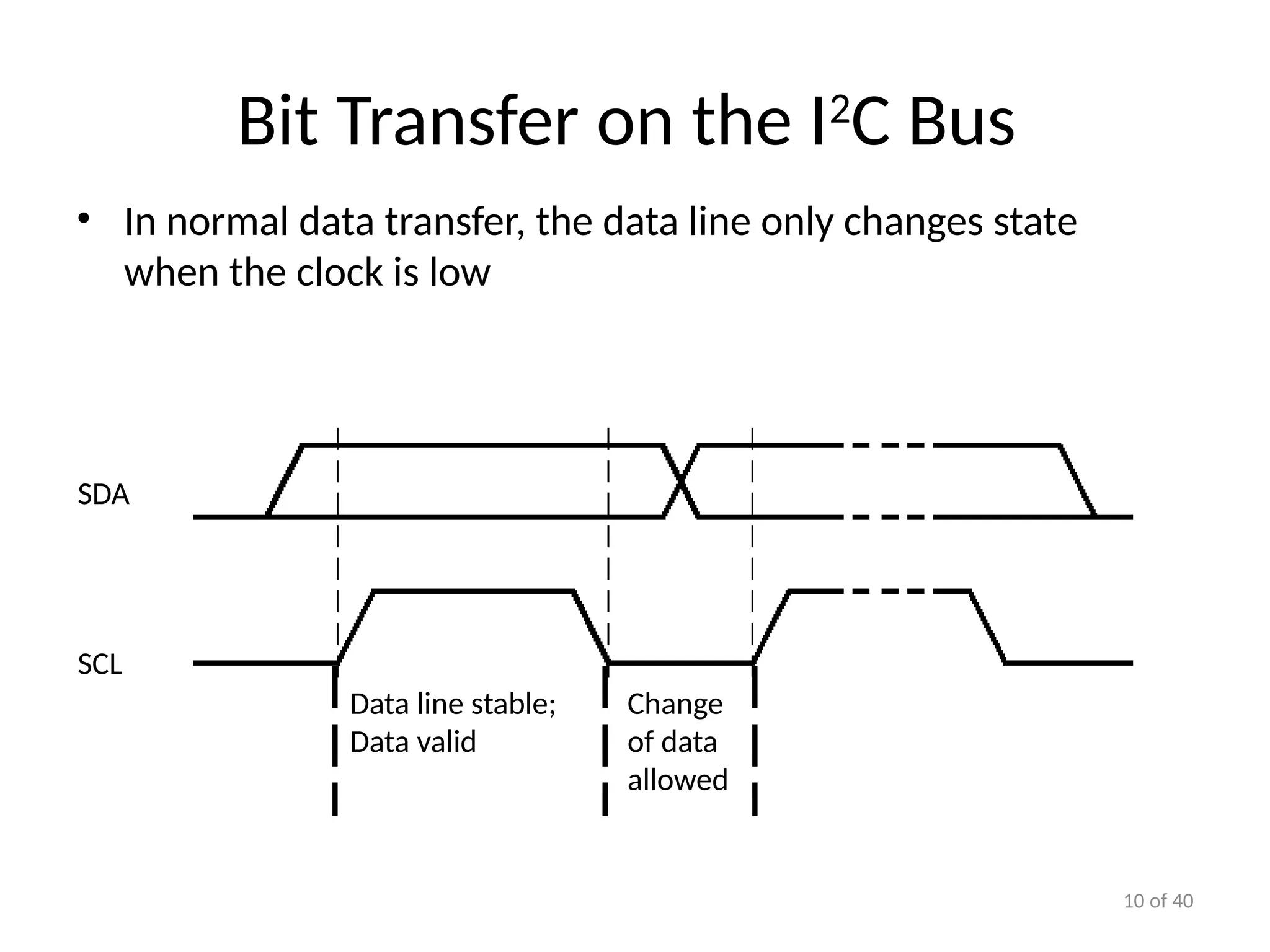

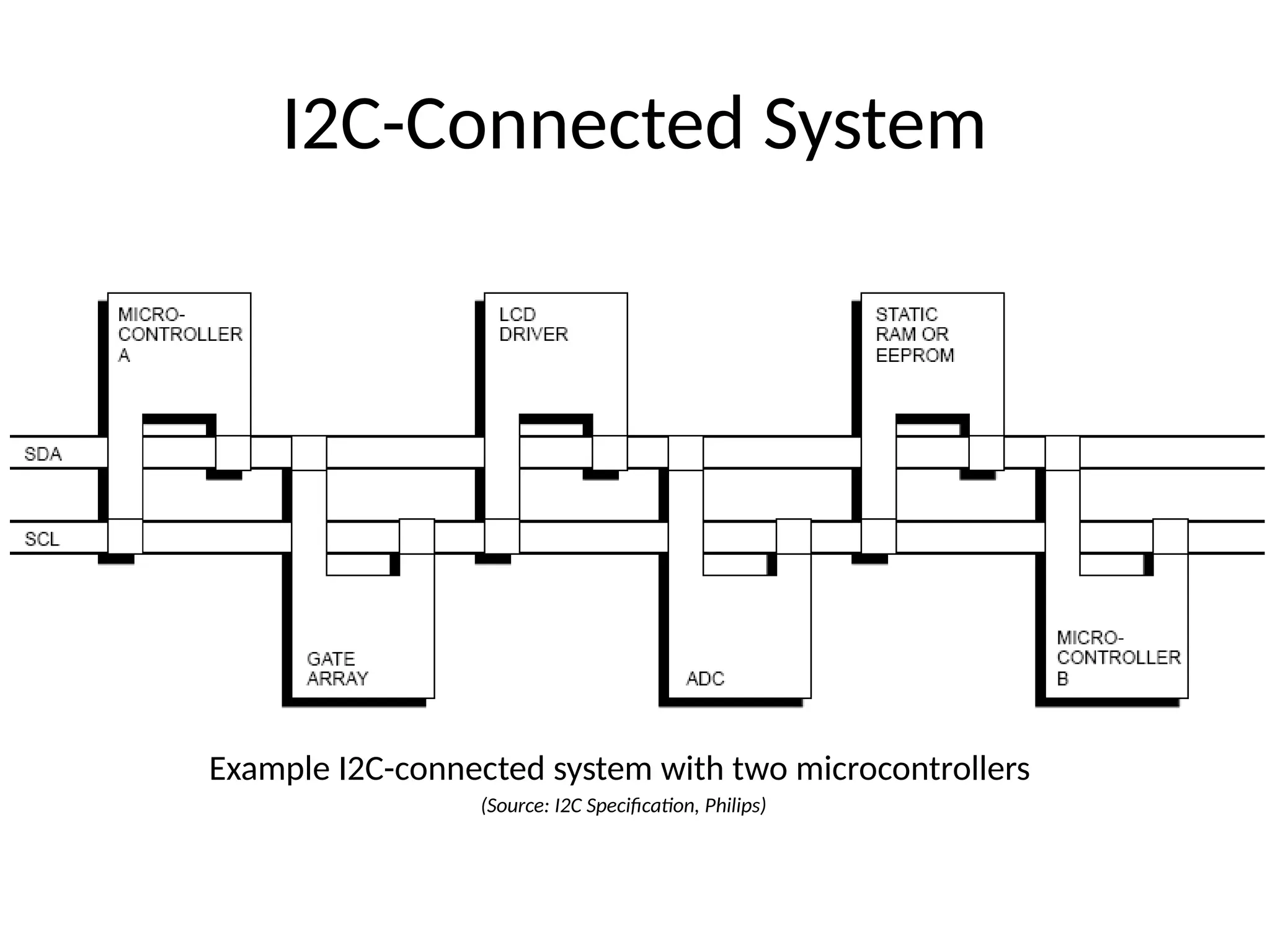

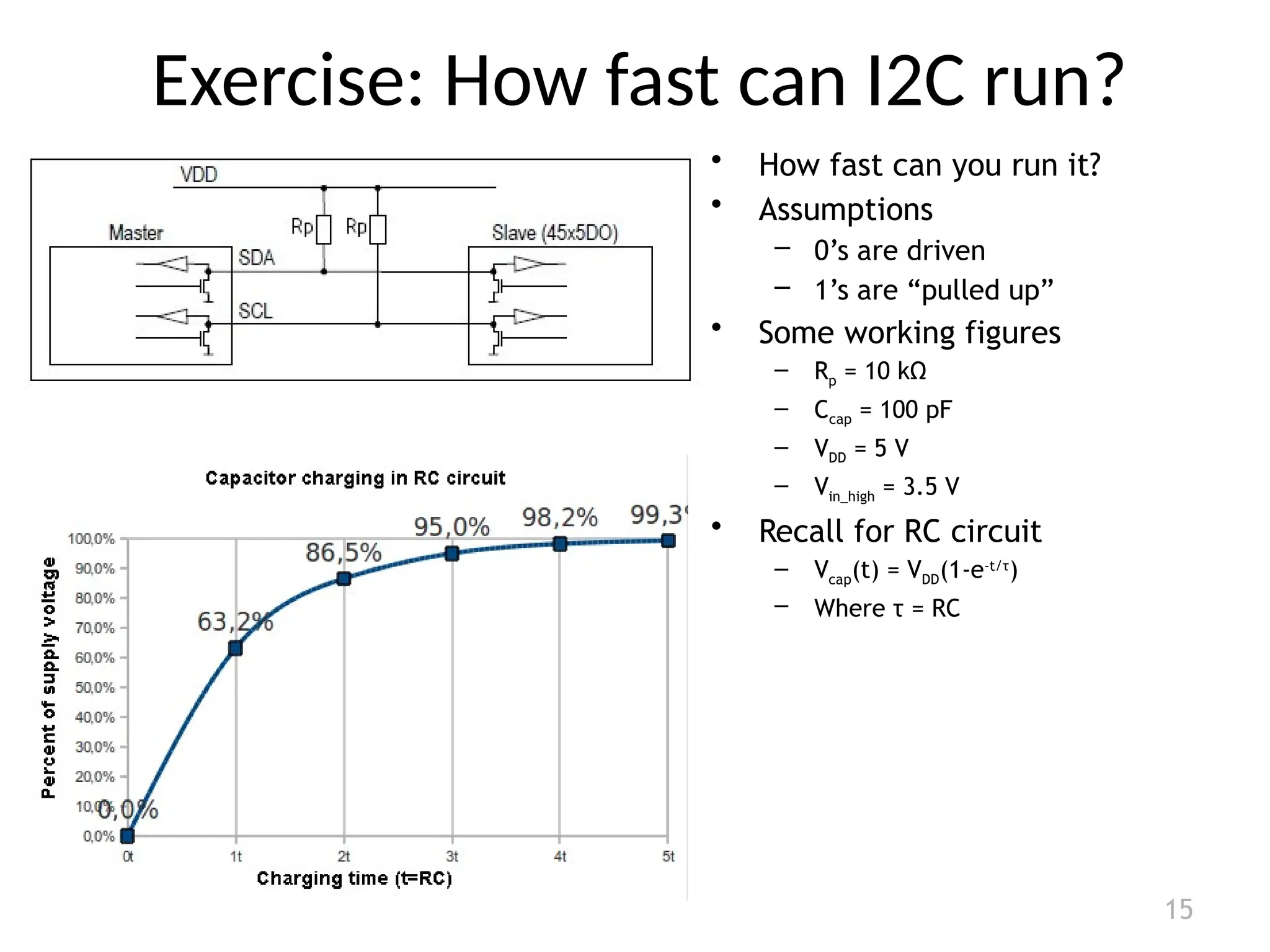

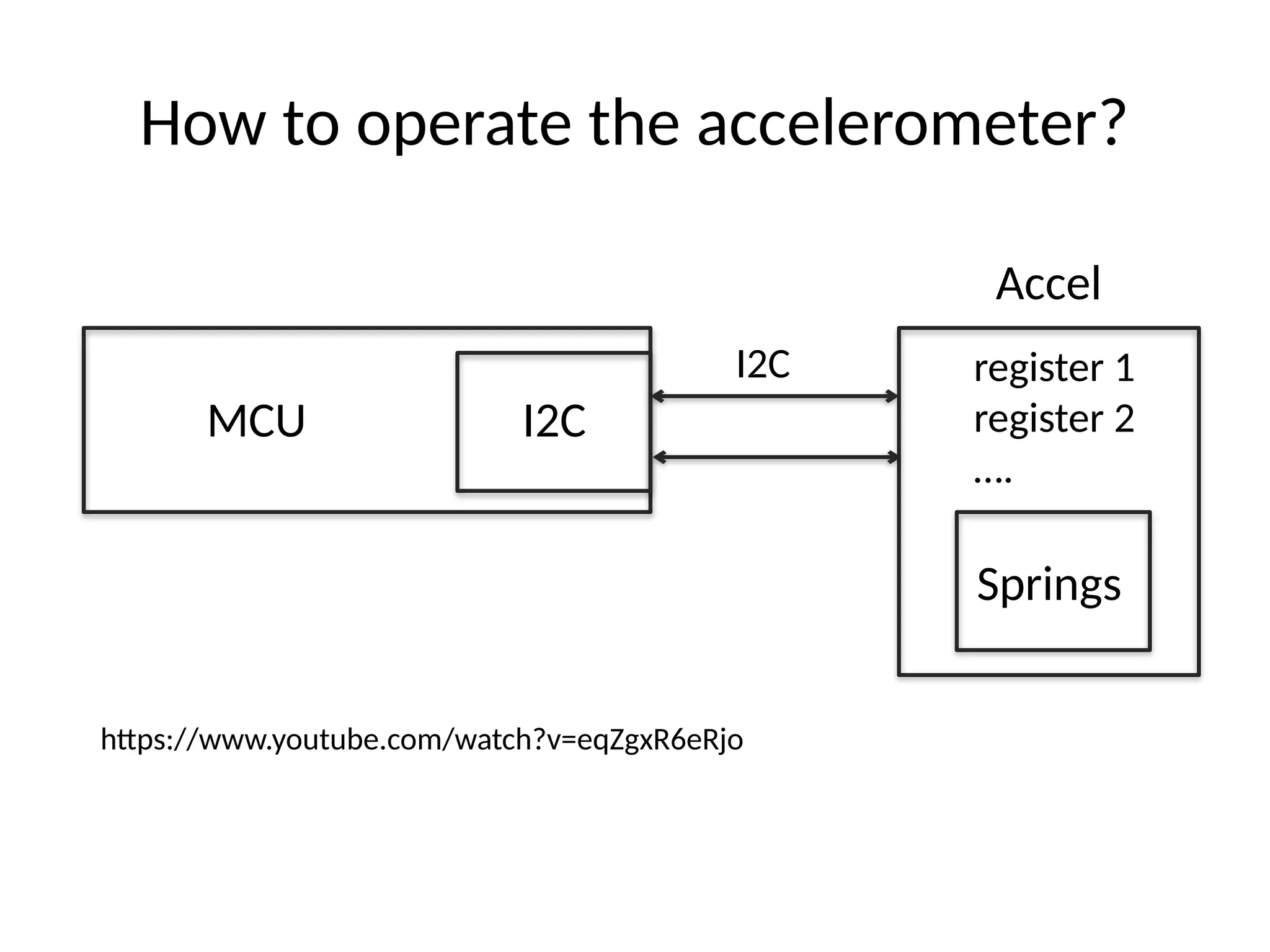

The document discusses communication protocols SPI and I2C for wireless embedded systems, highlighting their characteristics, pros, and cons. SPI is noted for its speed and simplicity in point-to-point connections but faces complications with multiple slaves and lacks acknowledgment and arbitration features. In contrast, I2C utilizes two wires for multiple device connections but comes with higher overhead and slower speeds, featuring a unique addressing system for devices involved in data transfers.