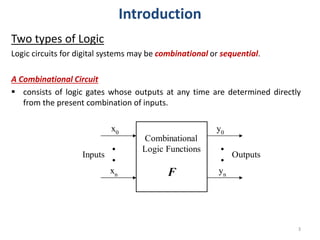

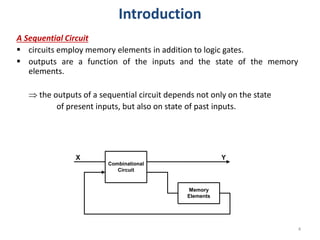

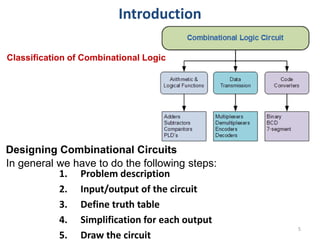

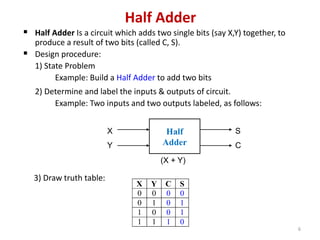

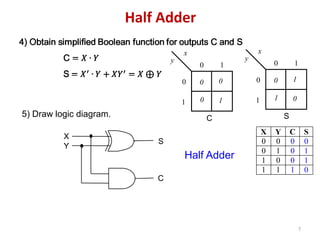

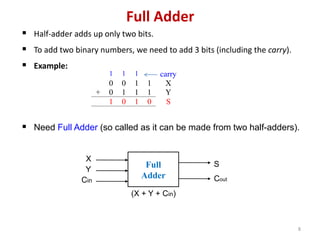

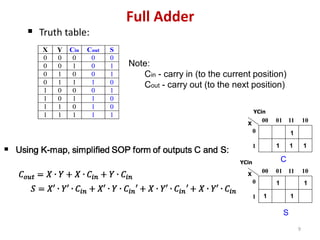

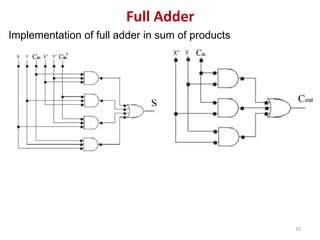

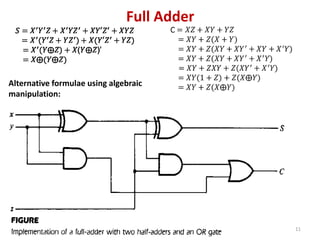

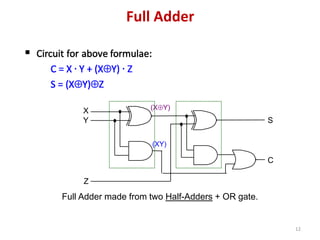

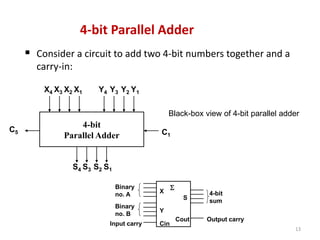

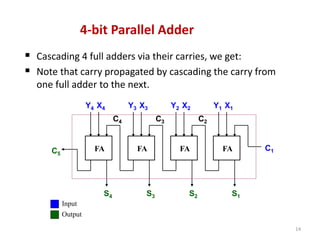

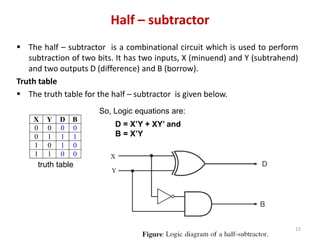

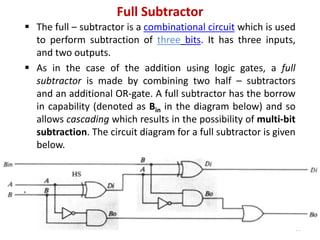

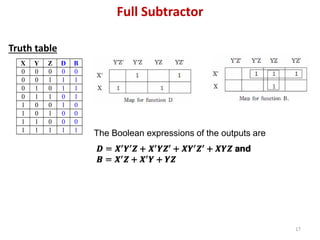

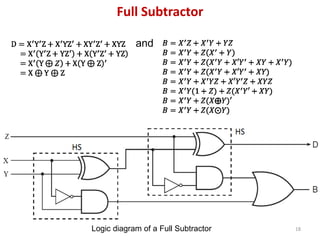

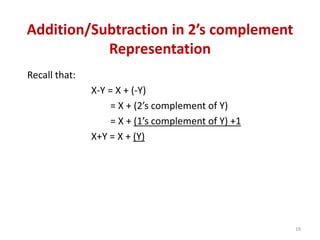

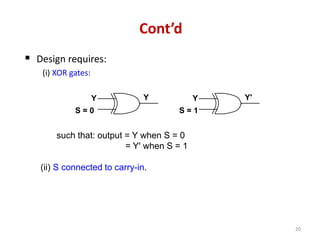

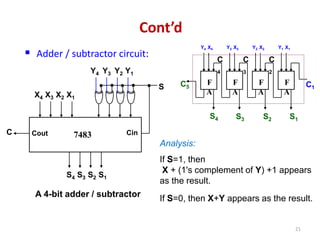

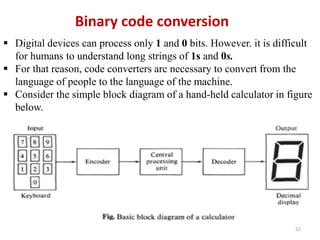

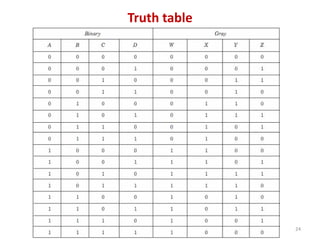

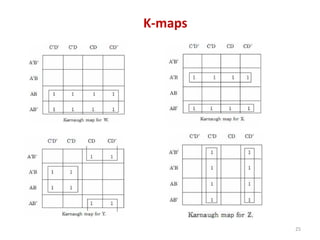

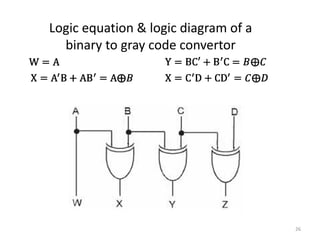

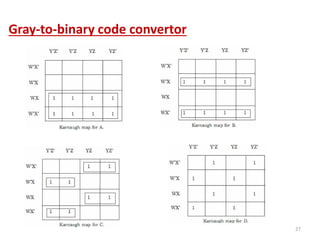

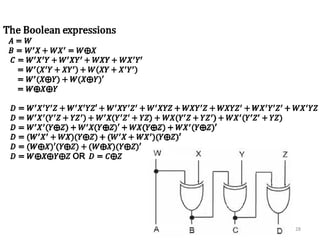

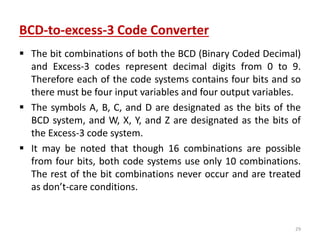

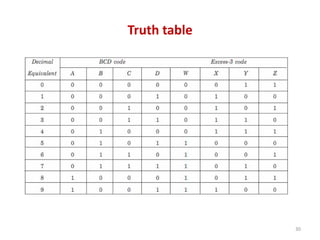

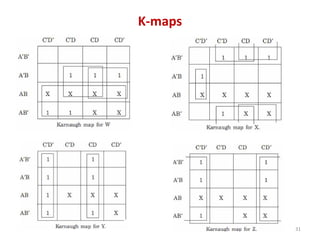

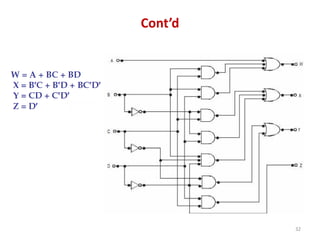

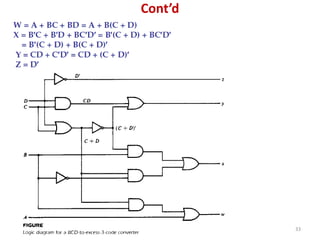

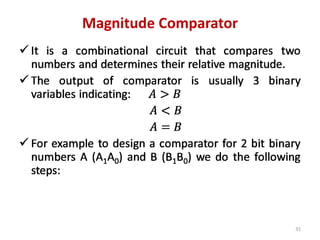

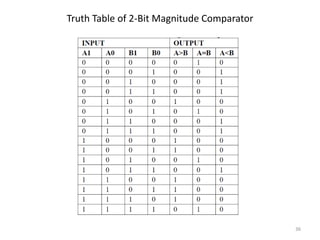

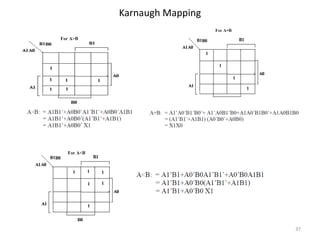

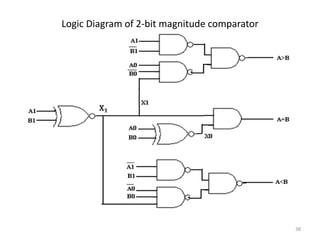

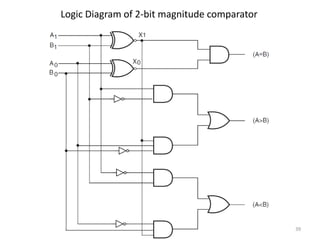

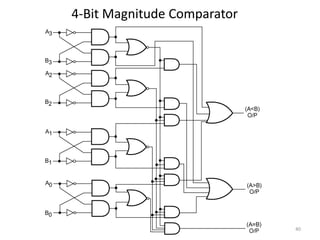

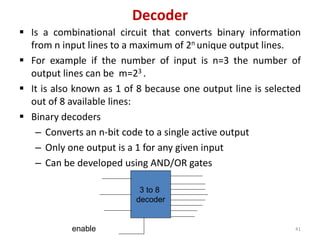

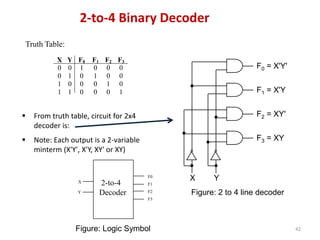

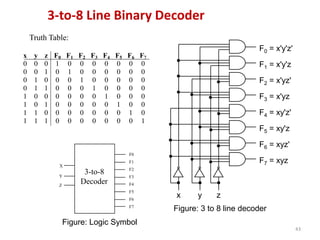

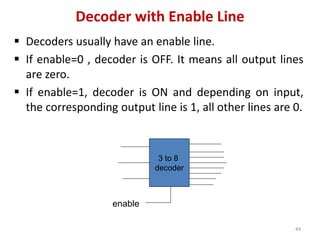

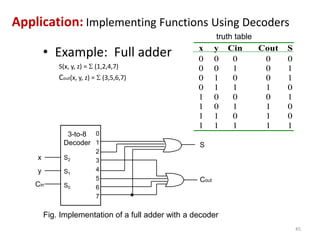

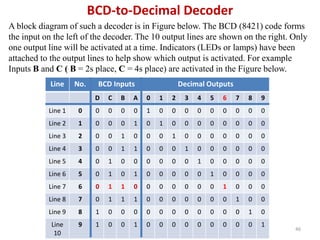

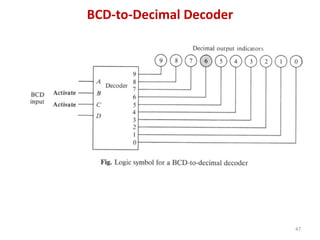

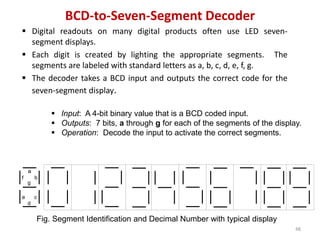

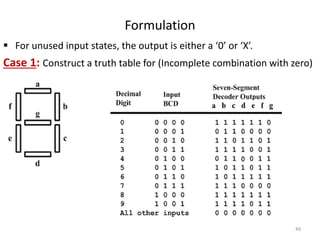

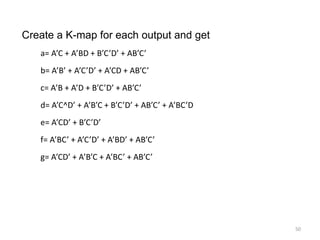

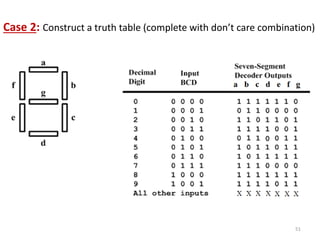

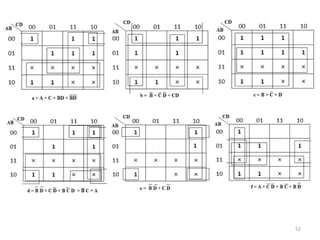

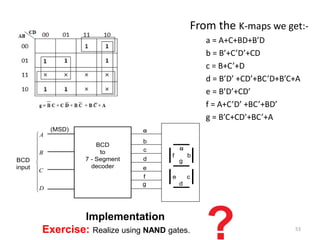

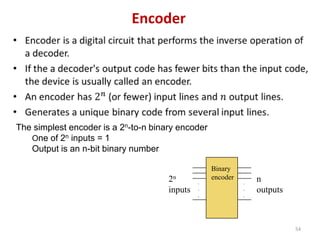

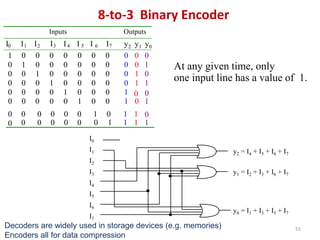

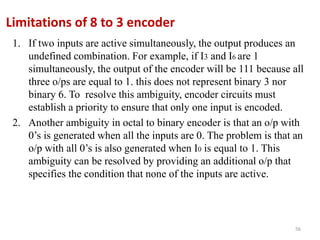

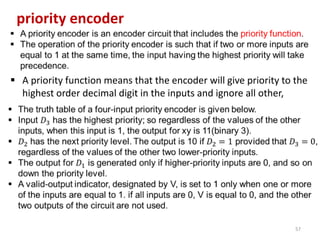

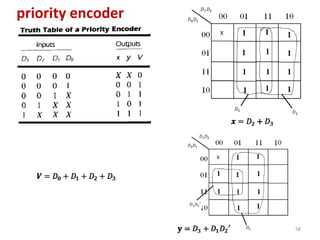

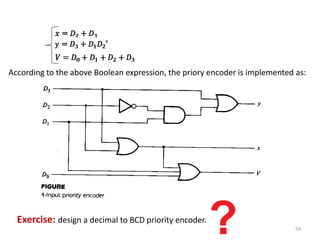

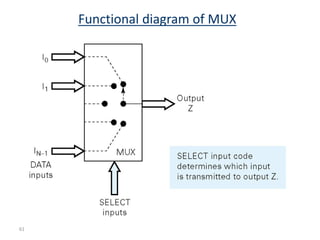

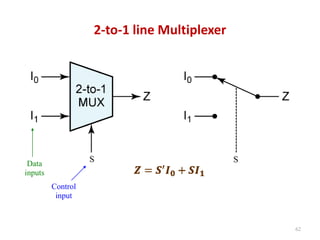

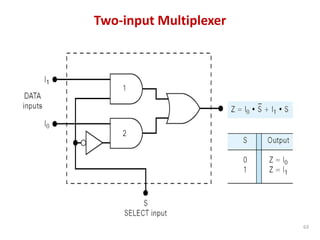

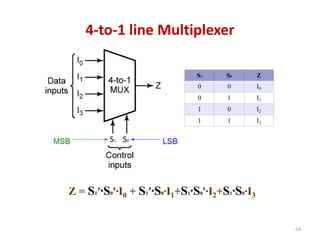

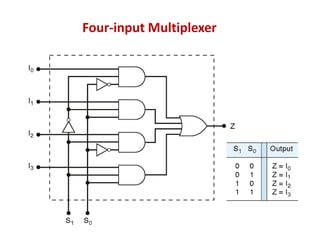

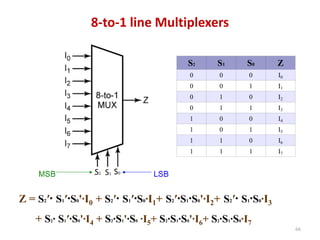

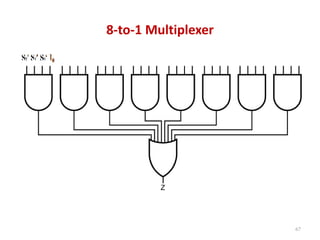

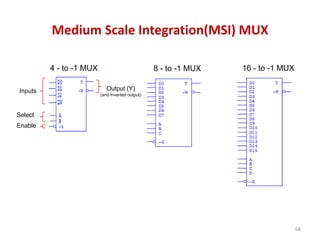

This document discusses combinational circuit design and provides examples of various combinational logic circuits. It begins with an introduction that defines combinational and sequential circuits. The remainder of the document provides details on specific combinational logic circuits including half adders, full adders, subtractors, encoders, decoders, multiplexers, comparators, and code converters. Worked examples are provided for each circuit type using truth tables, Karnaugh maps, and logic diagrams. Applications of decoders for implementing functions like a full adder are also described.