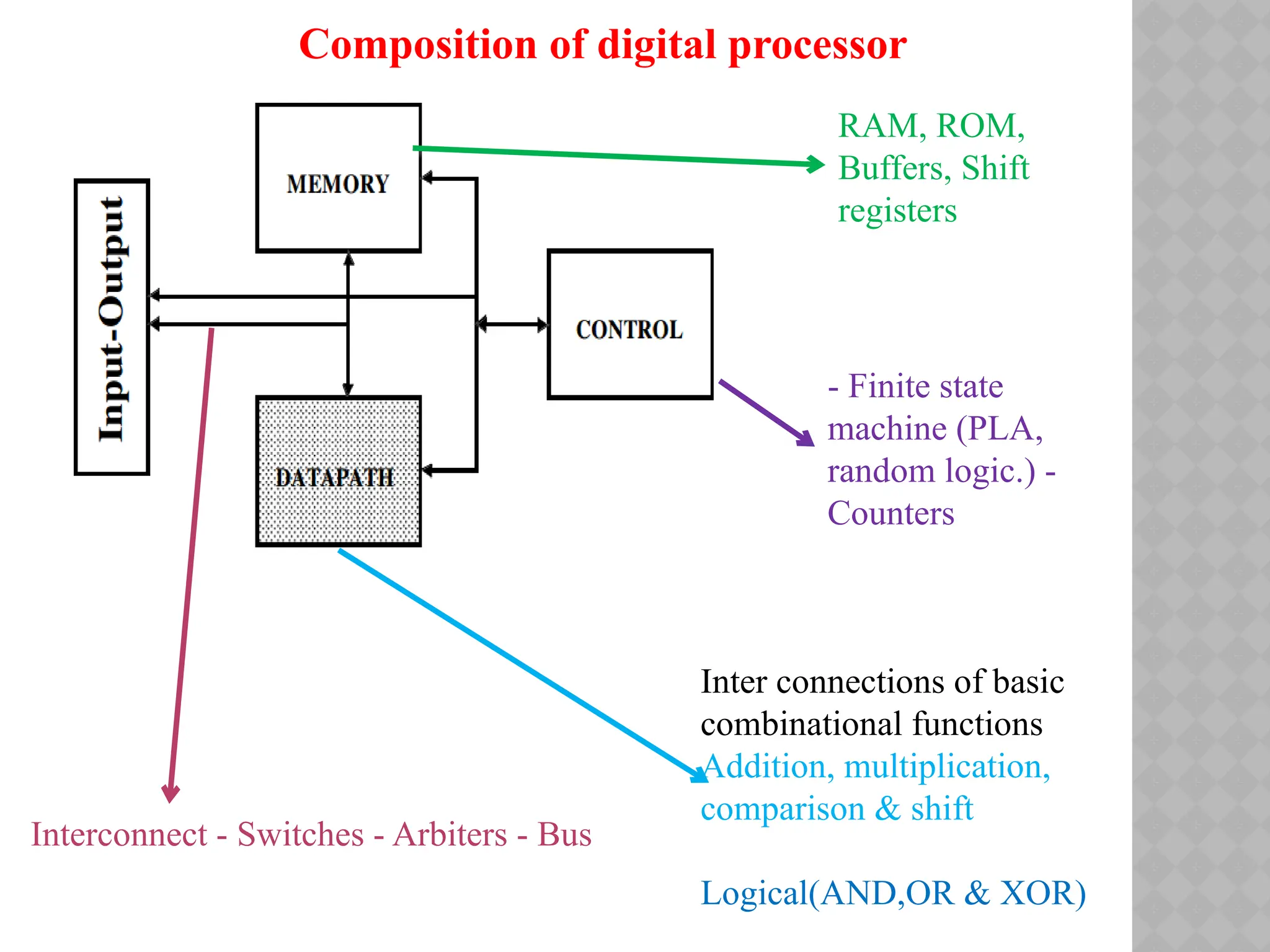

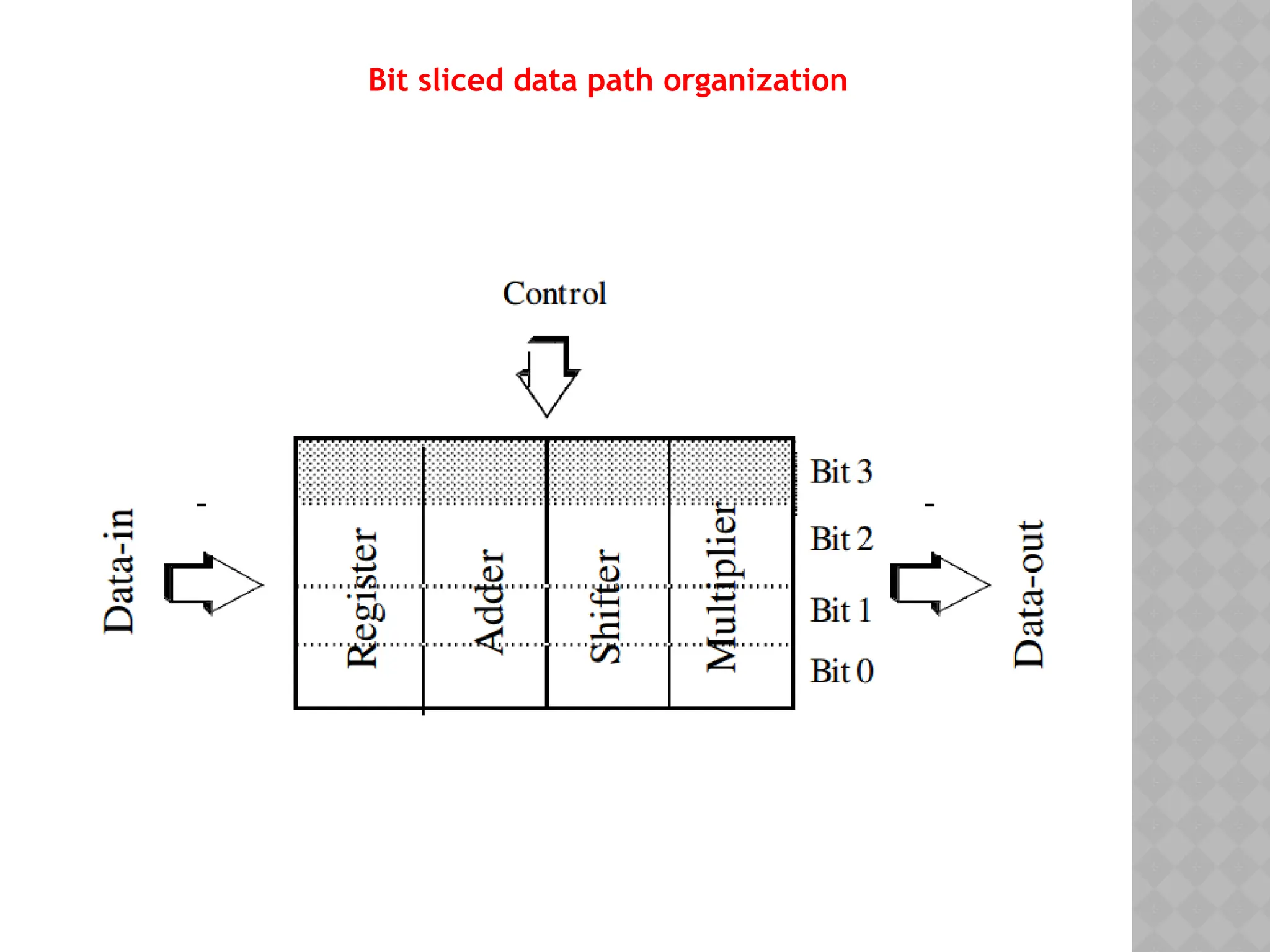

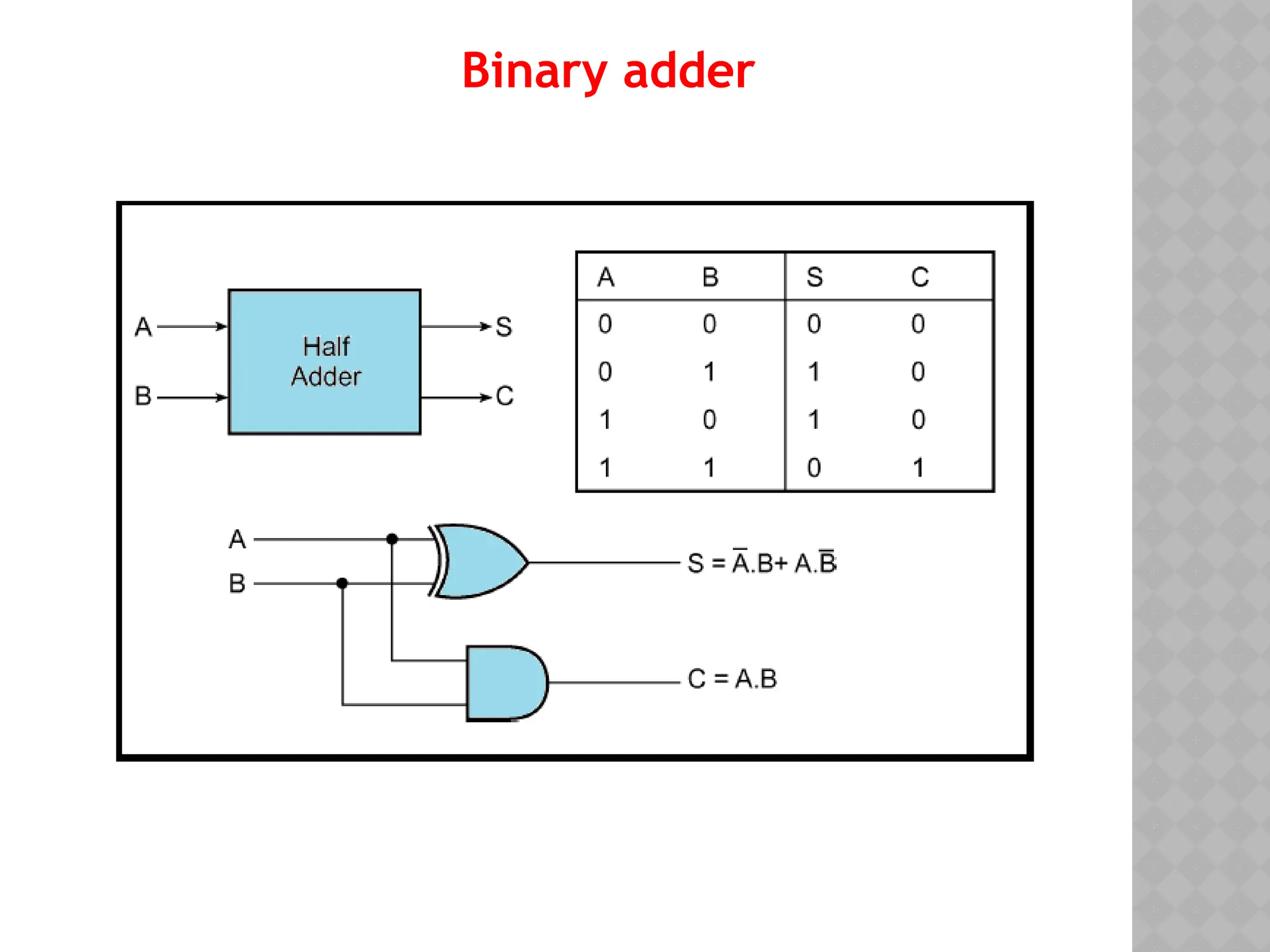

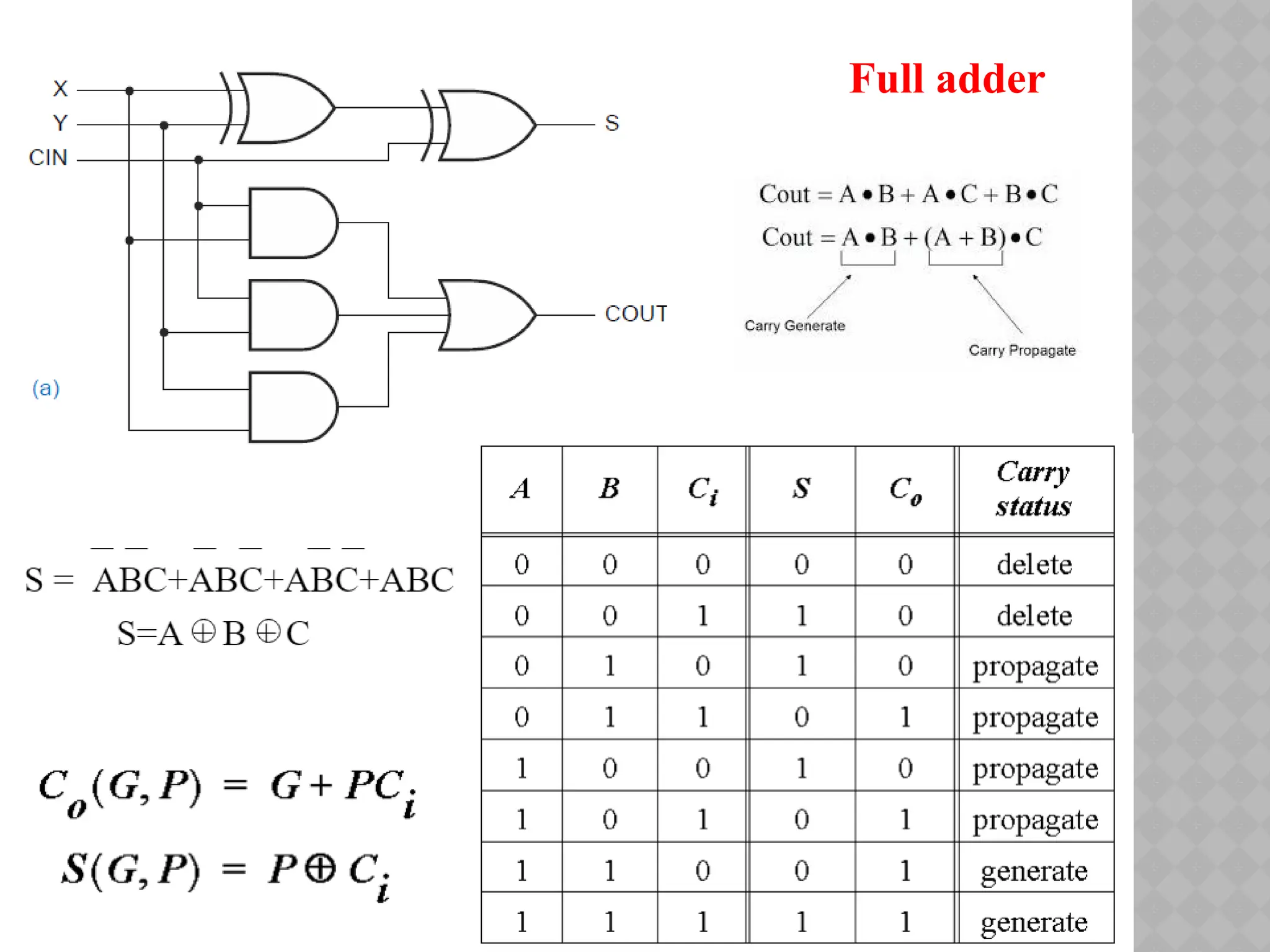

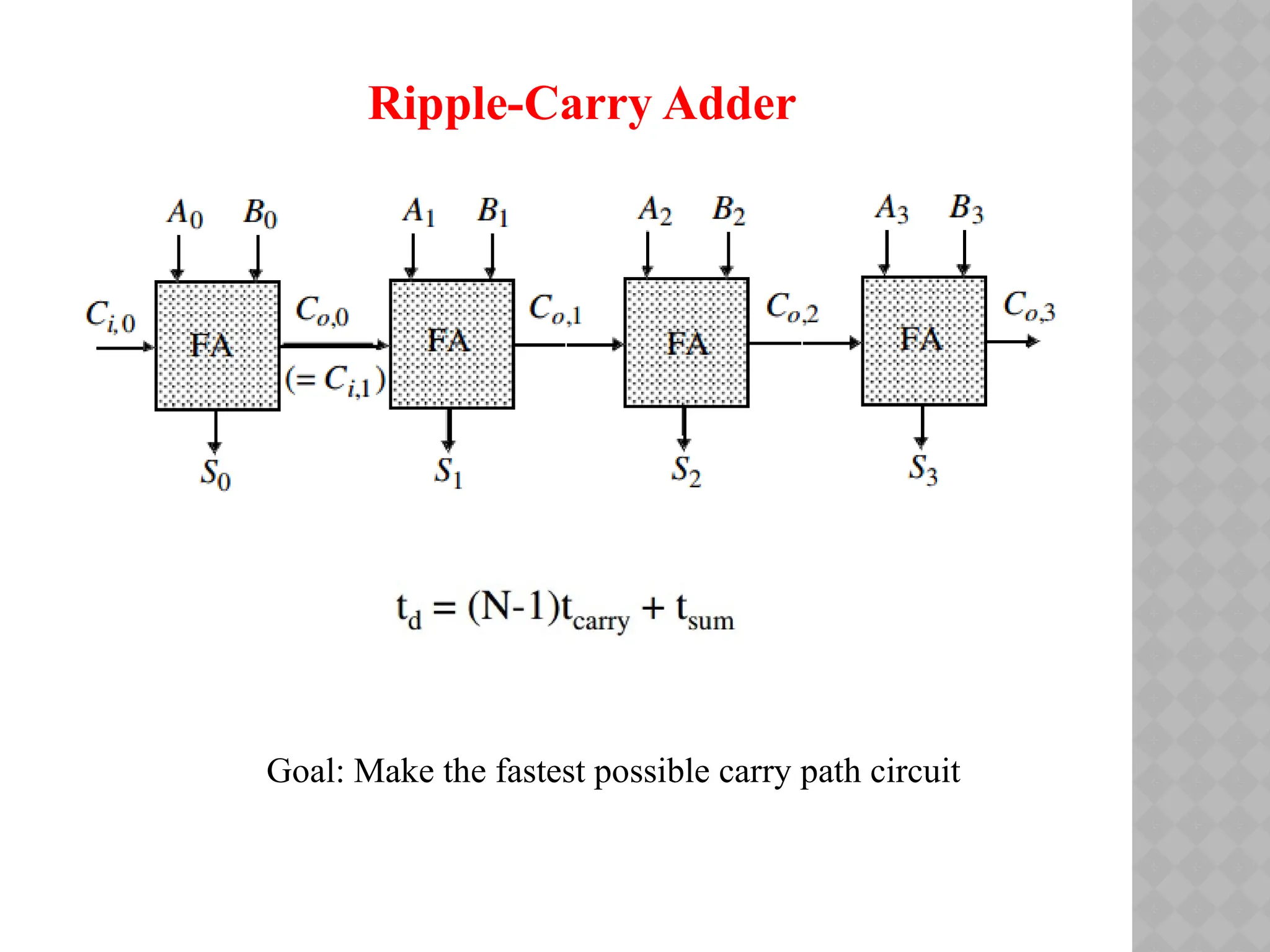

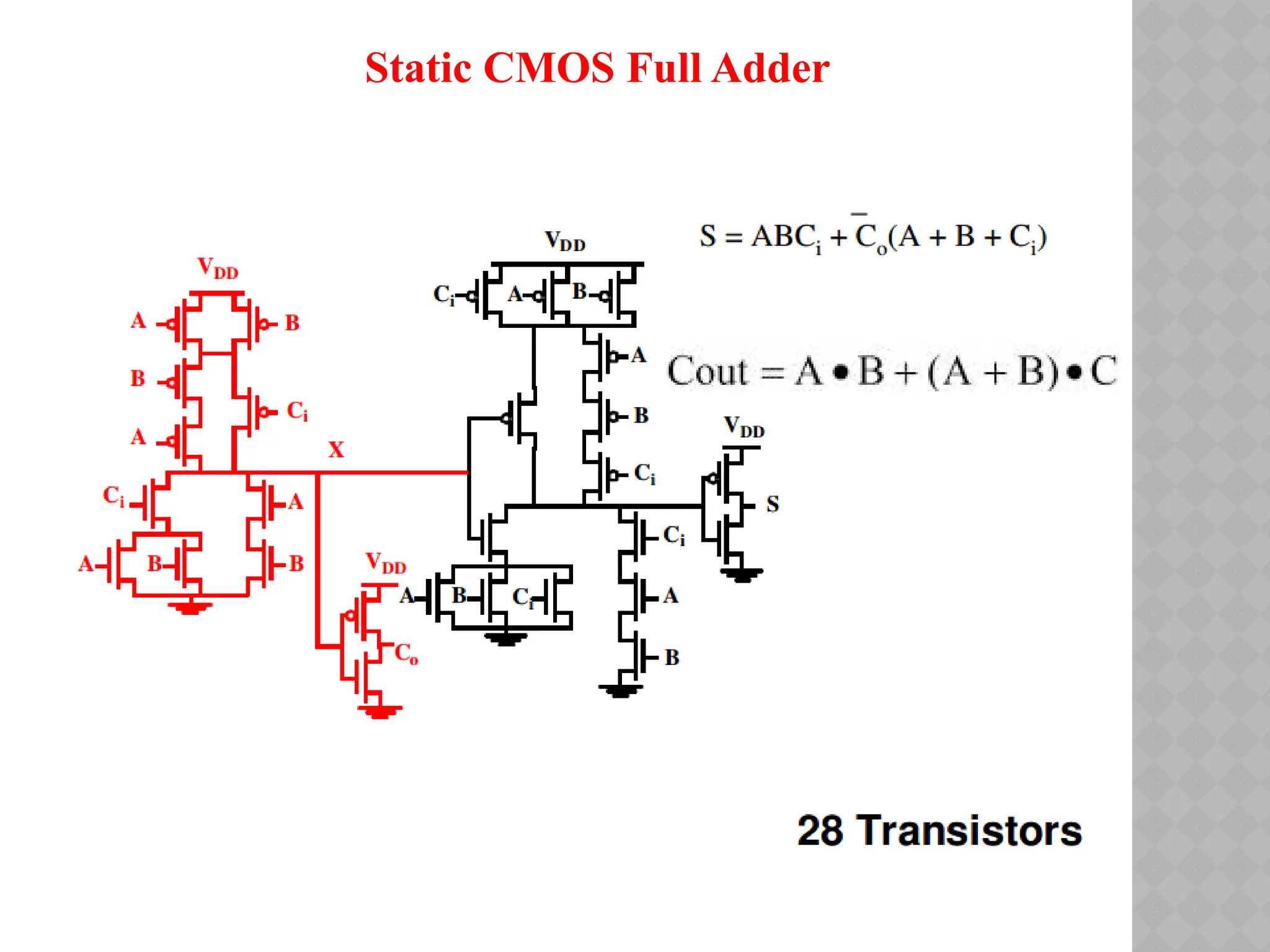

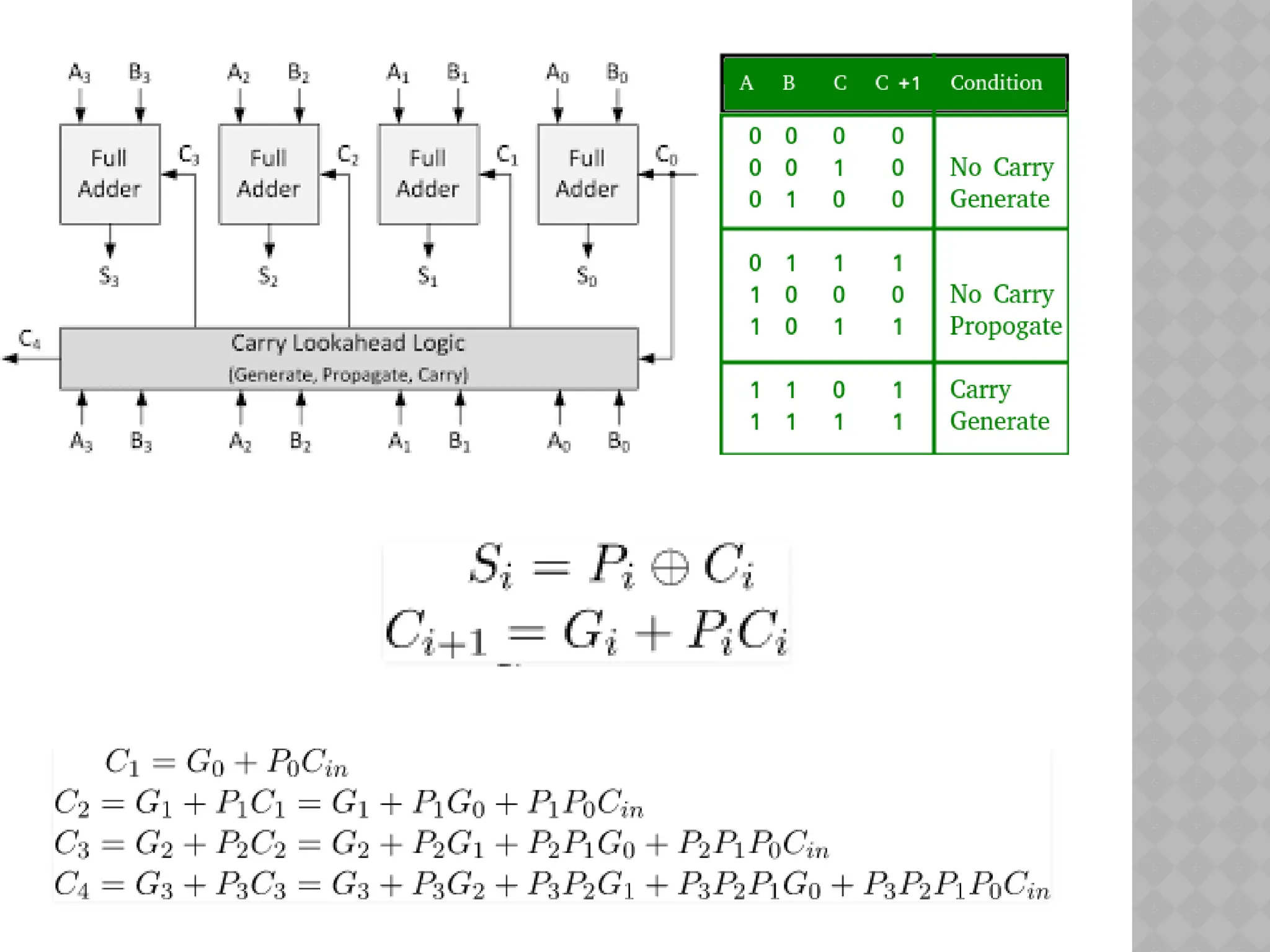

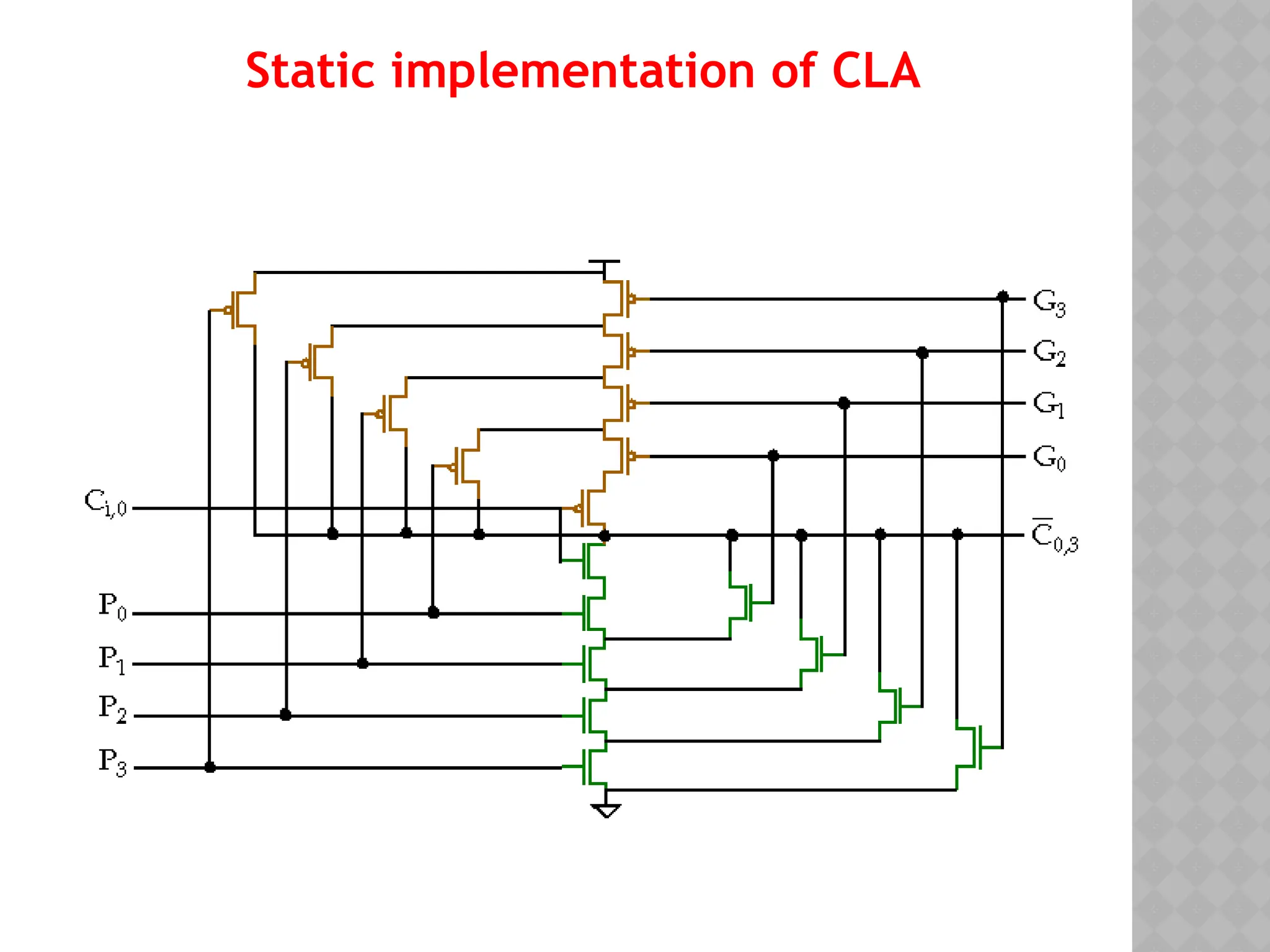

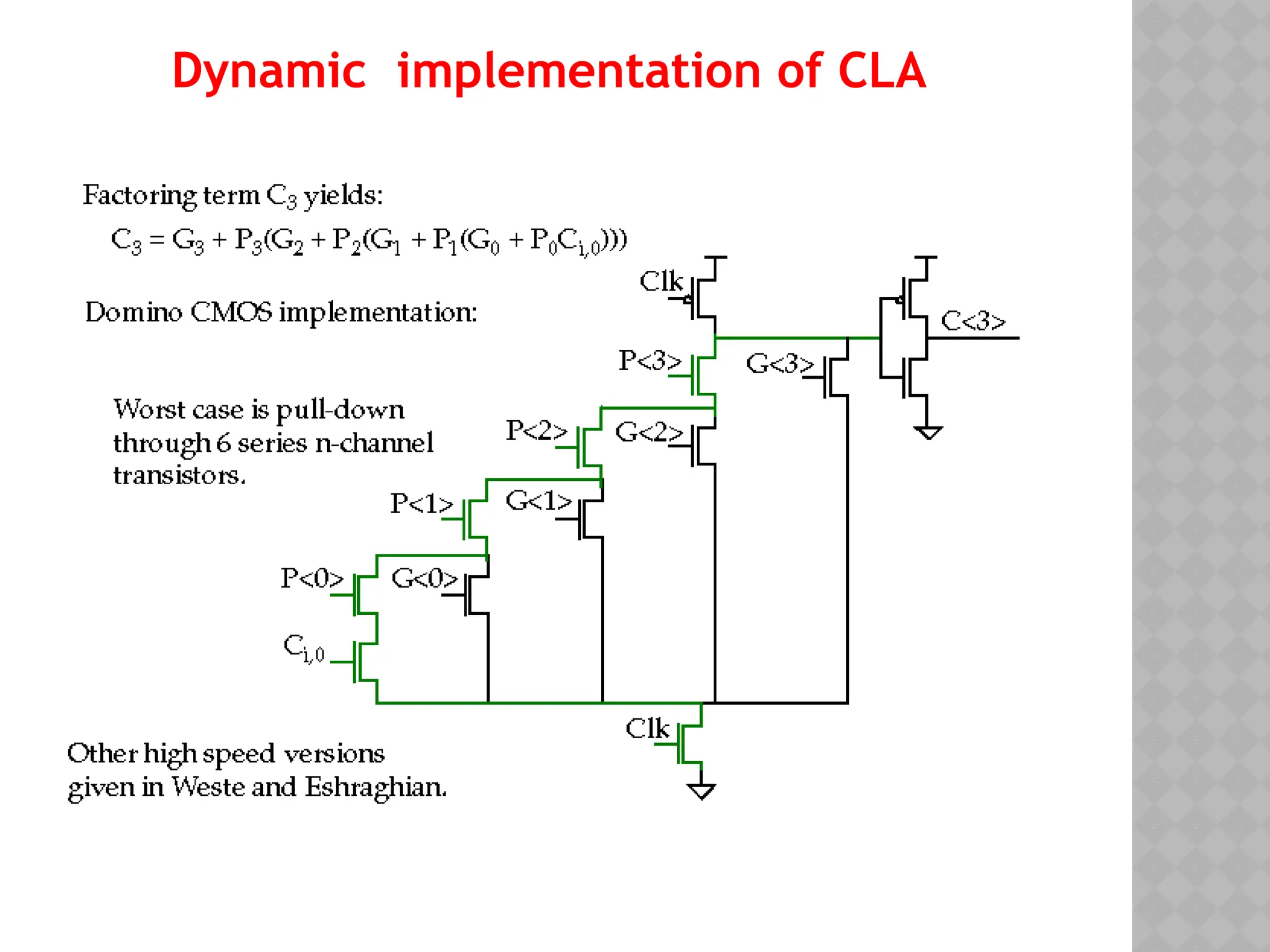

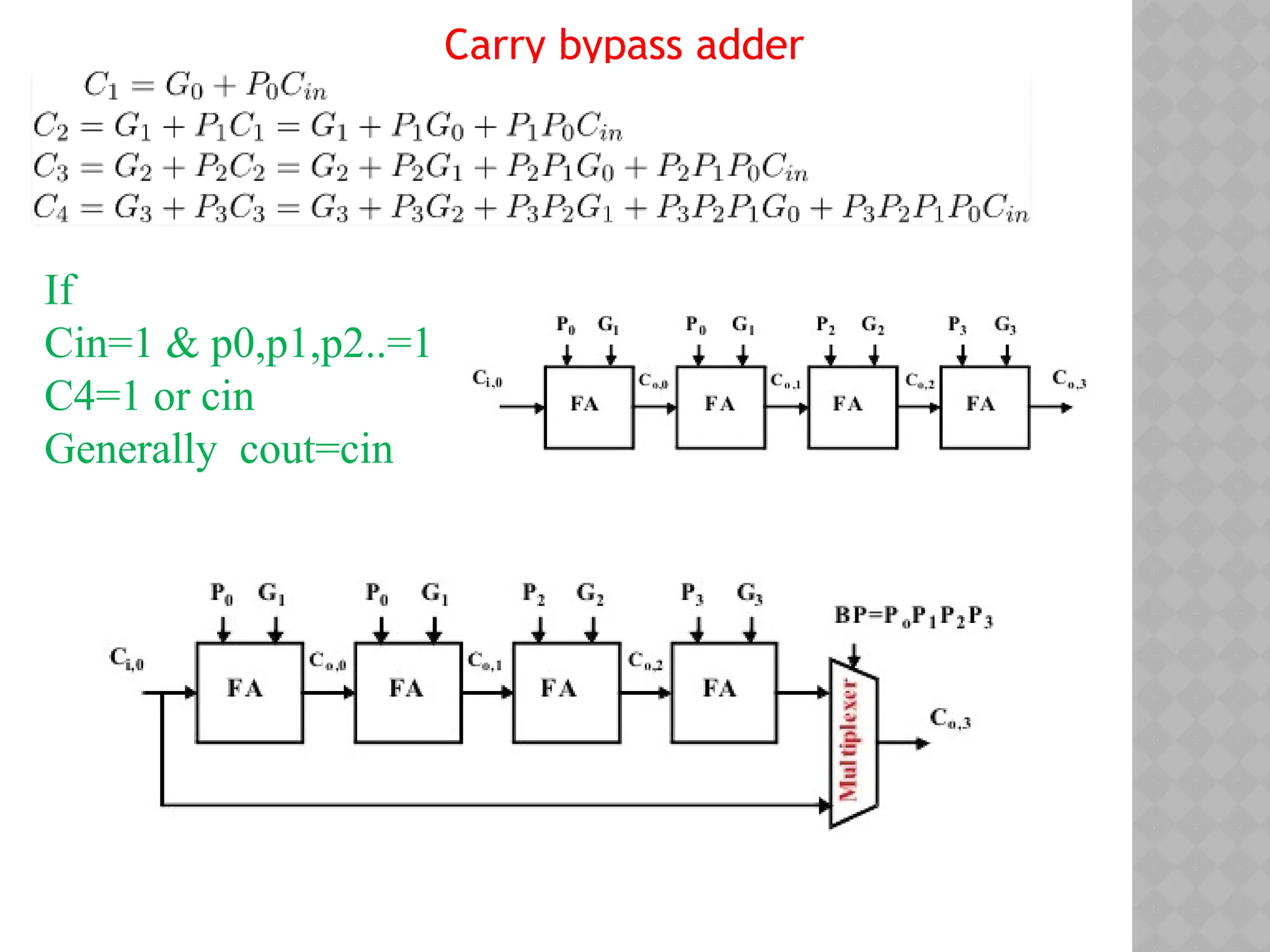

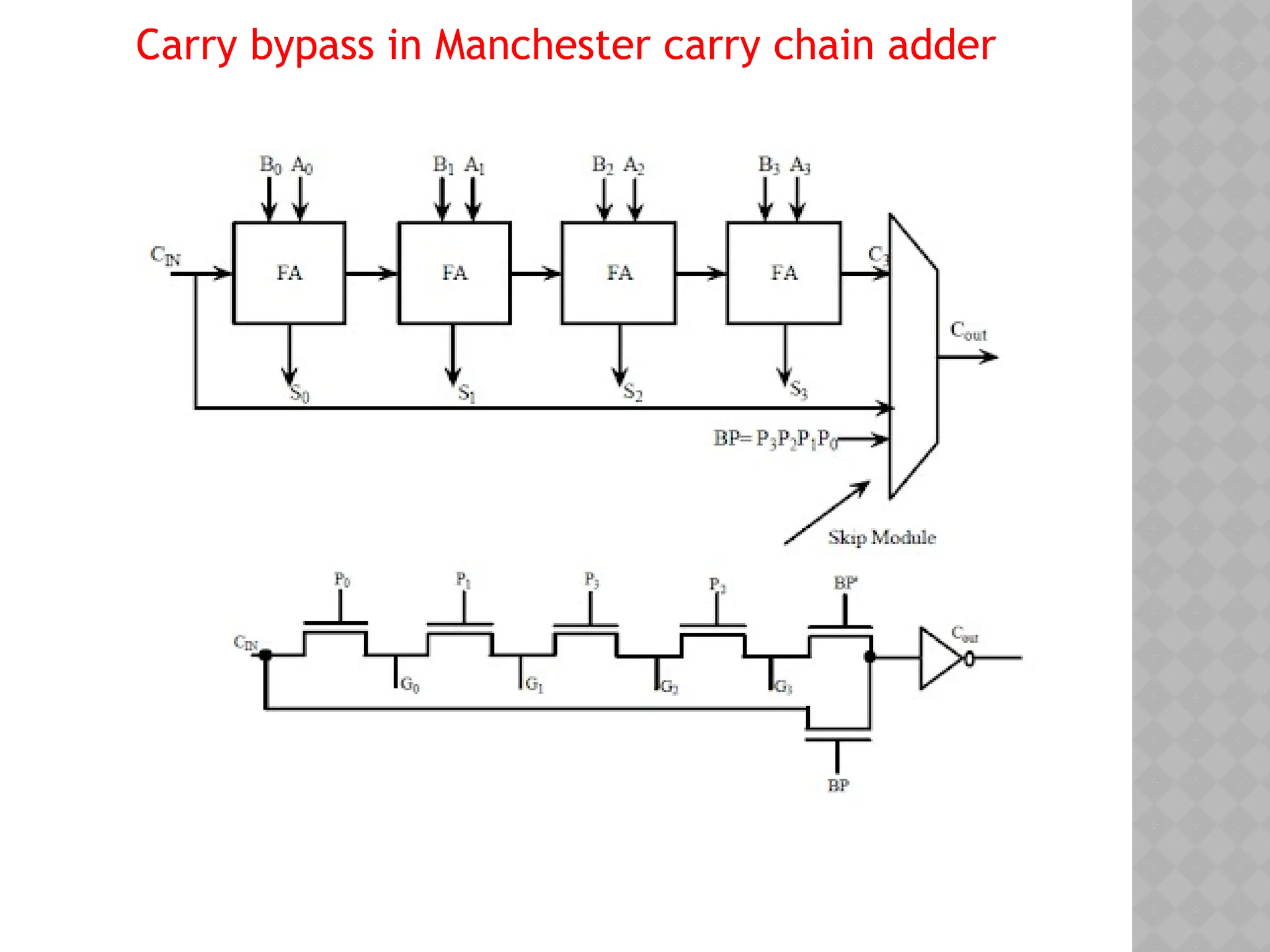

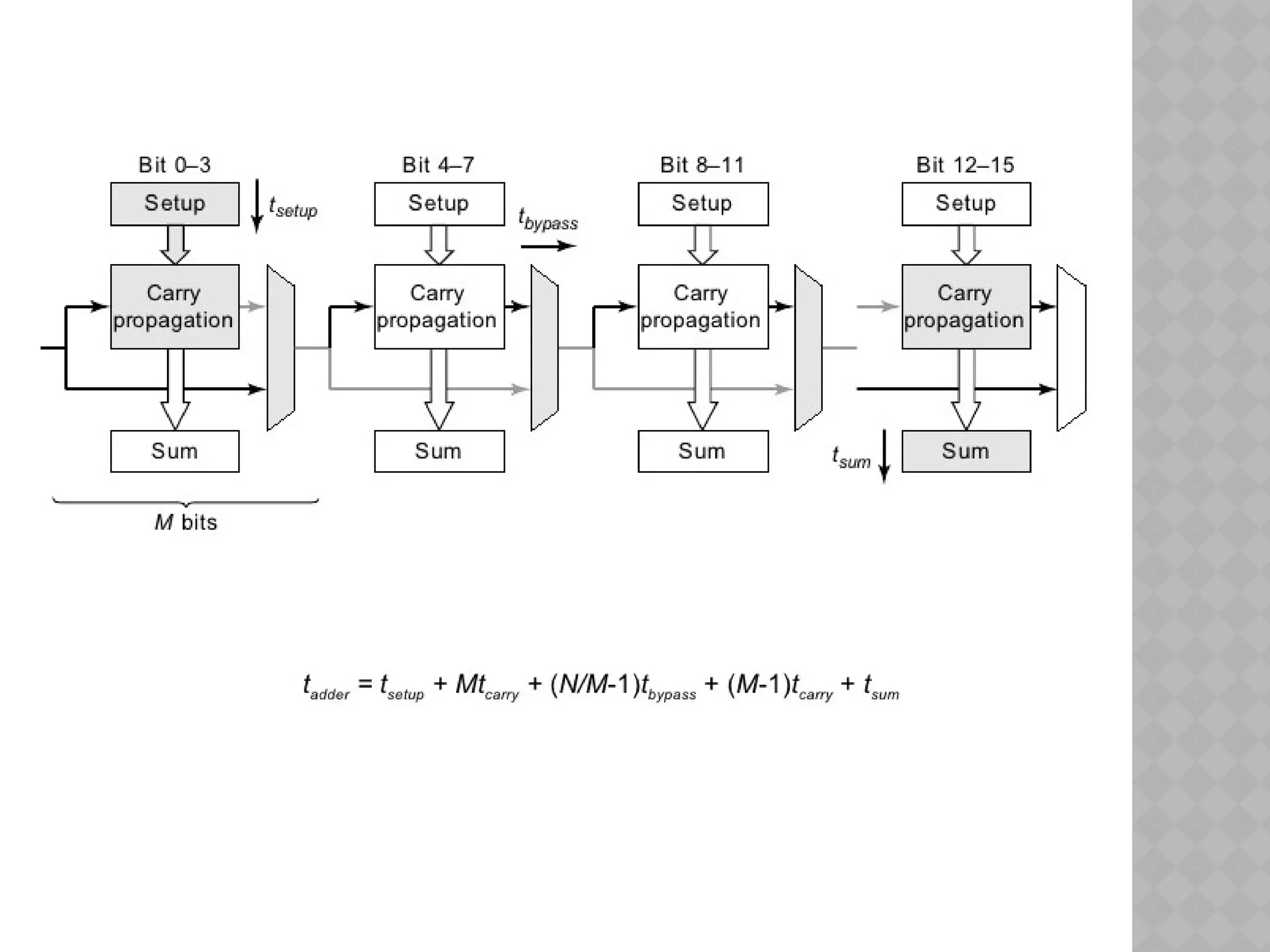

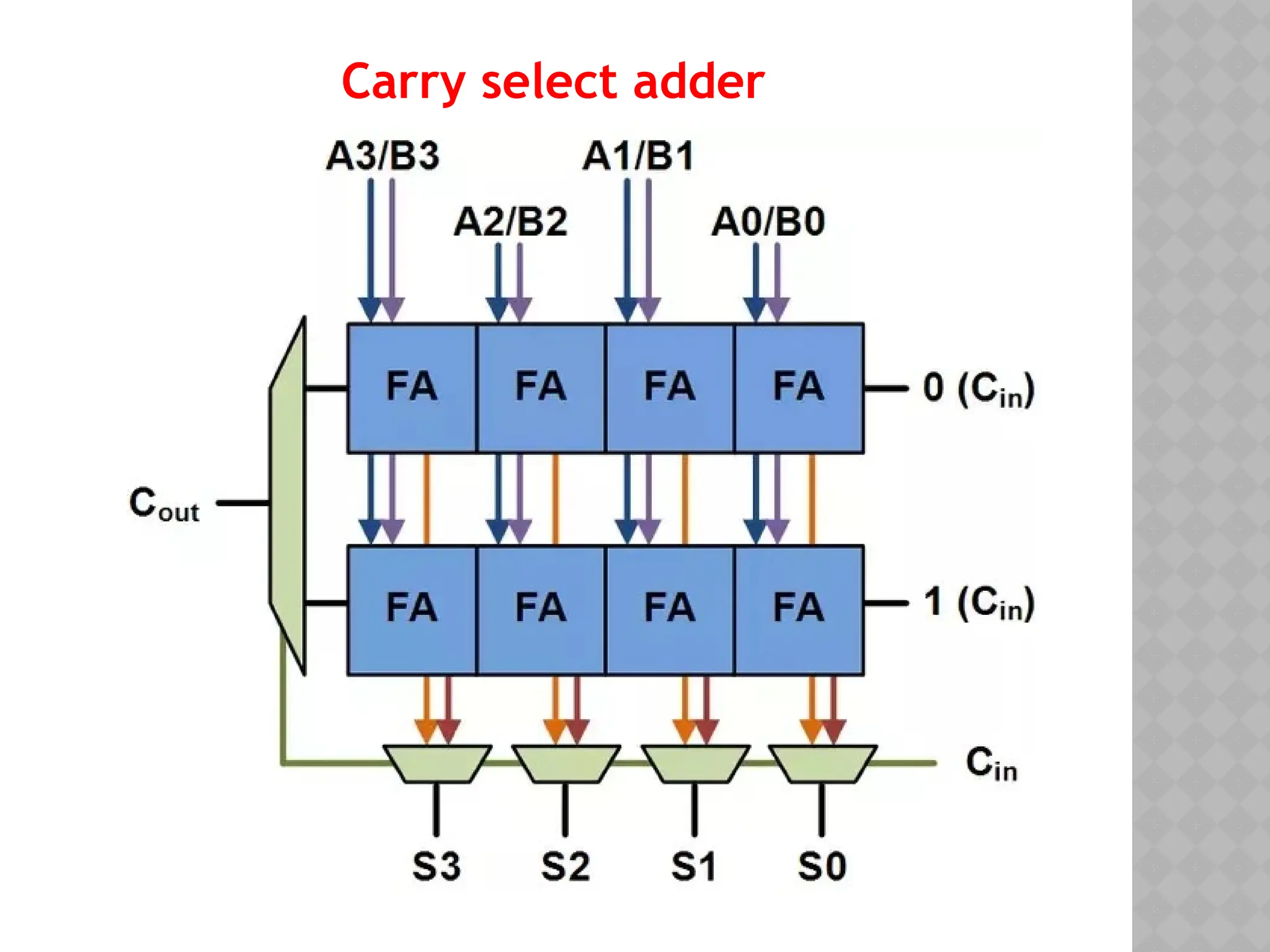

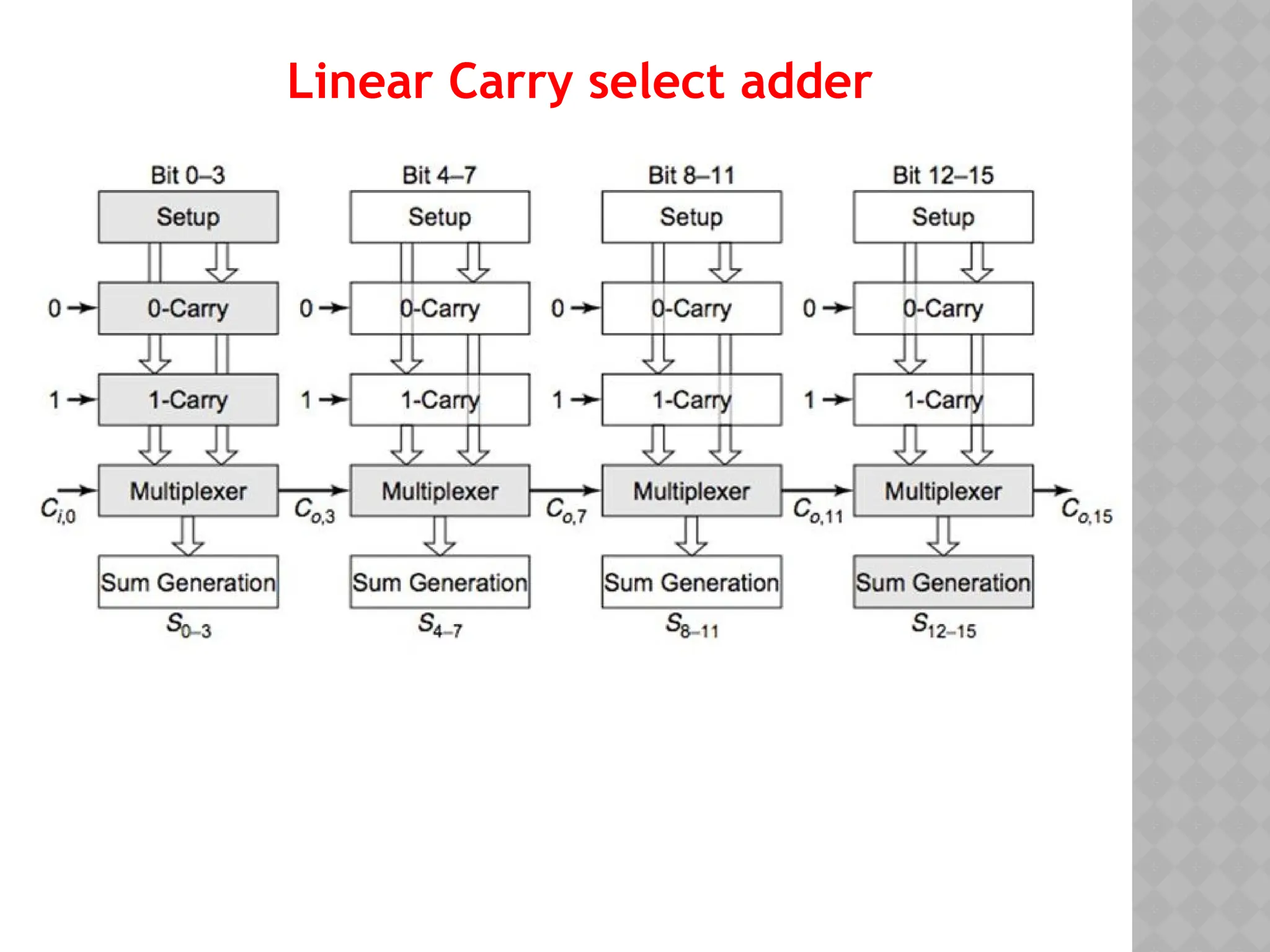

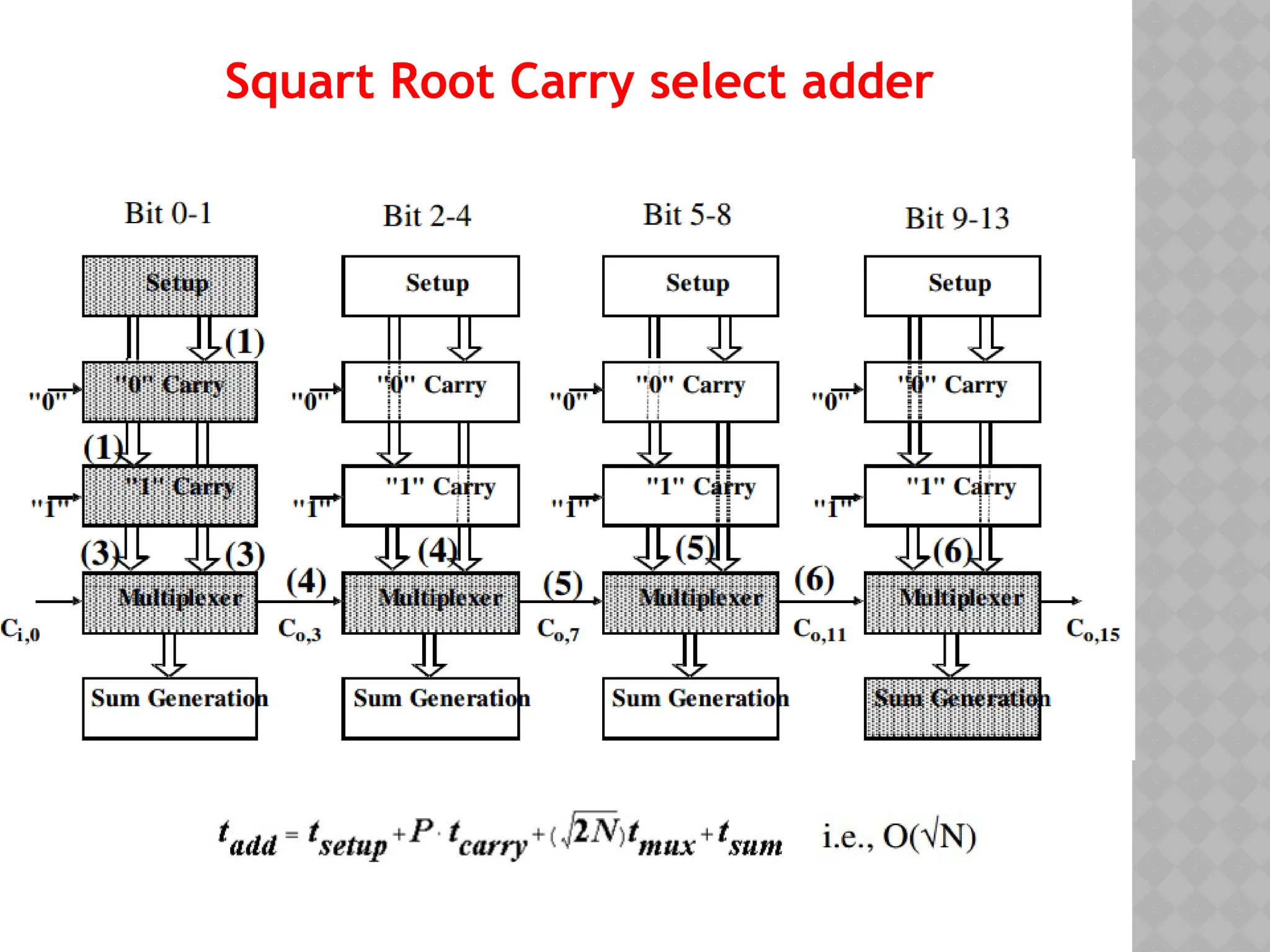

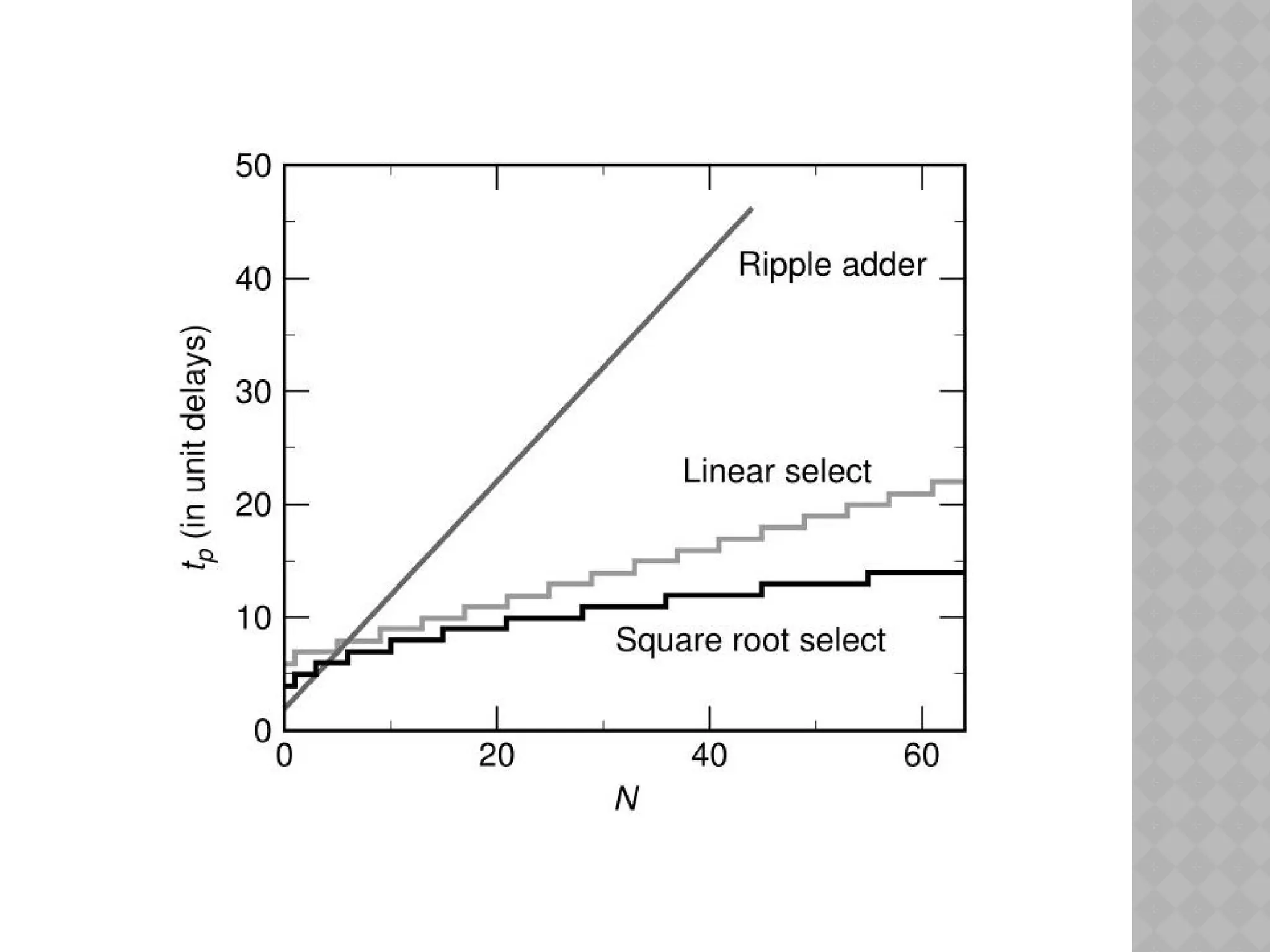

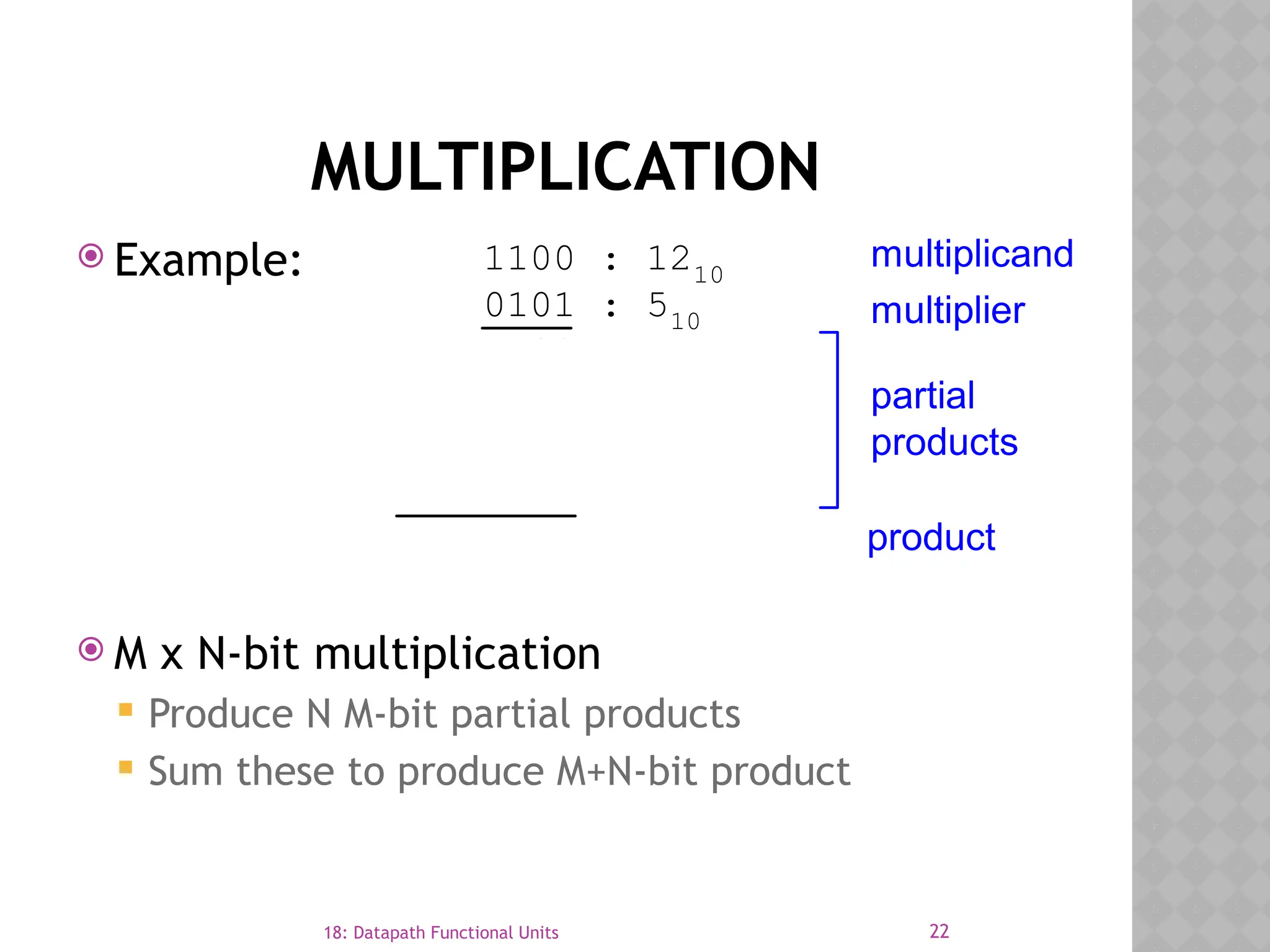

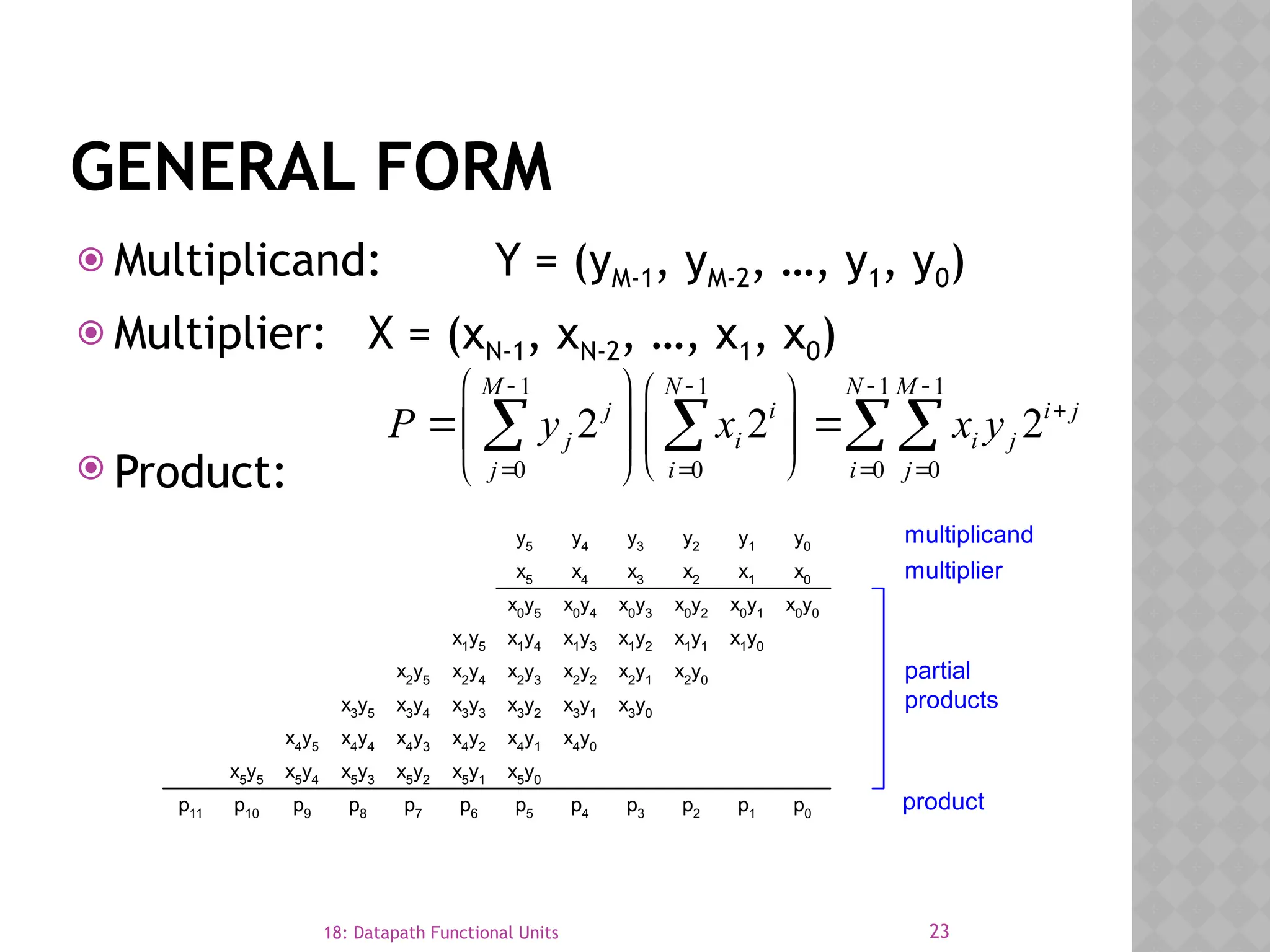

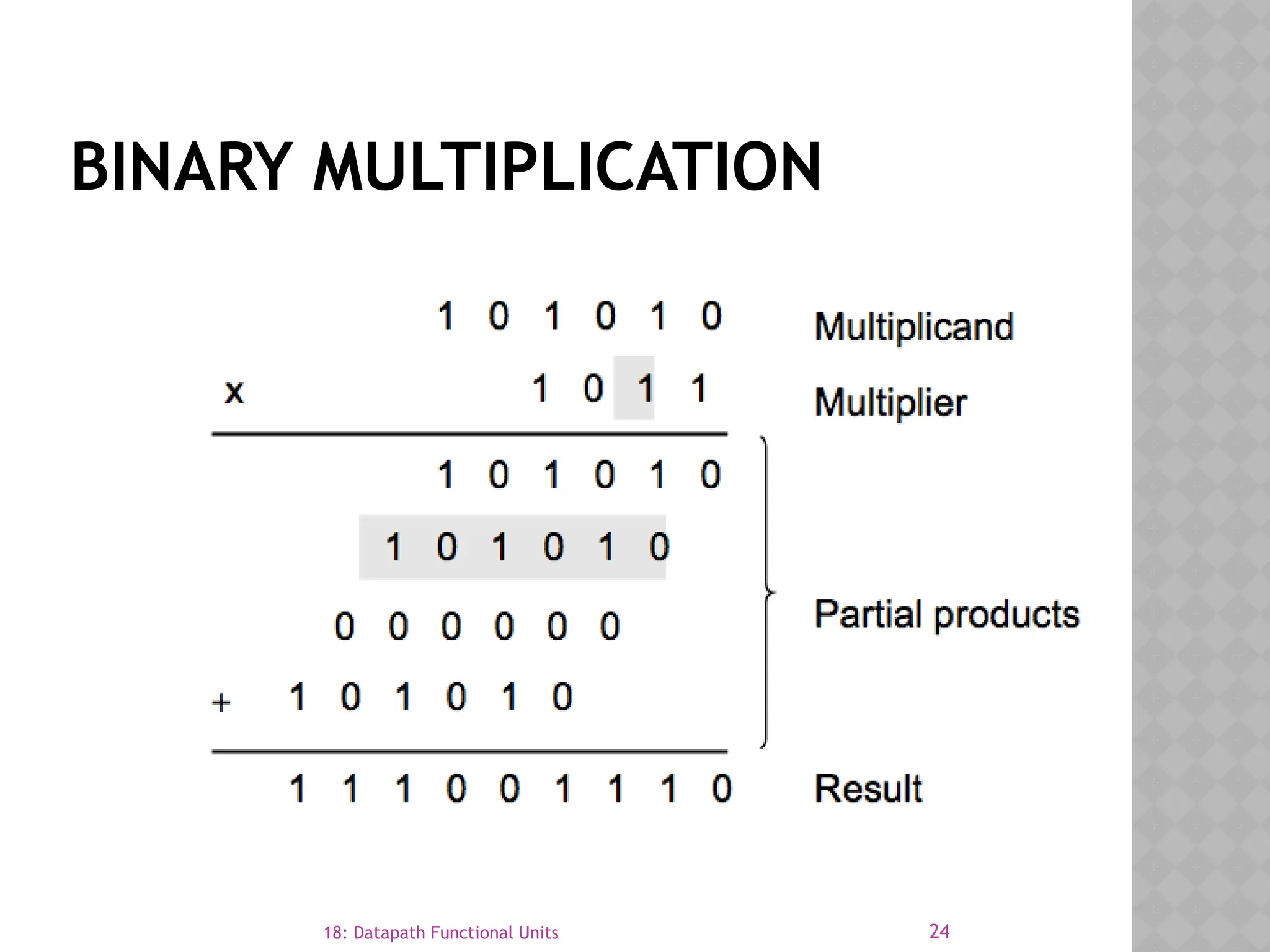

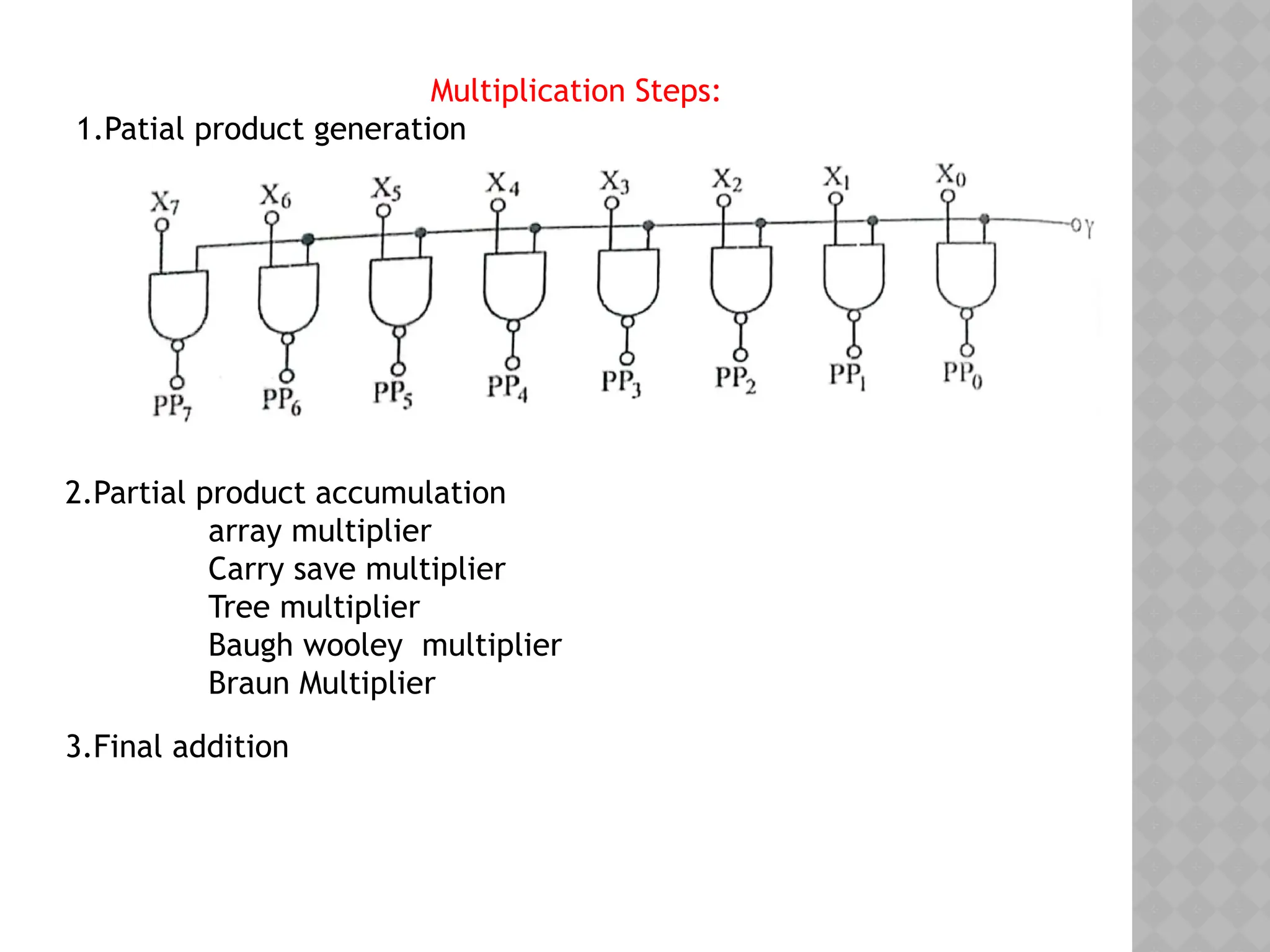

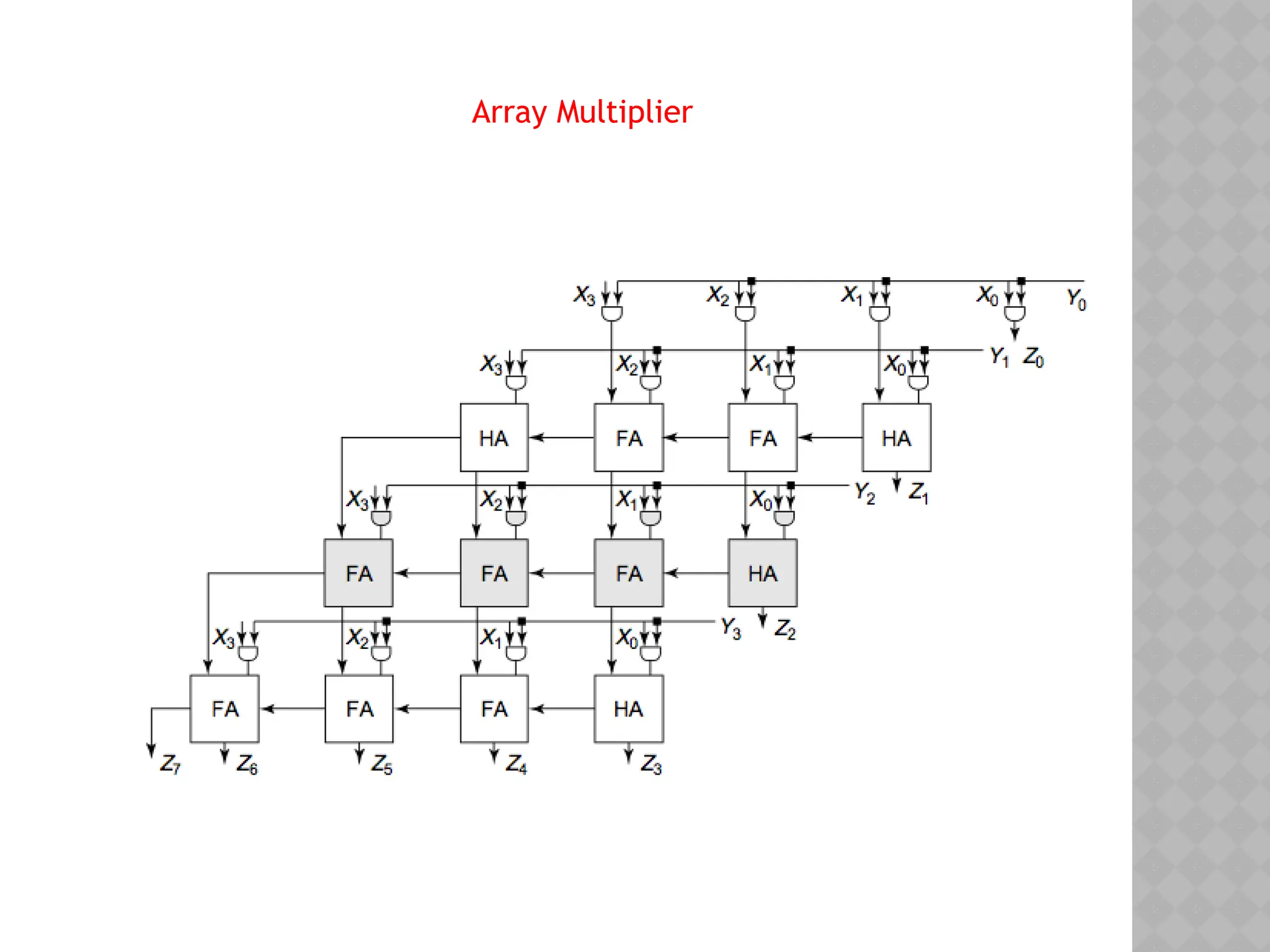

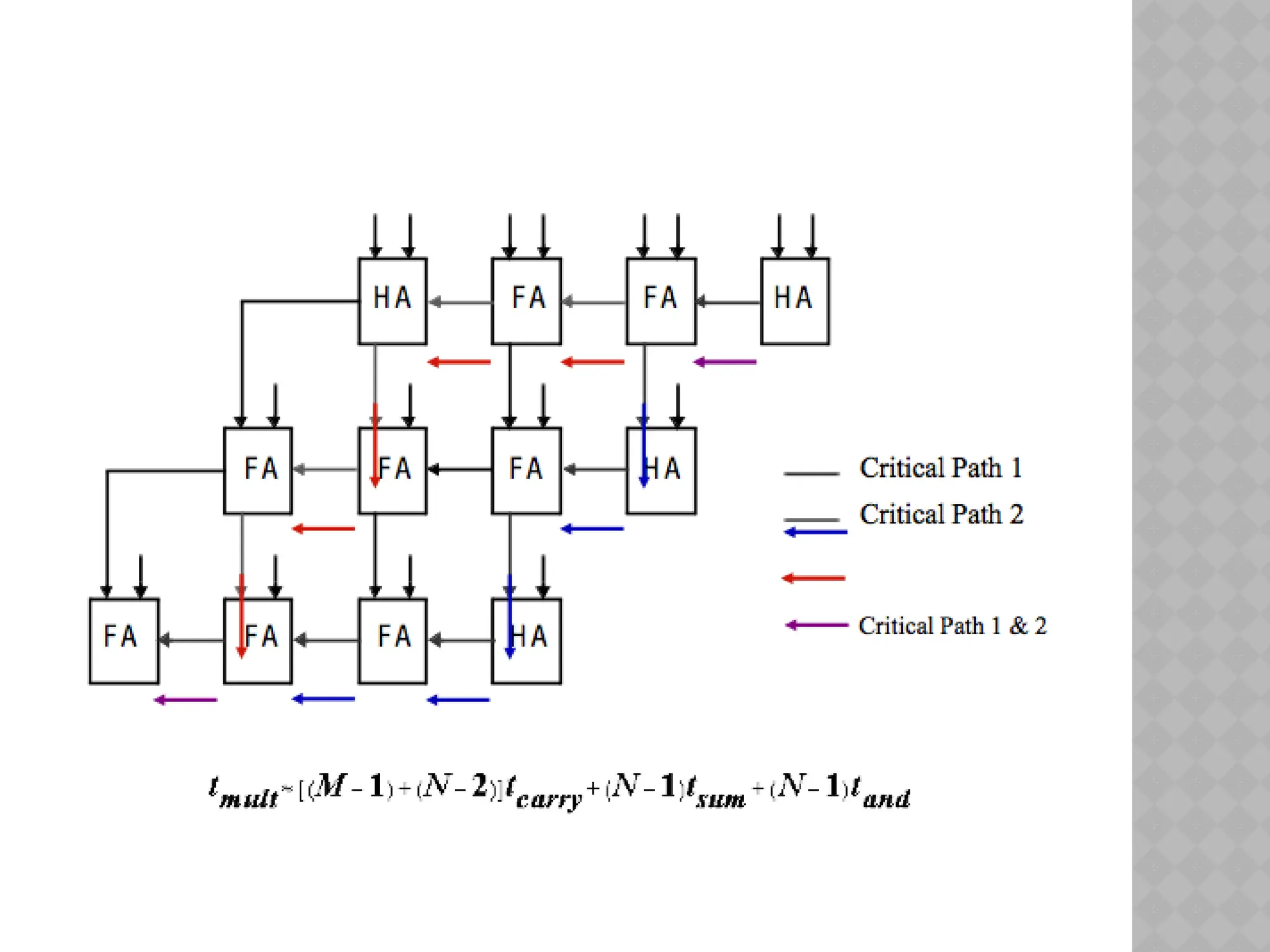

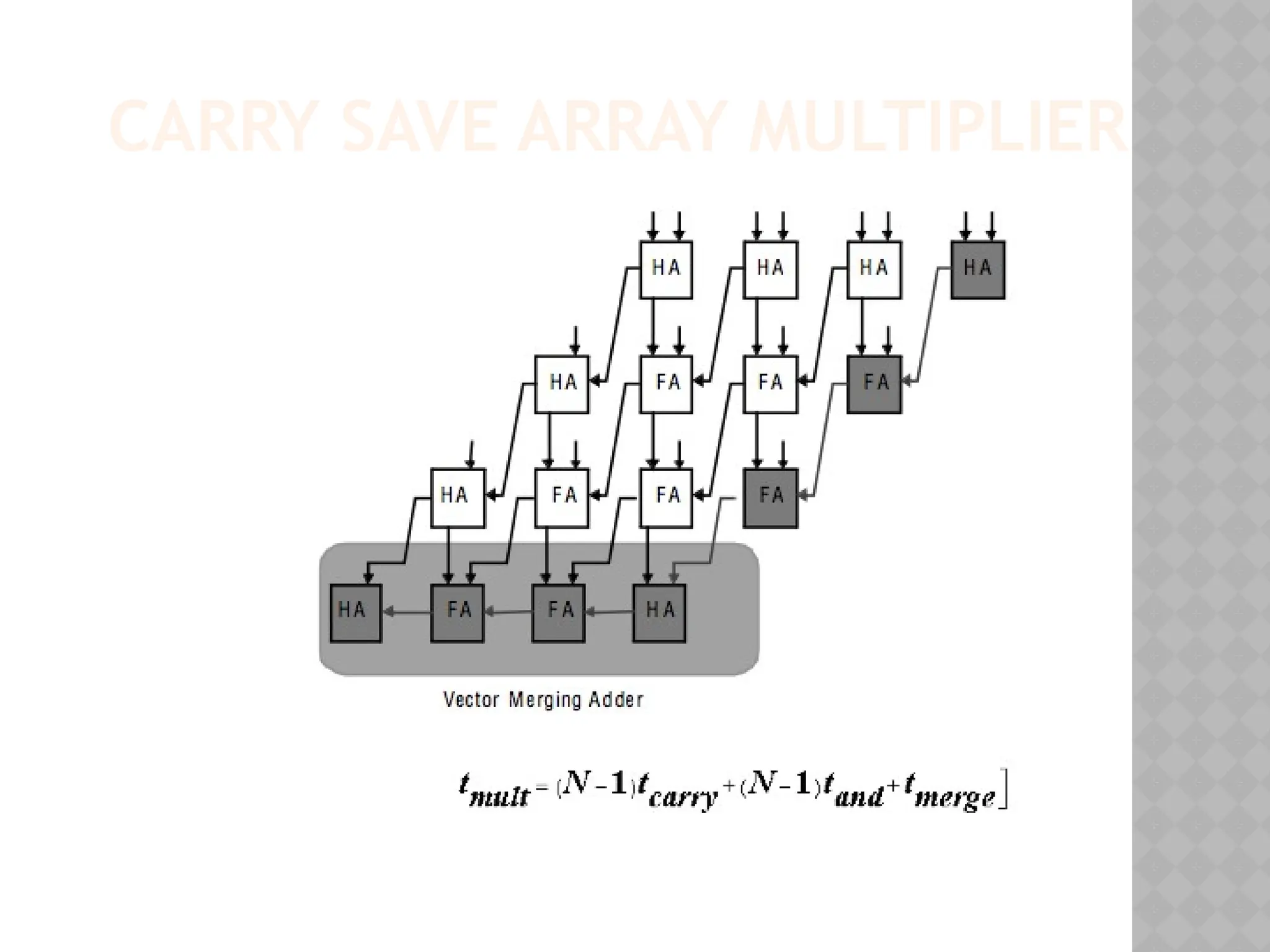

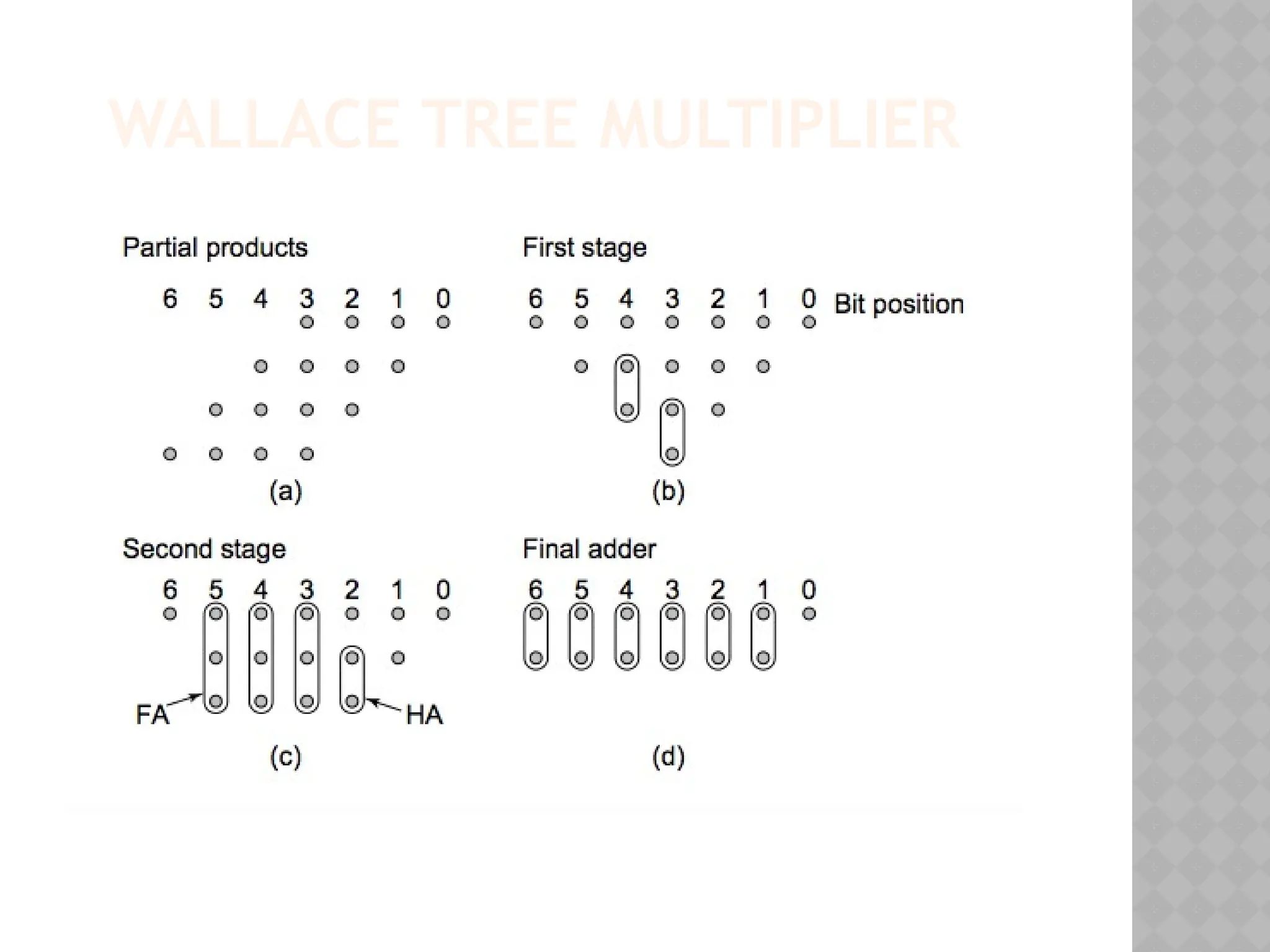

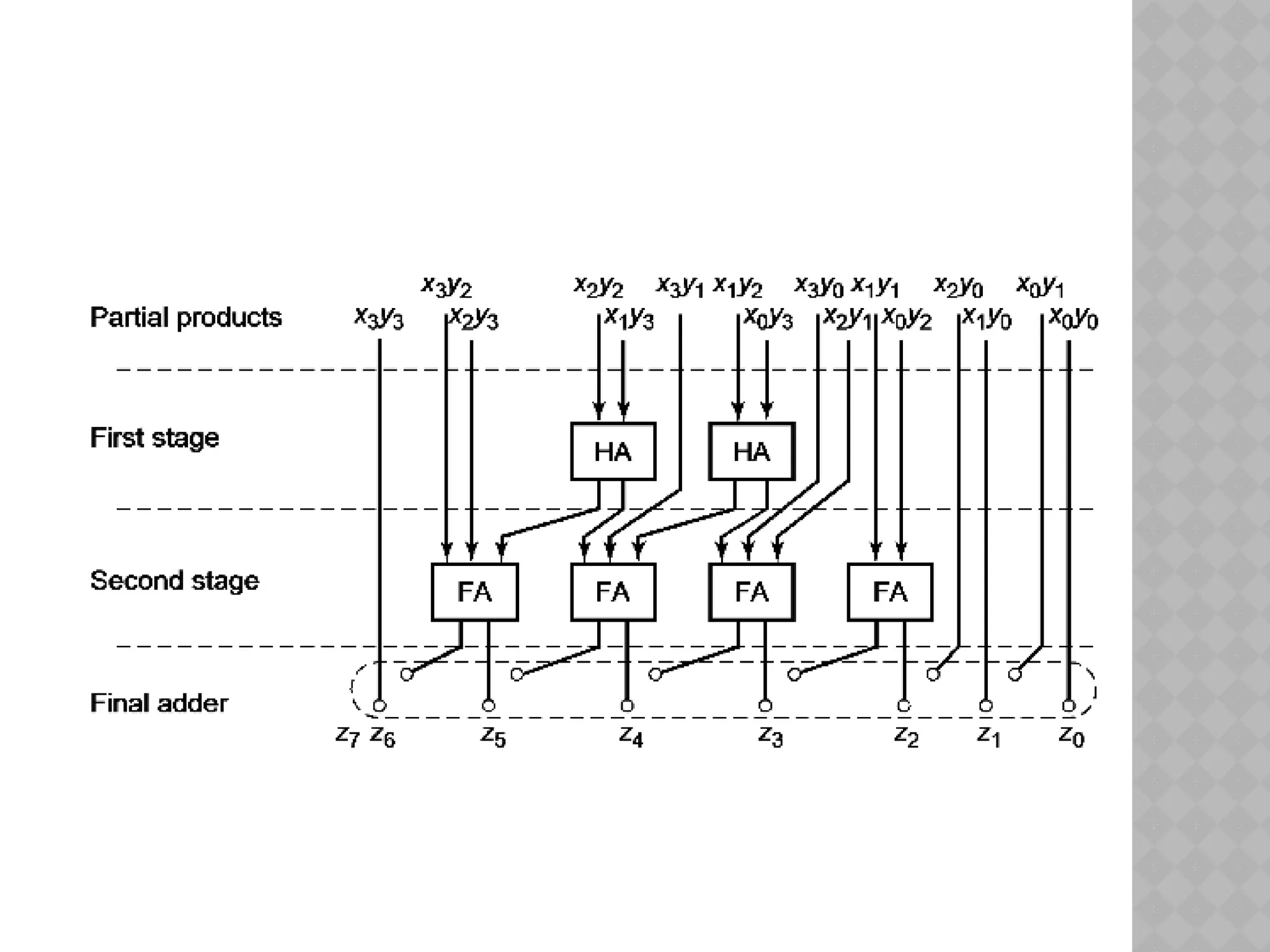

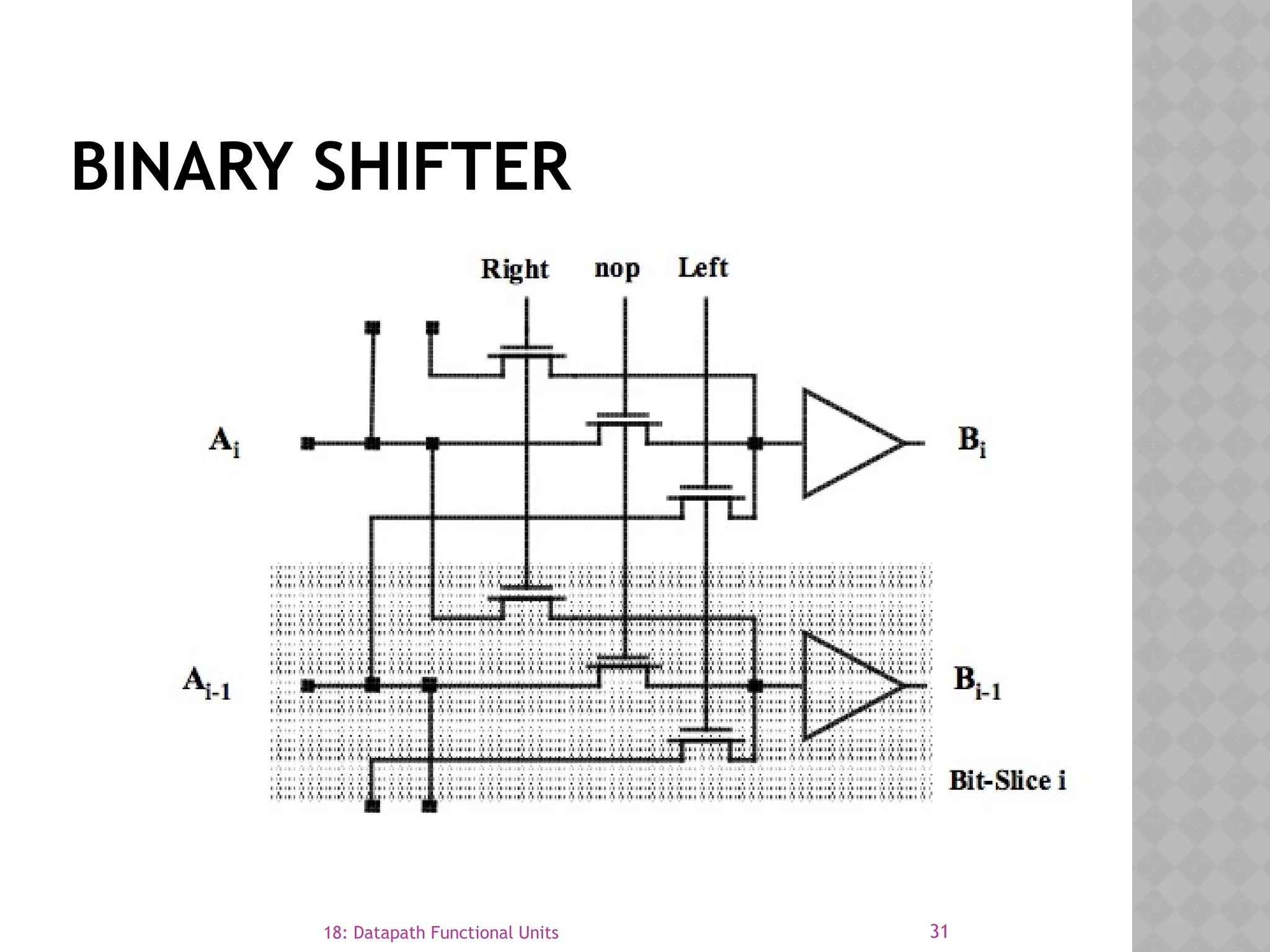

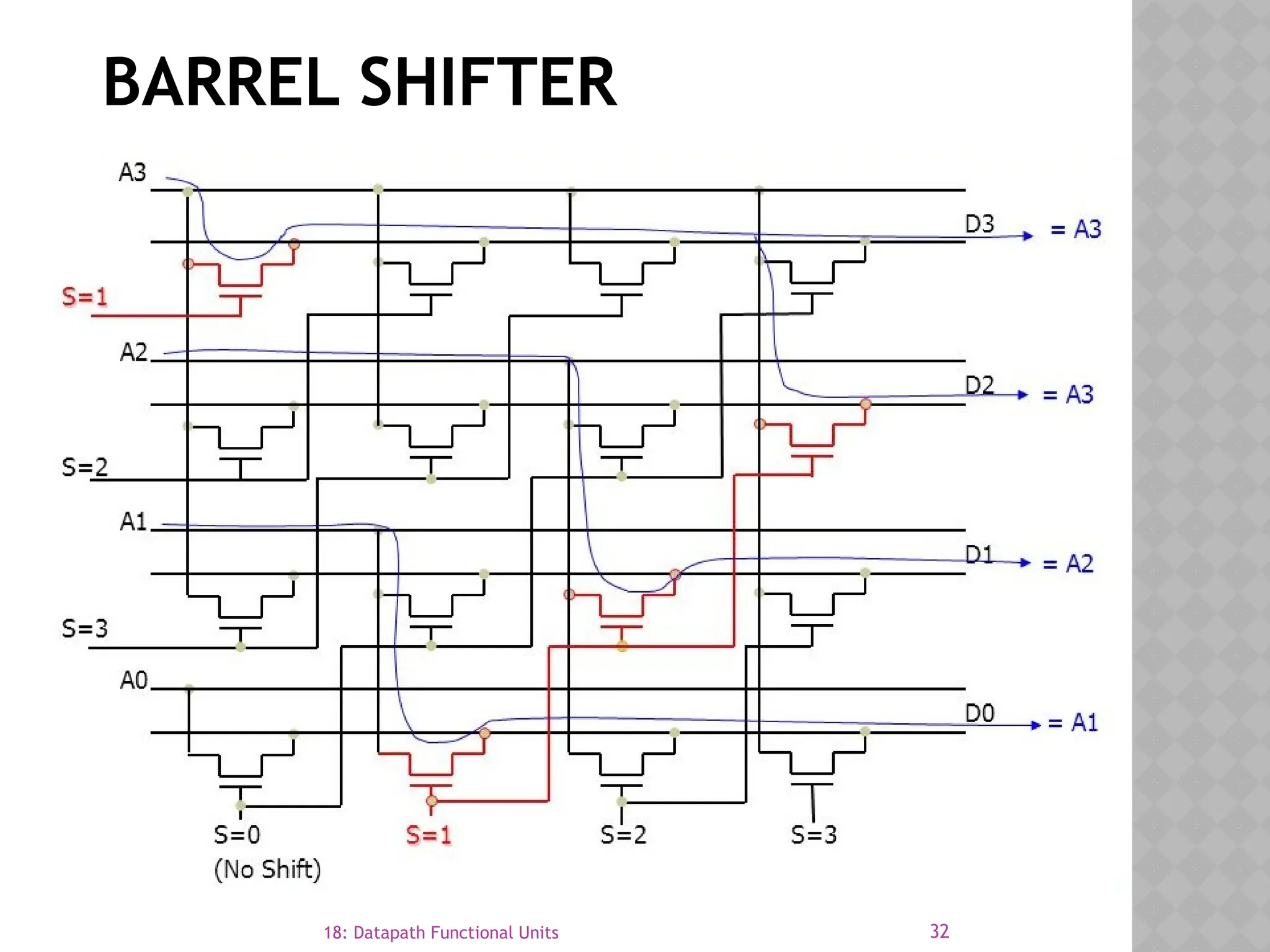

The document focuses on the design of arithmetic building blocks and subsystems, detailing elements such as adders (static and dynamic), multipliers, and shifters. It discusses optimization techniques for achieving faster circuits and describes various types of multipliers and their functioning. Additionally, it covers functional units in data paths, including binary multiplication and architectures for efficient computation.